# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

# Implementation of Adder by Using Quantum-Dot Cellular Automata Technology

T Ranjitha devi

Assistant Professor, Dept. of ECE, SVIT Engg College, ATP, India

ABSTRACT: In this paper, a novel quantum-dot cellular automata (QCA) adder design is presented that decrease the number of QCA cells compared to previously report designs. The proposed one-bit QCA adder design is based on a new algorithm that requires only three majority gates and two inverters for the QCA addition. A novel 128-bit adder designed in QCA was implemented. It achieved speed performances higher than all the existing. QCA adders, with an area requirement comparable with the cheap RCA and CFA established. The novel adder operates in the RCA fashion, but it could propagate a carry signal through a number of cascaded MGs significantly lower than conventional RCA adders. In adding together, because of the adopted basic logic and layout strategy, the number of clock cycles required for completing the explanation was limited. As transistors reduce in size more and more of them can be accommodated in a single die, thus increasing chip computational capabilities. However, transistors cannot find much smaller than their current size. The quantum-dot cellular automata approach represents one of the possible solutions in overcome this physical limit, even though the design of logic modules in QCA is not forever straightforward.

**KEYWORDS:** Adders, nano-computing, QCA (quantum-dot cellular automata)

### I. INTRODUCTION

In this paper, a new QCA adder design is implemented that reduces the number of QCA cells when compared to existing reported designs. We demonstrate that it is possible to design a CLA QCA one-bit adder, with the same reduced hardware as the bit-serial adder, as retaining the simpler clocking scheme and parallel structure of the novel CLA approach. The proposed design is based on a new algorithm that requires only three majority gates and two inverters for the QCA addition. It is noted that the bit-serial QCA adder uses a variant of the proposed one-bit QCA adder. By connect *n* proposed one-bit QCA adders.

A quantum-dot cellular automaton (QCA) is an attractive emerging technology suitable for the development of ultra dense low-power higher-performance digital circuits. For this cause in the last few years, the design of proficient logic circuits in QCA has received a great deal of attention. Special efforts are directed to arithmetic circuits, with the major interest focused on the binary addition that is the basic operation of any digital system. Of course, the designs commonly employed in traditional CMOS designs are considered a first reference for the new design environment. Ripple-carry, carry look-ahead (CLA), and conditional sum adders were implemented in. The carry-flow adder shown in was mainly an improved RCA in which detrimental wires effects were mitigated. Parallel-prefix architectures, including Brent–Kung (BKA), Kogge–Stone, Ladner–Fischer, and Han–Carlson adders, were analyzed and implemented in QCA. Recently, further efficient designs were proposed for the CLA and the BKA, and for the CLA and the CFA. In this brief, an innovative technique is presented to implement high-speed low-area adders into QCA. Theoretical formulations established for CLA and parallel-prefix adders are here exploited for the realization of a novel 2-bit addition slice. The latter allows the carry to be propagated through two subsequent bit-positions with the delay of just one majority gate (MG). In addition, the clever top level architecture leads to very compact layouts, thus avoiding unnecessary clock phases due to lengthy interconnections.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 3, March 2015

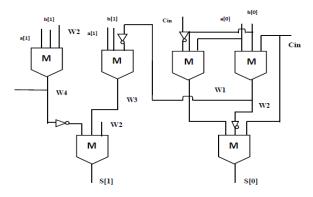

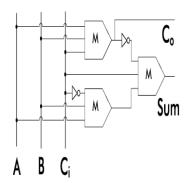

Fig 1 Novel 2-bit basic module

An adder designed as proposed runs in the RCA fashion, but it exhibit a computational delay lower than all state-oftheart competitors and achieves the lowest area-delay product (ADP).

#### II. BACK GROUND

#### A. QCA Basics

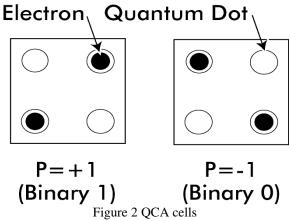

QCA is based on the interface of bi-stable QCA cells constructed from four quantum-dots. A high-level design of two polarized QCA cells is shown in Fig. 2. Each cell is constructed from four quantum dots arranged in a square pattern. The cell is charged with two electrons, which are free of charge to tunnel between adjacent dots. These electrons tend to take up antipodal sites as a result of their mutual electrostatic repulsion. Thus, there exist two equal energetically minimal arrangements of the two electrons in the QCA cell as shown in Fig. 2. These two arrangements are denoted as cell polarization P = +1 and P = -1 correspondingly. By using cell polarization P = +1 to represent logic "1" and P = -1 to represent logic "0", binary information can be encoded.

Arrays of QCA cells can be set to perform all logic functions. This is owed to the Columbic interactions, which influences the polarization of neighboring cells. QCA designs have been proposed with potential barriers between the dots that can be controlled and used to clock QCA designs.

#### B. QCA Logical Devices

The fundamental QCA logic devices are the QCA wire, majority gate and inverter.

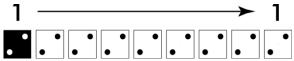

QCA wire: In a QCA wire, the binary signal propagates from input to output because of the Columbic connections between cells. This is a result of the system attempting to settle to a ground state. Any cells along the wire that are antipolarized to the input would be at a high energy level, and would soon settle to the correct ground state. The propagation in a 90-degree QCA wire is shown in Fig. 4. Other than the 90- degree QCA wire, a 45-dgree QCA wire

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

can also be used. In this case, the propagation of the binary signal alternates between the two polarizations. Advance, there exists a so-called non-linear QCA wire, in which cells with 90-degree orientation can be placed next to one more, but off center.

Figure 3 A QCA wire (90-degree)

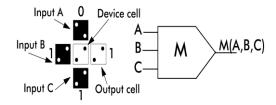

**Majority gate and inverter**: The majority gate and inverter are shown in Fig. 4 and Fig. 5 respectively. The majority gate performs a three-input logic function. Assuming the inputs are A, B and C, the logic function of the majority gate is

m(A, B, C) = A|B + B|C + A|C(1)

By fixing the polarization of one input as logic "1" or "0", we can get an OR gate and an AND gate respectively. More complex logic circuits can then be designed from OR and AND gates.

Figure 4 A QCA majority gate

Figure 5 A QCA inverter

### C. QCA Full Adders

Figure 6 one-bit QCA full adder

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

#### III. PROPOSED METHOD

A QCA is a nano-structure having as its basic cell a square four quantum dots structure charged with two free electrons able to tunnel through the dots inside the cell. Because of Coulombic repulsion, the two electrons will forever reside in opposite corners. The locations of the electrons in the cell determine two possible stable states that can be associated to the binary state 1 and 0.

Although adjacent cells interact through electrostatic forces and tend to arrange in a line their polarizations, QCA cells do not have intrinsic data flow directionality. To achieve controllable data directions, the cells inside a QCA design are partitioned into the so-called clock zones that are progressively associated to four clock signals, each phase shifted by  $90^{\circ}$ . This clock system named the zone clocking scheme, makes the QCA designs intrinsically pipelined, as each clock zone behaves like a D-latch. QCA cells are used for both logic designs and interconnections that can exploit either the coplanar cross or bridge technique. The fundamental logic gates inherently available within the QCA technology are the inverter and the MG. Given three inputs a, b, and c, the MG perform the logic function reported in (1) provided that all input cells are associated to the same clock signal clkx (with x ranging from 0 to 3), whereas the remaining cells of the MG are linked to the clock signal clkx+1

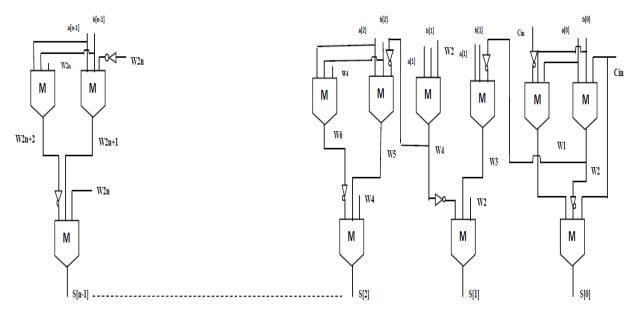

Fig 2 Novel *n*-bit adder

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 3, March 2015

Several designs of adders in QCA exist in literature. The RCA [11], [13] and the CFA [12] process *n*-bit operands by cascading *n* full-adders (FAs). Even although these addition circuits use different topologies of the generic FA, they include a carry-in to carry-out path consisting of one MG, and a carry-in to sum bit path contain two MGs plus one inverter. As a importance, the worst case computational paths of the *n*-bit RCA and the *n*-bit CFA consist of (*n*+2) MGs and one inverter. A CLA design formed by 4-bit slices was also presented. In particular, the auxiliary propagate and generate signals, namely

$p_i = a_i + b_i$  and  $g_i = a_i \cdot b_i$ , are compute for each bit of the operands and then they are grouped four by four. Such a designed *n*-bit CLA has a computational path composed of  $7+4\times(\log_4 n)$  cascade MGs and one inverter. This can be easily verified by observing that, given propagate and generate signals, to compute grouped propagate and grouped generate signals; four cascade MGs are introduced in the computational path. In addition, to calculate the carry signals, one level of the CLA logic is required for each factor of four in the operands word-length. This means that process *n* bit addends,  $\log_4 n$  levels of CLA logic are required, every contributing to the computational path with four cascaded MGs. Finally, the calculation of sum bits introduces two further cascaded MGs and one inverter. The parallel-prefix BKA demonstrated exploits more efficient basic CLA logic designs. As its main

Novel 16-bit adder

advantage over the previously describe adders, the BKA can achieve lower computational delay. When n-bit operands are processed, its bad case computational path consists of  $4 \times \log_2 n - 3$  cascaded MGs and one inverter. Apart from the level required to compute propagate and generate signals, the prefix tree consists of  $2 \times \log_2 n - 2$  stages. From the logic equations provided, it can be easily verified that the first stage of the tree introduces in the computational path just one MG; the last stage of the tree contributes with only one MG; while, the intermediate stages introduce in the critical path two cascaded MGs all. Finally, for the computation of the sum bits, further two cascaded MGs and one inverter are added. With the main objective of trading off area and delay, the hybrid adder (HYBA) described combines a parallel prefix adder through the RCA. In the presence of n-bit operands, this architecture has a worst computational path consisting of  $2 \times \log_2 n + 2$  cascade MGs and one inverter. When the methodology in recent times proposed was exploited, the worst case path of the CLA is reduced to  $4 \times [\log_4 n] + 2 \times [\log_4 n] - 1$  MGs and one inverter. The above-mentioned approach can be applied also to design the BKA. In this case the overall area is reduced with respect to, but maintaining the same computational path. By applying the decomposition method demonstrated, the computational paths of the CLA and the CFA are reduced to  $7 + 2 \times \log_4(n/8)$  MGs and one inverter and to (n/2) + 3 MGs and one inverter, respectively.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

### IV. NOVEL QCA ADDER

To introduce the novel design proposed for implementing ripple adders in QCA, let consider two *n*-bit addends  $A = a_{n-1}, \ldots, a_0$  and  $B = b_{n-1}, \ldots, b_0$  and suppose that for the *i* th bit position (with  $i = n - 1, \ldots, 0$ ) the auxiliary propagate and generate signals, namely  $p_i = a_i + b_i$  and

Novel 32-bit adder

Novel 64-bit adder

$g_i = a_i$ .  $b_i$ , are computed  $c_i$  being the carry produced at the generic (i-1)th bit position, the carry signal ci+2, furnished at the (i+1)th bit location, can be computed using the conventional CLA logic reported. The latter can be

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

rewritten as given in (3), by exploiting Theorems 1 and 2 demonstrated. In this way, the RCA action, needed to propagate the carry  $c_i$  through the two subsequent bit locations, requires only one MG. Conversely, conventional circuits operating in the RCA fashion, namely the RCA and the CFA, require two cascaded MGs to perform the same operation. In other words, an RCA adder designed as proposed has a worst case path almost halved with respect to the conventional RCA and CFA. Equation (3) is exploited in the design of the novel 2-bit module shown in Figure. 1 that also shows the computation of the carry  $c_{i+1} = M(p_i g_i c_i)$ . The proposed *n*-bit adder is then implemented by cascading n/2 2-bit modules as shown in Fig. 2(a). Having assumed that the carry-in of the adder is  $c_{in} = 0$ , the signal  $p_0$  is not required and the 2-bit module used at the least significant bit position is simplified.

It must be noted that the time critical addition is performed when a carry is generated at the least significant bit position and then it is propagated through the subsequent bit positions to the most significant one. In this case, the first 2-bit module computes  $c_2$ , causal to the worst case computational path with two cascaded MGs. The subsequent 2-bit modules contribute with only one MG each, thus introducing a total number of cascaded MGs equal to (n-2)/2. Considering that additional two MGs and one inverter are required to compute the sum bits, the worst case path of the novel adder consists of (n/2) + 3 MGs and one inverter.

#### V. RESULTS

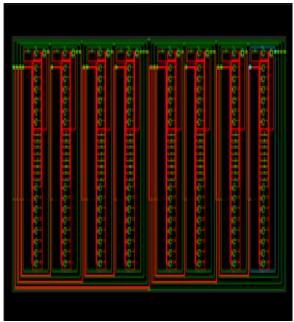

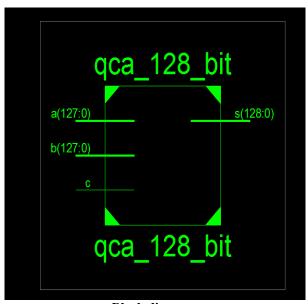

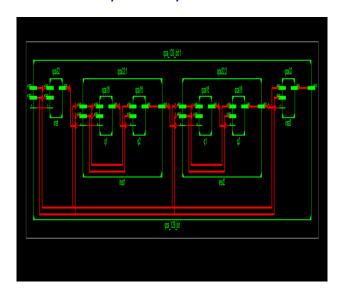

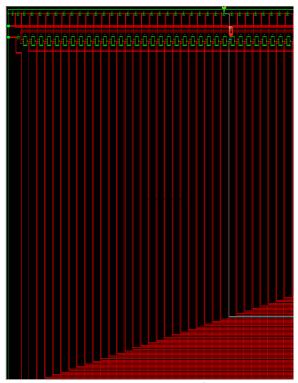

The proposed addition design is implemented for several operands word lengths using the QCA Designer tool adopting the same rules and simulation settings used.

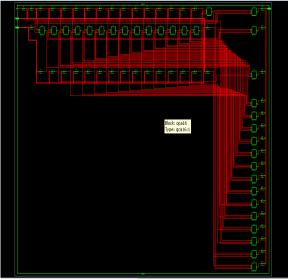

**Block diagram**

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

**RTL** schematic

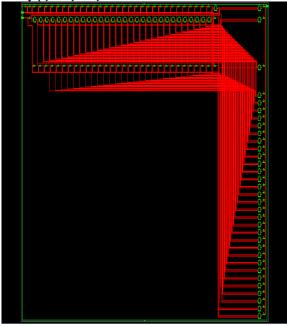

**Technology schematic**

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

| qca_128_bit Project Status |                          |                       |                   |  |

|----------------------------|--------------------------|-----------------------|-------------------|--|

| Project File:              | QCA.xise                 | Parser Errors:        | No Errors         |  |

| Module Name:               | qca_128_bit              | Implementation State: | Synthesized       |  |

| Target Device:             | xc3s50-5pq208            | •Errors:              | No Errors         |  |

| Product Version:           | ISE 14.3                 | •Warnings:            | 1 Warning (O new) |  |

| Design Goal:               | Balanced                 | •Routing Results:     |                   |  |

| Design Strategy:           | Xlinx Default (unlocked) | •Timing Constraints:  |                   |  |

| Environment:               | System Settings          | •Final Timing Score:  |                   |  |

| Device Utilization Summary (estimated values) |      |           |             |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |

| Number of Slices                              | 147  | 768       |             |  |  |

| Number of 4 input LUTs                        | 256  | 1536      |             |  |  |

| Number of bonded IOBs                         | 386  | 124       |             |  |  |

**Design summary**

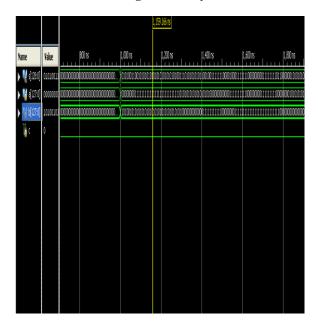

Simulation output

### VI. CONCLUSION

A new adder designed in QCA was implemented. It achieved speed performances high than all the existing QCA adders, with an area requirement comparable with the cheap RCA and CFA demonstrated. The novel adder operated in the RCA fashion, but it could propagate a carry signal through a number of cascaded MGs significantly lesser than conventional RCA adders. In addition, because of the adopted basic logic and layout strategy, the number of clock cycles required for completing the explanation was limited. A 128-bit binary adder designed as described in this brief.

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

#### REFERENCES

- [1] C. S. Lent, P. D. Tougaw, W. Porod, and G. H. Bernestein, "Quantum cellular automata," Nanotechnology, vol. 4, no. 1, pp. 49-57, 1993.

- [2] M. T. Niemer and P. M. Kogge, "Problems in designing with QCAs: Layout = Timing," Int. J. Circuit Theory Appl., vol. 29, no. 1, pp. 49–62, 2001.

- [3] J. Huang and F. Lombardi, Design and Test of Digital Circuits by Quantum-Dot Cellular Automata. Norwood, MA, USA: Artech House, 2007

- [4] W. Liu, L. Lu, M. O'Neill, and E. E. Swartzlander, Jr., "Design rules for quantum-dot cellular automata," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2011, pp. 2361–2364.

- [5] K. Kim, K. Wu, and R. Karri, "Toward designing robust QCA architectures in the presence of sneak noise paths," in *Proc. IEEE Design, Autom. Test Eur. Conf. Exhibit.*, Mar. 2005, pp. 1214–1219.

- [6] K. Kong, Y. Shang, and R. Lu, "An optimized majority logic synthesis methology for quantum-dot cellular automata," *IEEE Trans. Nanotechnol.*, vol. 9, no. 2, pp. 170–183, Mar. 2010.

- [7] K. Walus, G. A. Jullien, and V. S. Dimitrov, "Computer arithmetic structures for quantum cellular automata," in *Proc. Asilomar Conf. Sygnals, Syst. Comput.*, Nov. 2003, pp. 1435–1439.

- [8] J. D. Wood and D. Tougaw, "Matrix multiplication using quantumdot cellular automata to implement conventional microelectronics," *IEEE Trans. Nanotechnol.*, vol. 10, no. 5, pp. 1036–1042, Sep. 2011.

- [9] K. Navi, M. H. Moaiyeri, R. F. Mirzaee, O. Hashemipour, and B. M. Nezhad, "Two new low-power full adders based on majority-not gates," *Microelectron. J.*, vol. 40, pp. 126–130, Jan. 2009.

- [10] L. Lu, W. Liu, M. O'Neill, and E. E. Swartzlander, Jr., "QCA systolic array design," *IEEE Trans. Comput.*, vol. 62, no. 3, pp. 548–560, Mar. 2013.

- [11] H. Cho and E. E. Swartzlander, "Adder design and analyses for quantum-dot cellular automata," *IEEE Trans. Nanotechnol.*, vol. 6, no. 3, pp. 374–383, May 2007.

- [12] H. Cho and E. E. Swartzlander, "Adder and multiplier design in quantum-dot cellular automata," *IEEE Trans. Comput.*, vol. 58, no. 6, pp. 721–727, Jun. 2009.

- [13] V. Pudi and K. Sridharan, "Low complexity design of ripple carry and Brent-Kung adders in QCA," *IEEE Trans. Nanotechnol.*, vol. 11, no. 1, pp. 105–119, Jan. 2012.

- [14] V. Pudi and K. Sridharan, "Efficient design of a hybrid adder in quantumdot cellular automata," *IEEE Trans. Very Large Scale Integr. (VLSI)* Syst., vol. 19, no. 9, pp. 1535–1548, Sep. 2011.

- [15] S. Perri and P. Corsonello, "New methodology for the design of efficient binary addition in QCA," *IEEE Trans. Nanotechnol.*, vol. 11, no. 6, pp. 1192–1200, Nov. 2012.