# International Journal of Advanced Research

in Electrical, Electronics and Instrumentation Engineering

Volume 10, Issue 1, January 2021

Impact Factor: 7.122

|| Volume 10, Issue 1, January 2021 || DOI:10.15662/IJAREEIE.2021.1001012

### A Novel Multilevel Inverter Topology with Reduced Component Count

#### A Yadunanda Kumar<sup>1</sup>, V. Vikram<sup>2</sup>

Assistant professor, Dept. of EEE, Brahmaiah College of Engineering, Nellore, AP, India<sup>1</sup> PG Student [PE], Dept. of EEE, Brahmaiah College of Engineering, Nellore, AP, India<sup>2</sup>

**ABSTRACT**: This paper presents a multilevel inverter that has been conceptualized to reduce component count, particularly for a large number of output levels. It comprises floating input dc sources alternately connected in opposite polarities with one an-other through power switches. Each input dc level appears in the stepped load voltage either individually or in additive combinations with other input levels. This approach results in reduced number of power switches as compared to classical topologies. The working principle of the proposed topology is demonstrated with the help of a single-phase five-level inverter. The topology is investigated through simulations and validated experimentally on a laboratory prototype. An exhaustive comparison of the proposed topology is made against the classical cascaded H-bridge topology

**KEYWORDS**: Classical topologies, multilevel inverter (MLI), pulse width modulation (PWM), reduced component count, total harmonic distortion (THD).

#### **I.INTRODUCTION**

The last few decades, multilevel voltage-source inverters have emerged as a viable solution for high-power dc-to-ac conversion applications [1]. A multilevel inverter (MLI) is a linkage structure of multiple input dc levels (obtained from dc sources and/or capacitors) and power semiconductor devices to synthesize a staircase waveform. Voltage stresses experienced by the power switches are lower as compared to the overall operating voltage level [2]. In addition, the multilevel waveform has a better harmonic profile as compared to a two-level wave-form obtained from conventional inverters. Other advantages of MLIs are reduced *dv/dt* stress on the load and possibility of fault-tolerant operation [3]. Researchers are also exploring avenues to employ MLIs for low-power applications [4].

The quality of the multilevel waveform is enhanced by increasing the number of levels. However, it inadvertently leads to a large number of power semiconductor devices and accompanying gate driver circuits. This increases system complexity and cost and tends to reduce the system reliability and efficiency. For a high-resolution waveform, therefore, practical considerations necessitate reduction in the number of switches and gate driver circuits

The topologies which have been extensively studied and are commercially available for multilevel voltage output are neutral point clamped (NPC), cascaded H-bridge (CHB), and flying capacitor (FC) converters [1], [3], [5]–[7]. However, there is a significant increase in the number of power switches, the number of switches conducting simultaneously,

and the overall cost of the system with the increase in the number of output levels. Researchers, therefore, continue to focus on reducing the component count in multilevel topologies through various approaches. These approaches can be classified into three categories: topological changes [8]–[12], use of asymmetric sources [13]–[15], and combination of topological changes and asymmetric source configurations.

#### II. PROPOSED MULTILEVEL TOPOLOGY

In this section, the structure of the proposed topology is introduced, and its working principle is explained with the help of a single-phase five-level inverter. Expressions for out-put voltage, source currents, voltage stresses, etc.

#### || Volume 10, Issue 1, January 2021 ||

#### DOI:10.15662/IJAREEIE.2021.1001012

Fig. 1 Generalized single-phase structure of the proposed topology.

#### A. Generalized Structure

The generalized single-phase structure of the proposed topology is shown in Fig. 1. It has n number of isolated input dc sources.

The linkage structure is such that the higher potential terminal of the preceding source is connected to the lower potential terminal of the succeeding source and vice versa through power switches. Input sources are designated as Ej (where j = 1 to n). Source current from each source is designated as ij (t). Power switches can be implemented using a transistor device [e.g., MOSFET and insulated-gate bipolar transistor (IGBT)] with an antiparallel diode. In Fig. 1, power switches are illustrated with IGBTs with antiparallel diodes, and

Fig. 2 Single-phase inverter based on the proposed topology with two input sources

complementary pairs are designated as (Tj, T0) (where j = 1 to n + 1). Various nodal voltages are indicated as vj(t) (where j = 1 to n + 1). Load voltage and load current are designated as vL(t) and iL(t), respectively.

#### B. Working Principle

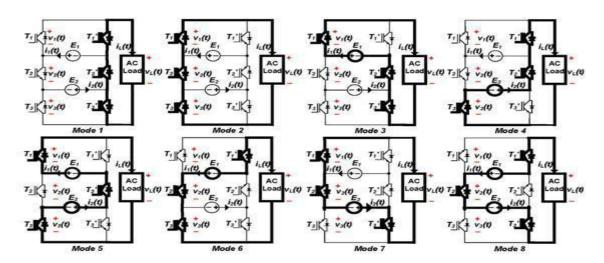

The working principle of the proposed topology is described with the help of a single-phase inverter with two input dc sources E1 and E2, as shown in Fig. 2. It has three pairs of active switches  $(Tj, T^0)$  (j = 1, 2, 3). Since the elements of these pairs are complementary, there are eight valid operating modes. These modes are shown in Fig. 3 and are summarized in Table I along with nodal voltages and source currents. With the use of the operating modes shown in Fig. 3, the load is supplied with five-levels, viz.,  $\pm V dc$ ,

$\pm 2$  Vdc, and zero for E1 = E2 = Vdc. With such a symmetric source configuration, modes 3 and 4 become redundant for output level + Vdc, while modes 6 and 7 become redundant for output level - Vdc. It is important to note here that, for all positive

### || Volume 10, Issue 1, January 2021 || DOI:10.15662/IJAREEIE.2021.1001012

Fig. 3 Valid operating modes for the inverter shown in Fig. 2.

# TABLE I MODES, SWITCHING STATES, NODAL VOLTAGES, AND SOURCE CURRENTS FOR THE PROPOSED TOPOLOGY WITH TWO INPUT SOURCES

| Mode | Switc        | h States |       | Nodal           | Voltage            |                    | Source C             | Current             | Output Voltage  |

|------|--------------|----------|-------|-----------------|--------------------|--------------------|----------------------|---------------------|-----------------|

|      | (1=ON;0=OFF) |          |       |                 |                    |                    |                      |                     | $v_L(t)$        |

|      | $\Gamma_1$   | $T_2$    | $T_5$ | $V_1(t)$        | V <sub>2</sub> (t) | V <sub>5</sub> (t) | $i_L(t)$             | $I_2(t)$            |                 |

| 1    | 0            | 0        | 0     | -E <sub>1</sub> | $E_1+E_2$          | -E <sub>2</sub>    | 0                    | 0                   | 0               |

| 2    | 1            | 1        | 1     | 0               | 0                  | 0                  | 0                    | 0                   | 0               |

| 5    | 1            | 0        | 0     | 0               | $E_1+E_2$          | -E <sub>2</sub>    | $i_L(t)$             | 0                   | $E_1$           |

| 4    | 0            | 0        | 1     | -E <sub>1</sub> | $E_1+E_2$          | 0                  | 0                    | i <sub>L</sub> (t)  | $E_2$           |

| 5    | 1            | 0        | 1     | 0               | $E_1+E_2$          | 0                  | i <sub>L</sub> (t)   | i <sub>L</sub> (t)  | $E_1+E_2$       |

| 6    | 0            | 1        | 1     | -E <sub>1</sub> | 0                  | 0                  | - i <sub>L</sub> (t) | 0                   | -E <sub>1</sub> |

| 7    | 1            | 1        | 0     | 0               | 0                  | -E <sub>2</sub>    | 0                    | -i <sub>L</sub> (t) | -E <sub>2</sub> |

| 8    | 0            | 1        | 0     | -E <sub>1</sub> | 0                  | -E <sub>2</sub>    | - i <sub>L</sub> (t) | -i <sub>L</sub> (t) | $-(E_1+E_2)$    |

voltage levels and one "zero" level (modes 1, 3, 4, and 5), switch  $T^0$  always conducts, while for all negative voltage levels and another "zero" level (modes 2, 6, 7, and 8), switch  $T^0$  always conducts. Therefore, it is possible to operate these two switches at the fundamental frequency to obtain five output levels. To do so, modes 1, 3 (or 4), and 5 need to be employed for the synthesis of positive levels (including a "zero" level), and modes 2, 6 (or 7), and 8 need to be

#### || Volume 10, Issue 1, January 2021 ||

#### DOI:10.15662/IJAREEIE.2021.1001012

employed for the synthesis of negative voltage levels (including a "zero" level). A procedure to achieve such operation is described in Section IV.

#### III. SWITCHING SCHEME

High-switching-frequency modulation methods like multi-carrier PWM and space vector modulation techniques have been used for MLI modulation control [22], [23]. On the other hand, active harmonic elimination, selective harmonic elimination, and fundamental frequency method are considered as low-switching-frequency methods [24]–[26]. The proposed topology can be modulated with any one of these methods with suitable adaptation. In the present work, the multicarrier PWM scheme is used. In a multicarrier PWM scheme, carrier signals are compared with the reference signal, and the pulses obtained are used for switching of devices corresponding to respective voltage levels. In the proposed topology, one switch may contribute for synthesis of more than one level at output terminals. Moreover, as mentioned in Section II-B, proper utilization of six modes (viz., modes 1, 2, 3, 5, 6, and 8) will lead to

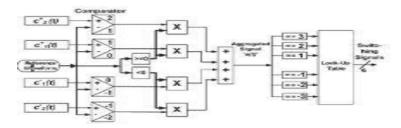

Fig. 4 Proposed control scheme for a five-level inverter

#### A. Modulation Scheme

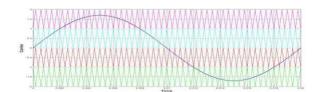

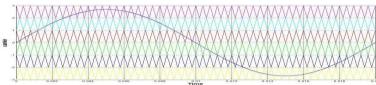

The schematic diagram of the modulation scheme is shown in Fig. 4, and the corresponding waveforms are shown in Four triangular waveforms of 1-kHz frequency each are used as carriers. Carrier signals are configured in alternate phase opposition disposition [3]. A sinusoidal waveform of 50-Hz frequency is taken as the reference signal. Carrier signals above the zero reference are designated as  $c^+(t)$  (k = 1, 2), and those below the zero

| Level of<br>Aggregated<br>Signal a(t)' | Mode | Load<br>voltage<br>v <sub>L</sub> (t)<br>[V] | Switches in<br>ON state                            |

|----------------------------------------|------|----------------------------------------------|----------------------------------------------------|

| 1                                      | 1    | 0                                            | T <sub>1</sub> ',T <sub>2</sub> ',T <sub>5</sub> ' |

| 2                                      | 5    | 24                                           | $T_{1}, T_{2}, T_{5}$                              |

| 5                                      | 5    | 48                                           | $T_1, T_2', T_5$                                   |

| -1                                     | 2    | 0                                            | $T_1, T_2, T_5$                                    |

| -2                                     | 6    | -24                                          | $T_1$ , $T_2$ , $T_5$                              |

| -5                                     | 8    | -48                                          | $T_1', T_2, T_5'$                                  |

Table II Lookup Table for Five-Level Inverter

reference are designated as  $C^-(t)$  (k = 1, 2). A continuous comparison of the reference with the carriers is executed. If the reference is greater than carrier  $C^+(t)$ , the com-parator gives "k" otherwise, it gives "k - 1." If the reference is greater than carrier  $C^-(t)$ , the comparator gives "-(k-1)" otherwise, it gives "-k." Signals so obtained are added so as to obtain an aggregated signal a(t). A one-to-one relationship of the levels contained in signal a(t) with corresponding levels in the output waveform is utilized to obtain switching pulses from signal a(t).

|| Volume 10, Issue 1, January 2021 ||

DOI:10.15662/IJAREEIE.2021.1001012

#### IV. SIMULATION RESULTS AND DISCUSSION

#### A. Five-Level Inverter

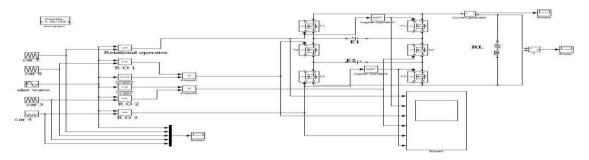

Fig. 7 Simulation Circuit Of Single Phase Inverter With Five Level Output

The figure 7 shows single phase MLI with 5-level output consisting of two dc sources of equal rating and three pair of active switches with 5-level multicarrier PWM control scheme. The circuit of single phase inverter with five level output contains 6 switches which are voltage controlled devices the control of switches can be done by using multi carrier sinusoidal pulse width modulation technique as shown in figure 7 The following control circuit four carrier signals & one reference signal the carrier signal of 1kHz frequency & reference signal of 50Hz frequency for soft switching of the T2 &T2'

Fig. 8 Reference and carrier waveform of five-level output

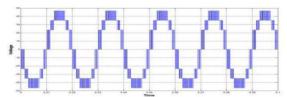

Fig. 9 Five-Level Current Waveform

Fig. 10 Five-Level Voltage Waveform

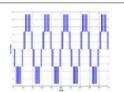

The harmonic spectrum of the five level load voltages is obtained with powergui FFT Analysis Tool. Here for output voltage of 48V the THD obtained is 37.25% and for output current of 4.79A is 37.25%.

Fig 11 Harmonic Spectrum of Five Level Load Voltage and Current

#### || Volume 10, Issue 1, January 2021 ||

#### DOI:10.15662/IJAREEIE.2021.1001012

#### **B.** Seven-Level Inverter

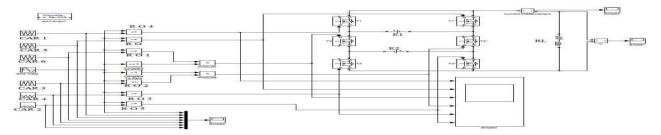

Fig. 12 Simulation Circuit of Single Phase Inverter With Seven Level Output

The figure shows single phase MLI with 7-level output consisting of two dc sources of equal rating and three pair of active switches with 7-level multicarrier PWM control scheme. The circuit of single phase inverter with seven level output contains 6 switches which are voltage controlled devices the control of switches can be done by using multi carrier sinusoidal pulse width modulation technique as shown in figure 5.7. The following control circuit four carrier signals & one reference signal the carrier signal of 1kHz frequency and reference signal of 50Hz frequency for soft switching of the T2 &T2'.

Fig. 13 Reference and carrier waveform for Seven-level output

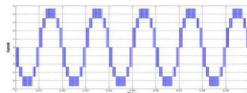

Fig. 14 Seven-level output voltage

Fig. 15 Seven-Level Current Waveform

#### V. CONCLUSION

As MLIs are gaining interest, efforts are being directed toward reducing the device count for increased number of output levels. A novel topology for MLIs has been proposed in this project to reduce the device count. The working principle of the proposed topology has been explained, and mathematical formulations corresponding to output voltage, output currents, have been developed. The results of a five-level and seven-level inverter based on the proposed structure have been validated by simulating using MATLAB/SIMULINK. Comparison of the proposed topology with conventional topologies reveals that the proposed topology significantly reduces the number of power switches and associated gate driver circuits.

The figure's shown above represents, fig 7 & 12 represent the simulation circuit's of proposed 5-Level & 7-Level simulation circuit respectively. Fig 8 & 13 represents the reference & carrier waveforms for triggering of transistors used for the proposed circuit. Fig 9 & 14 & fig 10 & 15 represents the output voltage & current respectively of the proposed level inverters. Fig 11 & 16 shows the THD as 37.25% & 22.56% of proposed 5-level & 7-level inverter respectively

#### **REFERENCES**

1. S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. Franquelo, B. Wu,J. Rodriguez, M. Perez, and J. Leon, "Recent advances and industrial applications of multilevel converters," IEEE Trans. Ind. Electron., vol. 57,no. 8, pp. 2553–2580, Aug. 2010.

#### || Volume 10, Issue 1, January 2021 ||

#### DOI:10.15662/IJAREEIE.2021.1001012

- 2. G. Buticchi, E. Lorenzani, and G. Franceschini, "A five-level single-phasegrid-connected converter for renewable distributed systems," IEEE Trans. Ind. Electron., vol. 60, no. 3, pp. 906–918, Mar. 2013.

- 3. J. Rodriguez, J.-S. Lai, and F. ZhengPeng, "Multilevel inverters: A surveyof controls, applications," Electron., vol. 49,no. 4, pp. 724–738, Aug. 2002.

- 4. S. De, D. Banerjee, K. Siva Kumar, K. Gopakumar, R. Ramchand, and C. Patel, "Multilevel inverters for low-power application," IET PowerElectronics, vol. 4, no. 4, pp. 384–392, Apr. 2011.

- 5. M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A surveyon cascaded multilevel inverters," IEEE Trans. Ind. Electron.,vol. 57,no. 7, pp. 2197–2206, Jul. 2010.

## International Journal of Advanced Research

in Electrical, Electronics and Instrumentation Engineering

📵 9940 572 462 🔯 6381 907 438 🔀 ijareeie@gmail.com