# International Journal of Advanced Research

in Electrical, Electronics and Instrumentation Engineering

Volume 9, Issue 10, October 2020

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

Impact Factor: 7.122

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 7.122|

|| Volume 9, Issue 10, October 2020 ||

### Solar Power Generation System with Seven-Level Boost Active-Neutral-Point-Clamped Inverter

Vimlabh Kant<sup>1</sup>, Prof. Manju Gupta<sup>2</sup>

M. Tech. Scholar, Department of Electrical & Electronics Engineering, OIST, Bhopal, India<sup>1</sup>

Associate Professor, Department of Electrical & Electronics Engineering, OIST, Bhopal, India<sup>2</sup>

**ABSTRACT:** This study proposes a seven-level power conversion system for a solar power generation system. This seven-level power conversion system consists of a cascade DC–AC inverter. The cascade DC–AC inverter comprises a full-bridge inverter and a T-type inverter. To reduce the dc-link voltage, a recenttopology that enhanced the voltage gain from half to unityhas been presented. In this letter, an alternative ANPC topology isestablished by using two T-type inverters. Two floating capacitorswith self-voltage balancing capability are integrated to achieve avoltage-boosting gain of 1.5. In addition, the proposed topology capable of generating seven voltage levels. Its operation is validated through circuit analysis followed by experimental results of a prototype.

KEYWORDS: Solar Power, PV Array, Inverter, Seven Level, Active Neutral Point Clamped

#### I. INTRODUCTION

The solar energy is becoming more important since it produces less pollution and the cost of fossil fuel energy is rising, while the cost of solar arrays is decreasing. The growing energy demand coupled with the possibility of reduced supply of conventional fuels, along with growing concerns about environmental preservation, has driven research and development of alternative energy sources that are cleaner, renewable and that produce little environmental impact. Among the alternative sources the electrical energy from PV is currently regarded as the natural energy source more useful, since it is free, abundant, and clean, distributed over the earth and participates as a primary factor of all other processes of energy production on earth.

The increasing need for electrical energy sources encourages people to use renewable electricity. The most popular renewable energy is photovoltaic. Photovoltaic is a component that utilizes sunlight to produce voltage.

Solar energy is a renewable energy that features easy installation, easy maintenance, no moving parts, no noise and negligible pollution. The cost of power generation from the solar power generation system (SPGS) is also decreasing so solar power is finding an increasing number of applications. The efficiency of SPGS is important because there is income from the generation source. The power efficiency is improved by improving solar cells and the power conversion interface. More new materials with high efficiency are still developed [1]. At the same time, many new power electronic components and power conversion topology have been proposed [2–3]. This study concerns power devices. The passive power devices include capacitors and inductors and they are used for voltage and current filtering. The power losses from passive power devices are due to conduction losses and switching losses. The conduction losses depend on the voltage drops of active power devices and court of active power devices in the current loop. The switching power loss is proportional to the change in voltage and current for a switching process for an active power device [4].

The switching power losses for active power devices can be attenuated by decreasing the voltage change in the switching process. Furthermore, the power losses of passive power devices are also improved because the ripples in voltage and current are suppressed by decreasing the voltage change in the switching process. Multilevel power converters generate more voltage levels in the AC output voltage so there is a smaller change in the voltage in the switching process for active power devices [5]. Therefore, multilevel power converters have lower switching losses due to active power devices. The ripples in the voltage and current for passive power devices are also reduced so power losses are decreased and their capacity is reduced. However, conduction losses due to active power devices are increased because there are more active power devices in the current loop. The control circuit and drive circuit are also complicated [6].

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 7.122|

#### || Volume 9, Issue 10, October 2020 ||

THD is a measurement of the quality of voltage or current. In normal conditions the output voltage form is a sinusoidal wave where THD is close to or equal to 0 (zero). THD is the percentage value between the total components of harmonics with its fundamental components. If the THD value is greater than the THD standard, it can lead to the destruction of electrical equipment, the burning of cable/conductor, overheat on the electric motor, and error on the electromechanical measurement of KWH meter [7].

#### II. MULTI LEVEL CONVERTER

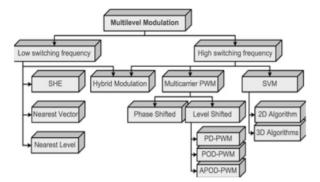

Figure 1 shows the multilevel converter modulation methods. The modulation control schemes for the multilevel inverter can be divided into two categories, fundamental switching frequency and high switching frequency PWM such as multilevel carrier-based PWM, selective harmonic elimination and multilevel space vector PWM Multilevel SPWM needs multiple carriers. Each DC source needs its own carrier. Several multi-carrier techniques have been developed to reduce the distortion in multilevel converters, based on the conventional SPWM with triangular carriers. Some methods use carrier disposition and others use phase shifting of multiple carrier signals. By generalizing, for an 'n' level multilevel inverter, (n-1) carriers are needed. The implementation of the various carrier PWM techniques that is possible for multi-level inverters are [3]-[6]:

Figure 1: Multilevel converter modulation methods

#### Level Shifted PWM (LSPWM)

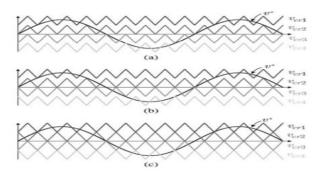

This modulation method is especially useful for NPC converters, since each carrier can be easily associated to two power switches of the converter. LSPWM leads to less distorted line voltages since all the carriers are in phase compared to PSPWM [8]. In addition, since it is based on the output voltage levels of an inverter, this principle can be adapted to any multilevel converter topology. However, this method is not preferred for CHB and FC, since it causes an uneven power distribution among the different cells. This generates input current distortion in the CHB and capacitor unbalance in the FC compared to PSPWM [3]-[6]. Figure 6 shows the LS-PWM carrier arrangements.

Figure 2: LS-PWM carrier arrangements: (a) PD, (b) POD, and (c) APOD.

#### Phase Shift Pulse Width Modulation

PWM signals are pulse trains which are applied to the gate of switches to perform the operation of converter. The pulse trains are fixed frequency and magnitude and variable pulse width [5]. There is one beat of settled extent in each PWM

#### | e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 7.122|

#### || Volume 9, Issue 10, October 2020 ||

period. In any case, the width of the beats changes from period to period as indicated by a regulating signal. At the point when a PWM flag is connected to the entryway of a power transistor, it causes the turn on and kills interims of the transistor to change starting with one PWM period then onto the next PWM period as indicated by the same regulating signal and thus working of converter begins. The recurrence of a PWM flag must be substantially higher than that of the regulating signal, the major recurrence, with the end goal that the vitality conveyed to the heap depends generally on the tweaking signal. The control of yield voltage is done utilizing beat width balance.

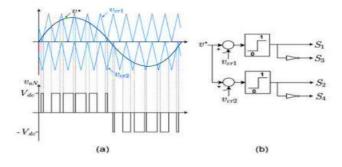

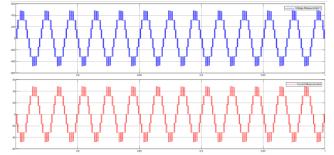

This technique uses a set of carriers that are all phase-shifted. The four triangular carriers are phase-shifted by 90°. Using the same sampling period, it has four times larger switching frequency than that of other techniques. This technique is specially conceived for FC and CHB converters. Since each FC cell is a two-level converter, and each CHB cell is a three-level inverter, the traditional bipolar and unipolar PWM techniques can be used, respectively. Due to the modularity of these topologies, each cell can be modulated independently using the same reference signal.

#### Figure 3: Phase Shift PWM

#### III. PV ARRAY

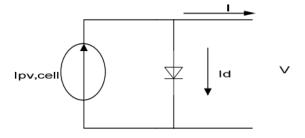

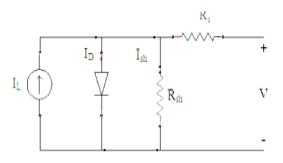

The photovoltaic cell converts the light energy into electrical energy depending on the irradiation of the sun and temperature in the atmosphere. Basically PVC is a PN junction diode [8] [4]. But in PN junction diode DCI AC source is needed to work, but here light energy is used as a source to produce DC output. PVC is a current control source not a voltage control source. The equivalent electrical circuit diagram of PVC is shown in the Figure 4.

Figure 4: Show ideal photovoltaic cell equivalent circuit

Figure 5: Equivalent Electrical Circuit of PVC

$$I_D = I_0 [\exp(V + IR_s) / KT - 1] (1)$$

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 7.122|

|| Volume 9, Issue 10, October 2020 ||

Therefore PVC output current is given in equation 2.

$$I = I_L - I_D - I_{Sh} \quad (2)$$

$$I = I_{L} - I_{0}[\exp(q(V + IR_{s})) / KT - 1] - (3)$$

$$(V + IR_{s}) / R_{sh}$$

Where  $I_D$  the diode is current,  $R_{sh}$  is the shunt resistance,  $I_L$  is the light generated current of solar array. Solar cell is basically a p-n junction fabricated in a thin wafer or layer of semiconductor. The electromagnetic radiation of solar energy can be directly converted electricity through photovoltaic effect. Being exposed to the sunlight, photons with energy greater than the band-gap energy of the semiconductor are absorbed and create some electron-hole pairs proportional to the incident irradiation. Under the influence of the internal electric fields of the p-n junction, these carriers are swept apart and create a photocurrent which is directly proportional to solar insolation. PV system naturally exhibits a nonlinear I-V and P-V characteristics which vary with the radiant intensity and cell temperature.

**MPPT ALGORITHM:-** Because of the lesser efficiency of photovoltaic array most of the energy, impacting over array gets wasted. The algorithm known as maximum power point tracking may be helpful to enhance the performance of solar panel. The MPPT algorithm works on principal of Thevenin, according which the power output of a circuit is maximum when impedance of circuit matches with the load of impedance. So now we have to match the impedance instead of tracking maximum power point.

There are different techniques used to track the maximum power point. Few of the most popular techniques are:

- Perturb and observe (hill climbing method)

- o Incremental Conductance method

- Fractional short circuit current

- Fractional open circuit voltage

- Neural networks

- Fuzzy logic

#### Perturb and observe

The P&O algorithm and "hill-climbing", both names refer to the same algorithm depending on how it is implemented. The basic difference between these two is that Hill-climbing involves a deviation of the duty cycle of the power converter and in P&O anxiety on the operating voltage of the DC link between the PV array and the power converter takes place [3]. The deviation of duty cycle of the power converter is the modification of the voltage of DC link between the PV array and the power converter refer as Hill-climbing, so both names refer to the same technique. What should be the next perturbation is decided by considering the sign of the last perturbation and the sign of the last increment in the power.

The perturbation will remain in the same direction if power is incremented, and if power is decreased then next perturbation will be in the opposite direction. The process will be repeated until the point of maximum power will be reached. Then the operating point oscillates around the MPP.

#### **Incremental conductance**

The slope of the curve between power and voltage of PV module is the deciding factor in incremental conductance algorithm, if it is zero it shows point of MPP positive (negative) on the left of it and negative (positive) on the right.

- $\Delta V / \Delta P = 0$  at the MPP

- $\Delta V / \Delta P > 0$  on the left

- $\Delta V / \Delta P < 0$  on the right

The change of MPP voltage is identified by comparing the change of the power to increment of the voltage of current curve.

#### Fractional short circuit current

Fractional short circuit current method states that the ratio between array voltage at maximum power  $V_{MPP}$  to its open circuit voltage  $V_{OC}$  is nearly constant.

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 7.122|

|| Volume 9, Issue 10, October 2020 ||

$V_{MPP} \approx k_1 V_{OC}$

The constant  $K_1$  is having value between 0.71 to 0.78. Now the value of  $V_{MPP}$  can be calculate by periodically measuring  $V_{OC}$ . This method is simple and cheap to implement but its efficiency is relatively low due to the utilization of inaccurate values of the constant k1 in the computation of  $V_{MMP}$ .

#### Photovoltaic cell

To convert the light energy supplied by sun the semiconductor solution is the photovoltaic cell it converts light energy to electrical energy by photovoltaic effect. The energy photons are available with light, if there energy is greater than the energy gap of atomic electronics, than the outer most electrons of atoms are get emitted because of the impact of these photon. These electrons get flow freely and cause current.

The construction of photovoltaic cell is similar as the construction of p-n junction diode. A photovoltaic cell is composed of two different layers of silicon one is P-type layer where negative ions are there with one less valence electron and other is N-type layer with positive ions with one extra valence electron. At the junction of these two layers extra electrons of N-layers get diffused with less electron space of P – layer and leave region with positive and negative ions only. This space is known as diffusion layer, the diffusion layer act as a protective layer and stops the transfer of electron across the junction when equilibrium is reached. When solar energy is imposed the energy of electrons available will increase and again transfer of electron get start. This will cause flow of current and convert solar energy into electric energy.

#### **IV. PROPOSED METHODOLOGY**

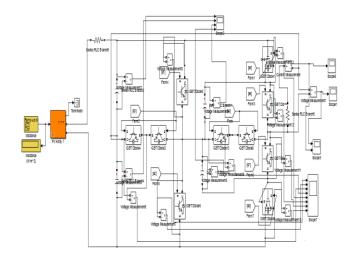

The proposed topology is called aDTT-7L BANPC following its circuit structure, which comprises two T-type inverters, as depicted in Fig. 6. Considering that all the power switches aremetal-oxide-semiconductor field effect transistors, the proposed ANPC inverter requires only two additional power switches to those in the previous study [11]. Two floating capacitors (*CF*1 and *CF* 2) are integrated to achieve a voltage-boosting gain of 1.5. With the magnitude of each level is 0.5 Vdc, the proposed topology is capable of generating seven levels from -1.5 Vdcto 1.5 Vdc. Analysis of the proposed DTT-7L-BANPC inverter is illustrated. The floating capacitor *CF* 1 is charged to Vdcwhen S4 and S9 are ON during 0.5 Vdcand-1.5 Vdc. In contrast, *CF* 2 is charged to Vdcduring 1.5 Vdcand -0.5 Vdc. The floating capacitors operate symmetrically for each half-cycle, which results in self-balancing of their voltages during operation.

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 7.122|

|| Volume 9, Issue 10, October 2020 ||

Figure 6: Simulation Model of Proposed Methodology

#### V. SIMULATION RESULT

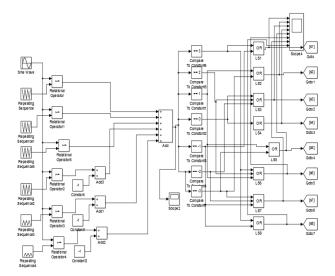

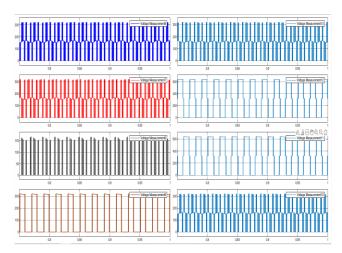

The precomputed switching angles using selective harmonicelimination pulsewidth modulation (SHEPWM) were first considered to analyze the operation of the proposed topology. Fig. 7 shows that the average floating capacitor voltages is equal to the input voltage Vdcof 100 V. Seven distinct voltage levels with the magnitude of each level equal to 50 V were clearly observed.

Figure 7: Output of Capacitor Voltage for Seven Level Inverter

Figure 8: Switching Blocking Voltage

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 7.122|

#### || Volume 9, Issue 10, October 2020 ||

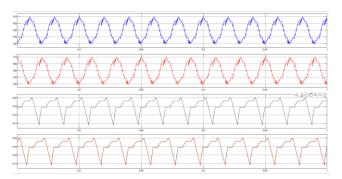

The voltage ripples of the floating capacitors were also measured. It is apparent from Fig. 5 that CF 1 was charged during 50 and -150 V, discharged during 100 and 150 V, and constant elsewhere. Symmetrical operation for CF 2 was observed such that it was charged during 150 and -50 V and discharged during -100 and -150 V. Good agreement between the experimental results and analysis conducted.

Figure 9: Output Voltage and Current of Seven Level Inverter

#### **VI. CONCLUSION**

A novel inverter topology, DTT-7L-BANPC, is reported in this letter. As the name implies, the proposed topology is capable of generating seven voltage levels with a voltage-boostinggain of 1.5. Self-voltage balancing of two floating capacitors was achieved during operation. The proposed topology was analyzed and tested. Experimental results validated its operation and feasibility. It is an alternative for a single-stage multilevelboost dc–ac power conversion system.

#### REFERENCES

- [1] D. Kiadehi, K. E. K. Drissi and C. Pasquier, "Voltage THD Reduction for Dual-Inverter Fed Open-End Load With Isolated DC Sources," in IEEE Transactions on Industrial Electronics, vol. 64, no. 3, pp. 2102-2111, March 2017.

- [2] N. D. Dao and D.-C. Lee, "Operation and control scheme of afive-level hybrid inverter for medium-voltage motor drives," *IEEETrans. Power Electron.*, vol. 33, no. 12, pp. 10178–10187, Dec.2018.

- [3] M. Abarzadeh and K. Al-Haddad, "An improved active-neutral-pointclampedconverter with new modulation method for ground power unitapplication," *IEEE Trans. Ind. Electron.*, vol. 66, no. 1, pp. 203–214, Jan.2019.

- [4] H. Wang, L. Kou, Y.-F. Liu, and P. C. Sen, "A seven-switch five-levelactive-neutral-point-clamped converter and its optimal modulation strategy,"*IEEE Trans. Power Electron.*, vol. 32, no. 7, pp. 5146–5161, Jul.2017.

- [5] Y. P. Siwakoti, "A new six-switch five-level boost-active neutral pointclamped (5L-Boost-ANPC) inverter," in *Proc. IEEE Appl. Power Electron.Conf. Expo.*, 2018, pp. 2424–2430.

- [6] Y. P. Siwakoti and F. Blaabjerg, "Common-ground-type transformerlessinverters for single-phase solar photovoltaic systems," *IEEE Trans. Ind.Electron.*, vol. 65, no. 3, pp. 2100–2111, Mar. 2018.

- [7] A. K. Yadav, M. Boby, S. K. Pramanick, K. Gopakumar, L. Umanand, and L. G. Franquelo, "Generation of high-resolution 12-sided voltage spacevector structure using low-voltage stacked and cascaded basic invertercells," *IEEE Trans. Power Electron.*, vol. 33, no. 9, pp. 7349–7358, Sep.2018.

- [8] W. Li, J. Hu, S. Hu, H. Yang, H. Yang, and X. He, "Capacitor voltagebalance control of five-level modular composited converter with hybridspace vector modulation," *IEEE Trans. Power Electron.*, vol. 33, no. 7,pp. 5629– 5640, Jul. 2018.

- [9] D. Cui and Q. Ge, "A novel hybrid voltage balance method for five-leveldiode-clamped converters," *IEEE Trans. Ind. Electron.*, vol. 65, no. 8, pp. 6020–6031, Aug. 2018.

- [10] W. Sheng and Q. Ge, "A novel seven-level ANPC converter topology andits commutating strategies," *IEEE Trans. Power Electron.*, vol. 33, no. 9,pp. 7496–7509, Sep. 2018.

- [11] H. Tian, Y. Li, and Y. W. Li, "A novel seven-level-hybrid clamped (HC)topology for medium-voltage motor drives," *IEEE Trans. Power Electron.*,vol. 33, no. 7, pp. 5543–5547, Jul. 2018.

Impact Factor: 7.122

## International Journal of Advanced Research

in Electrical, Electronics and Instrumentation Engineering

www.ijareeie.com