> (An ISO 3297: 2007 Certified Organization) Vol. 6, Special Issue 3, November 2017

# Comparative Performance Analysis of Multilevel Inverter Topologies with Renewable Energy

Dr.S.Priya<sup>1</sup>, G.Revathi<sup>2</sup>, P.Sangeetha<sup>3</sup>, R.Vasanthi<sup>4</sup>

Professor, Dept. of EEE, S A Engineering College, Chennai, Tamilnadu, India<sup>1</sup> UG Student, Dept. of EEE, S A Engineering College, Chennai, Tamilnadu, India<sup>2</sup> UG Student, Dept. of EEE, S A Engineering College, Chennai, Tamilnadu, India<sup>3</sup> UG Student, Dept. of EEE, S A Engineering College, Chennai, Tamilnadu, India<sup>4</sup>

**ABSTRACT:** This Paper explains about comparative performance analysis of multilevel inverter topologies. The topologies are the neutral point clamp multilevel inverter (NPCMLI) or Diode Clamped multilevel inverter, flying capacitor multilevel inverter (FCMLI) and cascaded H-bridge multilevel inverter (CMLI). The comparison of these inverters is based on criteria of output voltage quality, Total Harmonic Distortion (THD), circuitry complexity, and cost for implementation. IGBT's are used as a switching device for analysis. The comparison results are performed by detailed simulation results. The simulations are done by using MATLAB/SIMULINK software and the results are presented.

KEYWORDS: Diode clamped, neutral point, cascaded H-bridge multilevel inverters, THD

### **I.INTRODUCTION**

The major role of backup power supply is the DC to AC inverter which converts DC voltage from battery to an AC voltage that is necessary to operate electronics components. Inverter is an electrical device which converts direct current (DC) to alternate current (AC). A two-level inverter is used in order to generate the AC voltage from DC voltage but it creates harmonic distortions in the output voltage and also it has a high dv/dt as compared to that of a multilevel inverter. Some appliances in the industries however require medium or low power for their operation. Multilevel inverters are used for all industrial loads to high rating motors to requiring high power, while it might get damage to the other loads. Some medium voltage motor drives and some system requires medium voltage. The multi-level inverter has been introduced since 1975 as alternative in high power and medium voltage device. The Multi-level inverter is also like an inverter and it is also used for high rating machines and industrial applications as alternative in high power and medium voltage level at the output using multiple lower level DC voltages as an input. it offers several advantages as compared to hard switched two level pulse width modulated inverters it can able to operate at high voltage with lower dv/dt, high efficiency and lower electromagnetic interference . There are three important types of multilevel inverters they are 1.Neutral point or Diode clamped multilevel inverter 2.Flying Capacitor multilevel inverters 3.Cascaded -H-Bridge multilevel inverter.

### **II. MULTILEVEL INVERTER TOPOLOGIES**

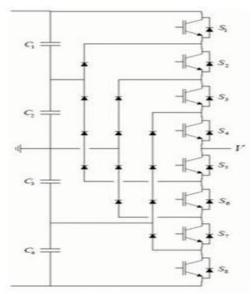

### A. Neutral Point Clamped Multilevel Inverter (NPCMLI)

The main concept of this inverter is to use diode to limit the voltage stress in power device. The switch over each capacitor and each voltage is Vdc. In which the diode is used as the clamping device to clamp the dc voltage so as to achieve steps in the output voltage.

(An ISO 3297: 2007 Certified Organization)

### Vol. 6, Special Issue 3, November 2017

#### Seven level neutral point clamped multilevel inverter

Examining the power circuit of the NPCMLI, if n is the Number of levels, p is the number of capacitors at the dc, q is the number of diodes, l is the number of switches.

No. of levels n=7No. of capacitors p=(n-1)No. of switches l=2(n-1)No. of diodes q=(n-1)(n-2)

Fig 1: 5 level Diode clamped multilevel inverter

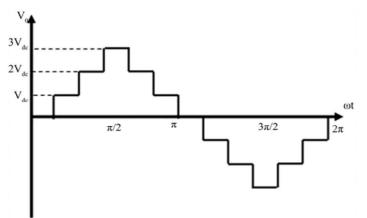

#### **Operation of 7level diode clamped multilevel inverter:**

From the table 1: To create a zero voltage level, the switches S4 to S9 are turned ON. Next the switches S3 to S8 are turned ON and remaining switches are turned OFF. So that we can obtained the voltage  $3v_d$ . Thus the level 1 is created. To create  $2v_d$  the switches from S6 to S11 is turned ON . Thus the second level was created . To create maximum voltage level  $v_d$ , the switches from S1 to S6 is turned ON. Thus the third level is created. Likewise the same step is repeated for next three levels.

| Table 1. Modes of operation of Neutral Point | Clamped Multilevel inverter (NPCMLI) |

|----------------------------------------------|--------------------------------------|

| ······································       |                                      |

| V <sub>0</sub>   | S <sub>1</sub> | S <sub>2</sub> | <b>S</b> <sub>3</sub> | <b>S</b> <sub>4</sub> | <b>S</b> <sub>5</sub> | S <sub>6</sub> | <b>S</b> <sub>7</sub> | S <sub>8</sub> | S <sub>9</sub> | S <sub>10</sub> | S <sub>11</sub> | S <sub>12</sub> |

|------------------|----------------|----------------|-----------------------|-----------------------|-----------------------|----------------|-----------------------|----------------|----------------|-----------------|-----------------|-----------------|

|                  |                |                |                       |                       |                       |                |                       |                |                |                 |                 |                 |

| Vd               | 1              | 1              | 1                     | 1                     | 1                     | 1              | 0                     | 0              | 0              | 0               | 0               | 0               |

| $2v_d$           | 0              | 1              | 1                     | 1                     | 1                     | 1              | 1                     | 0              | 0              | 0               | 0               | 0               |

| 3v <sub>d</sub>  | 0              | 0              | 1                     | 1                     | 1                     | 1              | 1                     | 1              | 0              | 0               | 0               | 0               |

| 0                | 0              | 0              | 0                     | 1                     | 1                     | 1              | 1                     | 1              | 1              | 0               | 0               | 0               |

| -v <sub>d</sub>  | 0              | 0              | 0                     | 0                     | 1                     | 1              | 1                     | 1              | 1              | 1               | 0               | 0               |

| -2v <sub>d</sub> | 0              | 0              | 0                     | 0                     | 0                     | 1              | 1                     | 1              | 1              | 1               | 1               | 0               |

| -3v <sub>d</sub> | 0              | 0              | 0                     | 0                     | 0                     | 0              | 1                     | 1              | 1              | 1               | 1               | 1               |

(An ISO 3297: 2007 Certified Organization)

Vol. 6, Special Issue 3, November 2017

Fig 2: 7level output waveform

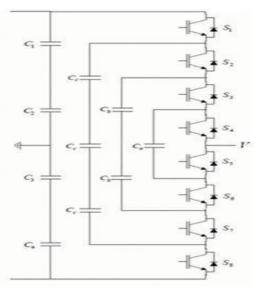

### B. Flying Capacitor Multilevel Inverter (FCMLI)

The structure of this inverter is similar to that of diode-clamped inverter except that instead of using clamping diodes, In this inverter we used capacitors in that place. This inverter uses capacitors to limit the voltage stress on the power devices. The flying capacitor involves series connection of capacitor clamped switching cells. This inverter also called has a ladder structure of dc side capacitors, each capacitor differs from the next capacitor. The voltage will increases between two adjacent capacitor gives the size of the voltage steps in the output waveform.

### Seven level flying capacitor multilevel inverter

No. of levels n=7No. of capacitors p=(n-1)No. of switches=2(n-1)No. of balancing capacitors=(n-1)(n2)/2

Fig.3: 5 level flying capacitor multilevel inverter

(An ISO 3297: 2007 Certified Organization)

### Vol. 6, Special Issue 3, November 2017

### **Operation of 7level flying capacitor multilevel inverter:**

From the table 2: To create zero level the switches S1-S3 & S7-S9 are turned ON and the remaining switches are turned OFF. Then the next level 3vdc is created by turning ON the switches from S1-S4 & S7,S8. By turning ON the switches S1-S5&S7 the next level 2vdc is created. To obtain a maximum voltage level  $v_d$  the switches from S1-S6 is turned ON. Thus the positive cycle is obtained. Likewise to create a levels in negative cycle the switching operation is performed as per given in table 2.

| Table 2. Modes of operation of the Flying Cap | acitor Multilevel Inverter (FCMLI) |

|-----------------------------------------------|------------------------------------|

|-----------------------------------------------|------------------------------------|

| V <sub>0</sub>   | S | S | S | S | S | S | S | S | S | S <sub>1</sub> | S  | S |

|------------------|---|---|---|---|---|---|---|---|---|----------------|----|---|

|                  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 0              | 11 | 1 |

|                  |   |   |   |   |   |   |   |   |   |                |    | 2 |

| v <sub>d</sub>   | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0              | 0  | 0 |

| $2v_d$           | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 0              | 0  | 0 |

| 3v <sub>d</sub>  | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0              | 0  | 0 |

| 0                | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0              | 0  | 0 |

| -v <sub>d</sub>  | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1              | 0  | 0 |

| -2v <sub>d</sub> | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1              | 1  | 0 |

| -3v <sub>d</sub> | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1              | 1  | 1 |

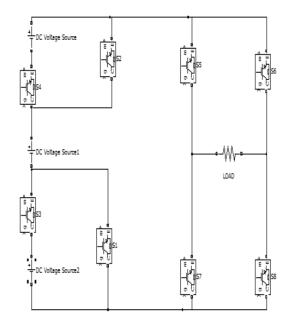

### C. Cascaded H-Bridge Multilevel Inverter (CMLI)

The cascaded H-bridge multilevel inverter is to use capacitors and switches and requires less number of components in each level. The combination of capacitors and switches pair is called an H-bridge and gives the separate input DC voltage for each H-bridge. it consists of H-bridge cells and each cells can provide the three different voltages like zero, positive DC and negative DC voltages. The concept of this inverter is based on connecting H-bridge inverters in series to get a sinusoidal voltage output. The output voltage is generated by the sum of the voltage by each cell. If Ns is the number of independent dc sources per phase.

### Seven level cascaded H-bridge multilevel inverter

No. of levels n=7 No. of switches=2(n-1) n= 2Ns+1 Ns is the number of independent DC source

| 0                  | S <sub>1</sub> | S <sub>2</sub> | $S_3$ | S <sub>4</sub> | $S_5$ | $S_6$ | <b>S</b> <sub>7</sub> | S <sub>8</sub> |

|--------------------|----------------|----------------|-------|----------------|-------|-------|-----------------------|----------------|

| v <sub>d</sub>     | 0              | 0              | 1     | 1              | 1     | 0     | 0                     | 1              |

| $2v_d/3$           | 0              | 1              | 1     | 0              | 1     | 0     | 0                     | 1              |

| $v_d/3$            | 1              | 1              | 0     | 0              | 1     | 0     | 0                     | 1              |

| 0                  | 0              | 0              | 0     | 0              | 1     | 1     | 0                     | 0              |

| -v <sub>d</sub>    | 0              | 0              | 1     | 1              | 0     | 1     | 1                     | 0              |

| $-2v_{d}/3$        | 0              | 1              | 1     | 0              | 0     | 1     | 1                     | 0              |

| -v <sub>d</sub> /3 | 1              | 1              | 0     | 0              | 0     | 1     | 1                     | 0              |

### Table 3. Modes of operation of the Cascaded Cell Multilevel Inverter (CCMLI).

(An ISO 3297: 2007 Certified Organization)

Vol. 6, Special Issue 3, November 2017

Fig 4: 7 level cascaded H-bridge multilevel inverter

### **Operation of 7level cascaded H-bridge multilevel inverter**

From the table 3:In order to have  $v_d$  in the output, switches S3-S8 are turned ON. Thus the level one is created . To obtain  $2v_d/3$ , the switches S2-S8 are turned ON and the remaining switches are turned OFF. Thus another level is created. Likewise this switching operation is performed for various levels by turning ON and OFF of switches. To create a zero level just create a short circuit across load by switching ON S5&S6. The same step is repeated for negative voltage levels  $-v_d/3$ ,  $-v_d/3$ ,  $-v_d$  by the switching operation as per given in table 3.

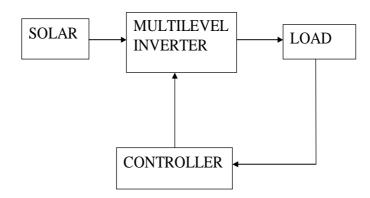

### III. BLOCK DIAGRAM

In this block shows that solar is given as input to the multilevel inverter. Solar energy gets from sunlight and converted into electricity. Solar is a D.C source it given to inverter. It converters DC into AC and given to the load. We prefer solar as an input because cost is very low inexpensive of carbon technology. It is also a source of electricity. It converts

(An ISO 3297: 2007 Certified Organization)

### Vol. 6, Special Issue 3, November 2017

light into electric current using the photovoltaic effects. For long distance transmission renewable energy replaced into fossil fuel. Solar as two technologies photovoltaic and concentrated solar power. In solar panel converts sunlight into electric power. In concentrated solar power we use solar thermal energy makes as a steam that converted into electricity.

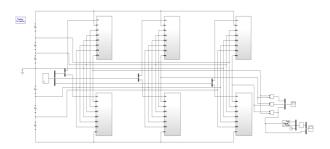

### **Simulation Circuit:**

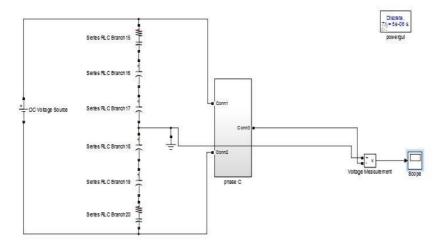

#### Fig 5 :7level neutral point clamped multilevel inverter

Subsystem:

Fig6: 7level neutral point clamped multilevel inverter Waveform

(An ISO 3297: 2007 Certified Organization) Vol. 6, Special Issue 3, November 2017

Fig 7 :7level neutral point clamped multilevel inverter

Fig 8: 7level Flying Capacitor multilevel inverter

(An ISO 3297: 2007 Certified Organization)

Vol. 6, Special Issue 3, November 2017

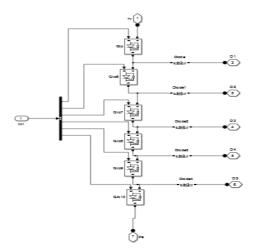

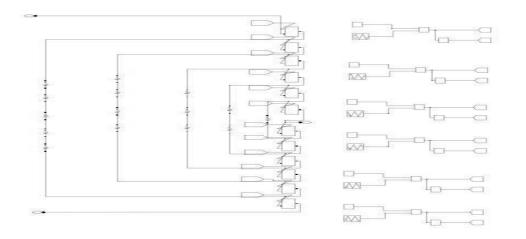

#### Subsystem:

Fig 9: 7level Flying Capacitor multilevel inverter

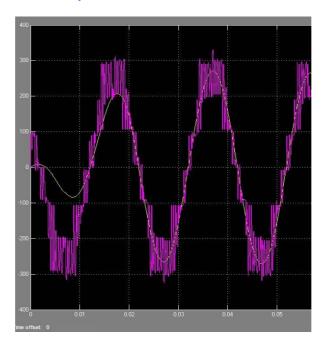

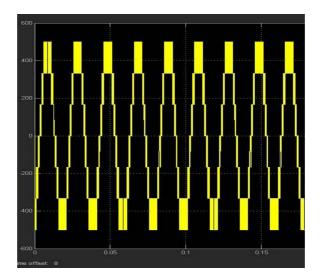

#### WAVEFORM:

Fig 10: 7level Flying Capacitor multilevel inverter

(An ISO 3297: 2007 Certified Organization)

### Vol. 6, Special Issue 3, November 2017

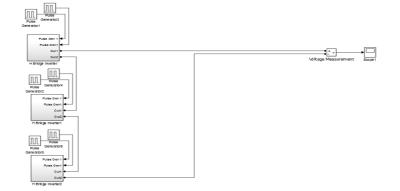

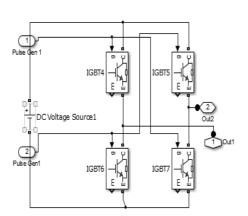

Subsystem:

fig 12: 7 level Cascaded H-Bridge multilevel inverter

Fig 13: 7level Cascaded H-Bridge multilevel inverter

Waveform

(An ISO 3297: 2007 Certified Organization)

### Vol. 6, Special Issue 3, November 2017

#### Comparison of multilevel inverters topologies:

| Topology             | DCMLI         | FCMLI       | CMLI               |

|----------------------|---------------|-------------|--------------------|

|                      | (7LEVEL)      | (7LEVEL)    | (7LEVEL)           |

| Main power           | 12            | 12          | 12                 |

| Switching devices    |               |             |                    |

| Clamping diodes      | 30            | 0           | 0                  |

| per phase            |               |             |                    |

| DC bus               | 6             | 6           | 3                  |

| capacitors           |               |             |                    |

| Balancing            | 0             | 15          | 0                  |

| Capacitors per       |               |             |                    |

| phase                |               |             |                    |

| Voltage unbalance    | average       | high        | Very small         |

| cost                 | medium        | more        | less               |

| THD% of output phase | 20.36%        | 21.54%      | 22.73%             |

| voltage              |               |             |                    |

| Main diodes          | 8             | 8           | 8                  |

| Circuit              | difficult     | difficult   | easy               |

| complexity           |               |             |                    |

| Switching            | IGBT          | IGBT        | IGBT               |

| device               |               |             |                    |

| weight               | medium        | more        | less               |

| Power                | 0.4MVA-4.8MVA | 0.3MVA-2MVA | 0.45MVA-           |

| range                |               |             | 7.5MVA             |

| Applications         | Motor drive   | Motor drive | Motor drive system |

|                      | systems       | systems     | PV, fuel cell,     |

|                      | STATCOM       | STATCOM     | battery system     |

In this paper the comparison of multilevel inverter based on voltage unbalance, cost, circuit complexity and total harmonic distortion. In NPCMLI have both advantage and disadvantage. The main drawback of this inverter is it requires more number of diodes for high power and controlling the individual converter of real power flow is difficult and advantage as no need of filters to reduce the harmonics and method of control is simple. In FCMLI within few cycle voltage can balanced main disadvantage in this inverter is need more capacitor. In this capacitor is cheaper than clamping diodes. It has low switching frequency and circuit become large in size. It decreases the power density. In CCMLI no capacitor or diode is needed. It has low switching frequency and less number of components is required for this inverter. The main disadvantage is separate D.C source is needed for real power conversion. Cost for breakdown implementation diode clamped is 80% and for power unit is 20%. In FCMLI 45% for breakdown implementation. 20% for capacitor. In CCMLI 65% for implementation and 20% for inverter. Using above statement comparison of 3 inverters table 4 can be developed. In order to generate an 7level inverter of CCMLI have less amount of semiconductor devices, THD value will be high and low cost.

#### **IV. CONCLUSION**

In this paper a comparison between the multilevel inverter topologies was discussed, such as neutral point clamped, flying capacitors and cascaded h-bridge multilevel inverters was performed. The result of this comparison is based on Total Harmonic Distortion, cost, circuit complexity, and voltage unbalance. Thus the three topologies are discussed here. It has both advantage and disadvantage. From the comparison it is clear that by increasing the number of levels, the THD will be decreased but the cost and circuit complexity will be increased. On the comparison of each topology the cascaded h-bridge has lowest cost and power loss is more than that of other topologies. On the other hand the flying capacitor inverter has lower power loss but the cost is more. The diode clamped multilevel inverters power loss is lower than cascaded h-bridge. From the overall comparison it was found out that cascaded h-bridge is the most preparing one

(An ISO 3297: 2007 Certified Organization)

### Vol. 6, Special Issue 3, November 2017

because here we can increase the levels of inverter up to n level without any problem in output when compared to other topology.

### REFERENCES

[1] Dr.S.Priya, A. Suresh and M. R.Rashmi "Investigation and Performance Analysis of Direct Torque Control of 3 $\varphi$  Induction Motor using 7 Level Neutral Point Clamped Multilevel Inverter" Indian Journal of Science and Technology, June 2016.

[2] Komal satose, S.N.Deshpande, Rahul Bhujabal and Priya Tiwari "Analysis of Different Topologies of Multilevel Inverters" International Journal for Innovative Research in Science & Technology (IJIRST) February2016.

[3]M. Murugesan, R.Pari, R.Sivakumar and S.Sivaranjani "DIFFERENT TYPES OF MULTILEVEL INVERTER TOPOLOGIES" March., 2016.

[4]Akhila.A, Manju Ann Mathews and Dr Nisha G.K "Comparative Analysis of Flying Capacitor and Diode Clamped Multilevel Inverters Using SPWM" IJISET - International Journal of Innovative Science, Engineering & Technology, August 2016.

[6]Purohit Sadanand Chandrashekhar "Neutral Point Clamped (Npc) Type Multilevel Inverter"INTERNATIONAL JOURNAL OF SCIENTIFIC & TECHNOLOGY SEPTEMBER 2016.

[7]C.R.Balamurugan, S.P.Natarajan, M.Arumugam "A Review On Various Multilevel Inverter Topologies" January 2015.

[8] Dr.S. Priya, A. Suresh and M. R. Rashmi "A Novel Scheme for Reduction of Torque Ripple in Direct Torque Control of Three Phase Squirrel Cage Induction Motor Using Seven Level Neutral Point Clamped Inverter" February 2013.

[9]S. Mohamed Yousuf, P. Vijayadeepan, Dr. S. Latha "The Comparative THD Analysis of Neutral Clamped Multilevel Z-Source Inverter using Novel PWM Control Techniques" June 2012.

[10] Mariusz Malinowski, K. Gopakumar, Jose Rodriguez and Marcelo A. Perez "A Survey on cascaded multilevel inverters" July 2010.

[11]Panagiotis Panagis, Fotis Stergiopoulos, Pantelis Marabeas and Stefanos Manias "Comparison of State of the Art Multilevel Inverters" August 2008.