(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 10, October 2015

# NIOS II Soft-Core Processor Based Wireless Notice Board

C. F. Pinto<sup>1</sup>, G. M. Naik<sup>2</sup>, J. S. Parab<sup>3</sup>

Assistant Professor, Department of Electronics, St. Xavier's College, Mapusa, Goa, India<sup>1</sup>

Professor, Department of Electronics, Goa University, Goa, India<sup>2</sup>

Assistant Professor, Department of Electronics, Goa University, Goa, India<sup>3</sup>

**ABSTRACT**: This paper is about the development of GSM based Wireless Notice board using Altera NIOS II softcore processor system. In today's world the transfer of information is seen that important notices takes time to be displayed on the notice boards as the person has to go physically to display the desired message on the Notice board. We have designed an embedded soft-core based system to solve this problem. Here embedded system on peripheral chip (SOPC) reconfigurable system receives SMS's from several authenticated mobile users and display's the message on the Notice Board. The implementation of the interface with GSM Modem and Liquid Crystal Display (LCD) was carried out using NIOS II soft-core system running on Altera FPGA DE2 board having target as Cyclone II EP2C35F672C6. The designed NIOS II processor based wireless notice board has various applications in several domains including public advertisements and educational sectors i.e in schools and colleges to update and display messages in real time from any geographical location of the user which reduces manual operation.

KEYWORDS: Soft-core, GSM, NIOS II, wireless, SOPC.

#### I. INTRODUCTION

A Notice Board is a very important in an organization and public place like airports, railway stations and auditoriums. People are now adapted to the idea ofthe world at its finger-tips, as they wish to control everything without moving an inch. The usage of mobile phones has increased rapidly over the years. GSM Modem with a sim card of GSM network operator, performs just like a mobile phone. The advantages of GSM modem is because of its RS232 port to communicate and develop embedded applications like data transfer and remote control, which has become important in all parts of the country. The GSM modem can be directly connected directly to the serial port of the controller, which can send / receive SMS or make / receive voice calls. This gave us an idea to use mobile phones to send & receive messages using GSM technology and then displays iton a notice board. If the administrator wants to display a message, he can send the information by SMS and update the message on LCD. The electronic display board updates with the incoming SMS from authentic mobile phone. The valid senders will be accepted and displayed while other SMS from any other mobile phone will be discarded. Thus message from valid senders will be broadcasted easily. Such a system proves to be beneficial for immediate transfer of information and can be easily implemented.

### **II. RELATED WORK**

A lot of research works have been done on wireless notice board using GSM technologies. Foram et al [1] designed Notice Board using GSM. The system consists of ATMEGA32 controller interfaced with GSM Modem and LCD. The notice board can be used by only one user and does not acknowledge the user.

Nivetha et al [2] developed a wireless notice board. This system was used ARMLPC2148 which was interfaced with a multiple displays. This past work does not acknowledge that the message has been displayed successfully. Also multiple users were not authorised.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 10, October 2015

Darshil et al [3] designed an electronic display with PIC microcontroller with graphical LED. However, the extent of reliability and authenticity of the wireless communication between the controller and mobile unit via the GSM module was not considered. Also multiple users were not authorised.

Kumar et al [4] designed a Wireless Notice Board with AT98S52 microcontroller and LCD display. However, the system has no feedback mechanism and multiple users were not authorised.

Ketkar et al [5] designed a GSM based LED display system. It consisted of AT89C51 microcontroller, a GSM Modem and LED display. The messages were displayed in the scroll format. The system was complex with no feedback mechanism and multiple users had no access the Notice Board.

In addition, Ukpa et al [6] developed a display Board using multiple PIC microcontrollers. The limitations were it accepts only seven characters at once. Also, the system does not acknowledge ascertaining the delivery of the message.

Furthermore Dogo et al [7] developed an Electronic display board. The developed system has feedback mechanism but multiple users were not authorised to access. Also the numbers of Characters Displayed on the LED matrix were few.

#### **III. DESIGN AND IMPLEMENTATION**

As discussed above, several researchers have designed wireless Notice board using different controllers but in our design we have used NIOS II soft-core processor to receive the message and acknowledges ascertaining that the message is displayed. Multiple users were authorised to access the wireless Notice Board. FPGA allows the developer to customise it to make instructions execute faster in single cycle. Advantages of using NIOS II are simplified designed update to higher level, reuse of design, lower latency between processor & FPGA components. Also Using NIOS II, we can choose the components to build a soft-core processor running on FPGA and rest of the FPGA hardware can be used for accelerating the parts of the code. Also less power is consumed using NIOS II running on Cyclone II compared to other predefined microcontrollers.

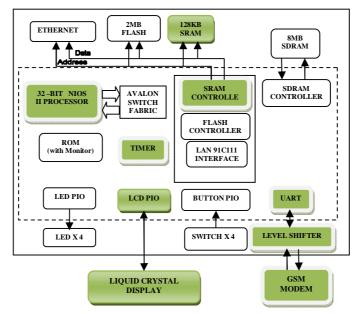

Fig. 1 Block diagram of a NIOS II soft-core processor Based Wireless Notice Board

The detailed block diagram of a NIOS II soft-core Processor system for Wireless Notice Board includes NIOS II running on Cyclone FPGA Board, GSM modem with SIM, LCD & Power Supply is shown above in fig. 1. The shaded blocks are the ones used in wireless notice board.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 10, October 2015

#### IV. NIOS II INTERACTION WITH GSM MODEM AND LCD

The SOPC components required to build the Wireless Notice board system is shown below in Fig. 2. The selected components are 32-bit NIOS II CPU, SRAM, JTAG UART, Interval Timer, RS232, LCD, SYSID, etc. After selecting the SOPC components, the entire NIOS II system is generated. The NIOS II processor is interfaced to the on board memories (SRAM) to store the code and the data received from GSM modem. NIOS II interacts with GSM modem using the RS232 interface.

| Use         | Con           | Module Name                      | Description                               | Clock | Base                       | End                  | IRC |

|-------------|---------------|----------------------------------|-------------------------------------------|-------|----------------------------|----------------------|-----|

|             |               | 🖂 cpu                            | Nios II Processor                         | 1     |                            |                      |     |

|             | -             | instruction_master               | Avalon Master                             | clk   |                            |                      |     |

|             | <b>F</b>      | data_master<br>jtag_debug_module | Avalon Master<br>Avalon Slave             |       | IRQ C<br><b>0x00100800</b> | IRQ 3.<br>0x00100fff | 1   |

| <b>&gt;</b> | $\rightarrow$ | ☐ jtag_uart<br>avalon_jtag_slave | JTAG UART<br>Avalon Slave                 | clk   | dx00101050                 | 0x00101057           |     |

|             | $\rightarrow$ | ⊡ uart<br>s1                     | UART (RS-232 Serial Port)<br>Avalon Slave | clk   | d 0x00101000               | 0x0010101f           |     |

| <b>&gt;</b> | $\rightarrow$ | <b>⊡ sysid</b><br>control_slave  | System ID Peripheral<br>Avalon Slave      | clk   |                            | 0x0010105f           |     |

|             | $\rightarrow$ | control_slave                    | Character LCD<br>Avalon Slave             | clk   | <i>∎</i> 0x00101040        | 0x0010104f           |     |

| <b>&gt;</b> | $\rightarrow$ | E timer<br>s1                    | Interval Timer<br>Avalon Slave            | clk   | n 0x00101020               | 0x0010103f           |     |

|             |               | sram_0<br>avalon sram slave      | SRAM<br>Avalon Slave                      | clk   | <b>₫ 0x00080000</b>        | 0x000fffff           |     |

Fig. 2 SOPC Block selected to Build System

The generated system is then brought to Quartus Bdf window and later the pin mapping is done as shown in fig. 3. In DE2 boards the components on the board are hardwired to the FPGA pins like Clock, Reset, LCD, SRAM and UART. They are configured as input or output pins as shown in fig. 3.

| clk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| LCD_E_from_the_lcd   DUTPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |

| LCD_RS_from_the_tcd   OUTPUT   LCD_RS_from_the_tcd     LCD_RW_from_the_tcd   OUTPUT   LCD_RW_from_the_tcd     LCD_data_to_and_from_the_tcd[70]   UCE_data_to_and_from_the_tcd[70]     SRAM_ADDR_from_the_sram_0[170]   OUTPUT   SRAM_ADDR_from_the_sram_0[170]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |

| LCD_RS_from_the_lcd   OUTPUT   LCD_RS_from_the_lcd     LCD_RW_from_the_lcd   OUTPUT   LCD_RW_from_the_lcd     LCD_data_to_and_from_the_lcd[7.0]   BDB   UCD_data_to_and_from_the_lcd[7.0]     SRAM_ADDR_from_the_sram_0[17.0]   OUTPUT   SRAM_ADDR_from_the_sram_0[17.0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

| LCD_data_to_and_from_the_lcd[7.0] BDIR LCD_data_to_and_from_the_lcd[7.0]   SRAM_ADDR_from_the_sram_0[17.0] OUTPUT SRAM_ADDR_from_the_sram_0[17.0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| SRAM_ADDR_from_the_sram_0[17.0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | · · · · · · · · · · · |

| SRAM CE N from the sram 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |

| SRAM_DQ_to_and_from_the_sram_0[15.0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50]                   |

| SRAM_LB_N_from_the_stam_0 SRAM_LB_N_from_the_stam_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                       |

| SRAM_OE_N_from_the_sram_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |

| SRAM_UB_N_from_the_sram_0 SRAM_UB_N_from_the_sram_0 SRAM_WE N_from_the_sram_0 SRAM_WE N_from_ |                       |

| SRAM_WE_N_from_the_sram_0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                       |

| rxd_to_the_uart INPUT rxd_to_the_uart txd_from_the_uart txd_from_the_uart txd_from_the_uart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |

| inst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

Fig. 3 Altera NIOS II soft-core system interface with GSM Modem and LCD.

After compiling the entire design, it shows how many logic elements, registers, pins & memory bits are utilised. We also found that this designed system utilizes 6% of available resources of logic elements as shown below in fig. 4 and remaining resources can be used for further improvement in the design in future.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 10, October 2015

| Flow Status<br>Quartus II Version<br>Revision Name | Successful - Mon Aug 03 17:47:16 2015<br>7.2 Build 207 03/18/2008 SP 3 SJ Web Edition<br>test1 |

|----------------------------------------------------|------------------------------------------------------------------------------------------------|

| Top-level Entity Name                              | test1<br>Cualana II                                                                            |

| Family                                             |                                                                                                |

| Device                                             | EP2C35F672C6                                                                                   |

| Timing Models                                      | Final                                                                                          |

| Met timing requirements                            | Yes                                                                                            |

| Total logic elements                               | 1,929 / 33,216 ( 6 % )                                                                         |

| Total combinational functions                      | 1,786 / 33,216 ( 5 % )                                                                         |

| Dedicated logic registers                          | 1,117 / 33,216 ( 3 % )                                                                         |

| Total registers                                    | 1117                                                                                           |

| Total pins                                         | 58 / 475 ( 12 % )                                                                              |

| Total virtual pins                                 | 0                                                                                              |

| Total memory bits                                  | 10,240 / 483,840 ( 2 % )                                                                       |

| Embedded Multiplier 9-bit elements                 | 0/70(0%)                                                                                       |

| Total PLLs                                         | 0/4(0%)                                                                                        |

|                                                    |                                                                                                |

Fig. 4 Summary of Compilation Report

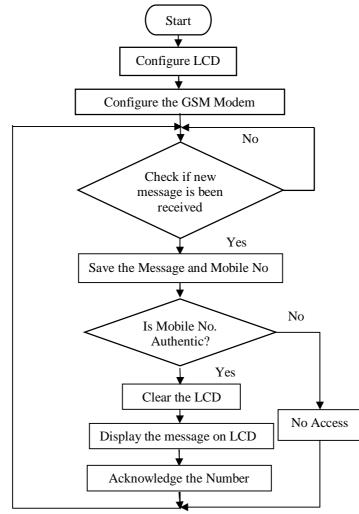

Once the design is compiled, the programming file is ported on Cyclone II using USB blaster. Next step is to run the C code on the NIOS II system to get the expected result. The flowchart for the C code which runs on the NIOS II system is shown in Fig. 5.

Fig 5. Flowchart for Wireless Notice Board.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 10, October 2015

First the LCD is configured as 8 bit data, display on, cursor on and other settings. The GSM modem is also configured to read the text messages and turns the echo off as shown in Table 1. Then it checks whether a new message is received. The message comes in a particular format wherein it is saved in different arrays like mobile number, date, time & message. Than the mobile number is verified with the mobile numbers saved in the system. If the mobile number is authentic, the display is cleared and the message is displayed on the LCD. The system sends an acknowledgement to the authentic mobile number stating that the message is displayed on the LCD. If the mobile number is not authentic, the message will not be displayed on the board and a message will be send to the mobile number saying no access. The message on the LCD gets updated again only if a new message is sent from the authentic mobile numbers.

| AT Command                                          | Description                                         |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------|--|--|--|

| AT                                                  | Check if serial interface and GSM modem is working. |  |  |  |

| ATE0                                                | Turn echo off, less traffic on serial line.         |  |  |  |

| AT+CMGF=0 PDU mode                                  | SMS string format, how they are compressed.         |  |  |  |

| =1 text mode                                        |                                                     |  |  |  |

| AT+CMGR = 1 Read message from $1^{st}$ location     | Read new message from a given memory location.      |  |  |  |

| =2 Read message from $2^{nd}$ location              |                                                     |  |  |  |

| AT+CMGS= "9823054798"                               | Send message to a given recipient.                  |  |  |  |

| Hello and terminating it with Cltr Z                |                                                     |  |  |  |

| $AT+CMGD = 1$ Delete message from $1^{st}$ location | Delete message.                                     |  |  |  |

| =2 Delete message from $2^{nd}$ location            |                                                     |  |  |  |

| Table 1. AT commands.                               |                                                     |  |  |  |

### V. RESULT AND DISCUSSIONS

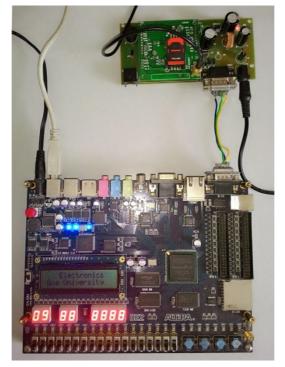

The Quartus II software was used for building the Entire Wireless Notice board system which was downloaded onto Cyclone II FPGA Board. Finally it was connected to the GSM Modem with power supply to get the desire result. The photo of Wireless Notice board using DE2 board is shown below in fig. 6.

Fig. 6 Wireless Notice board using DE2 board.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 10, October 2015

The C code running on Altera NIOS II processor receives the message from the GSM modem and is stored in the SRAM. The processor does the verification of the mobile number. If the message is sent by authentic mobile number, the message will be displayed on the (LCD) and an acknowledgement will be also sent as accepted. If message is not sent through authentic mobile number, the system sends a message as no access. The message continues to be displayed on the LCD. Whenever a new message is received by the designed system from authentic mobile user, the previous notice is cleared and a new message is displayed on the LCD.

#### VI. CONCLUSION

The Wireless Notice Board was efficiently designed using Altera FPGA DE2 Board. The code was written in C language and was loaded into the FPGA for testing the project which was successful in the process. This notice board accepted the SMS from mobile phones, checked whether the mobile numbers is authentic, saved and displayed the messages on the LCD. Also the user was acknowledged with a message.

#### REFERENCES

- [1] Kamdar, F., Malhotra, A., Mahadik, P., "Display Message on Notice Board using GSM," Advance in Electronic and Electric Engineering, vol. 3, no. 7, pp. 827-832, 2013.

- [2] Nivetha, S. R., Pujitha, R., Preethi, S., Yashvanthini, S. M., "SMS based Wireless Notice board with Monitoring System," International Journal of Advanced Electrical and Electronics Engineering, vol. 2, no. 3, pp. 58-62, 2013.

- [3] Darshil, J. M., Vishal, Vora, S., "Advertising Display System using LED and Graphical LED," International Journal of scientific Research & Development, vol. 1, no. 2, pp. 153-157, 2013.

- [4] Kumar, P., Bhrdwaj, V., Pal, K., Rathor, N. S., Mishra, A., "GSM Based e-Notice Board: Wireless Communication," International Journal of Soft Computing and Engineering, vol. 2, no. 3, pp. 601-605, 2012.

- [5] Ketkar, P. U., Tayade, K. P., Kulkarni, A. P., Tugnayat, R. M., "GSM Mobile Phone Based LED Scrolling Message Display System," International Journal of Scientific Engineering and Technology, vol. 2, no. 3, pp. 149-55, 2013.

- [6] Ukpa, O. S., Owuamanam, C. C., Okpala, N. K., Chukwudebe, G., Achumba, I. E., "SMS controlled Digital Display System," Emerging & Sustainable Technologies for Power & ICT in a Developing Society (NIGERCON), 2013 IEEE International Conference, pp. 153-165, 2013.

- [7] Dogo, E. M., Akogbe, A. M., Folorunso, T. A., Maliki, D., Akindele, A. A., "Development of Feedback Mechanism for Microcontroller Based SMS Electronic Strolling Message Display Board," African Journal of Computer & ICTs, vol. 7, no. 4, pp. 59-68, 2014.

#### BIOGRAPHY

Caje Francis Pinto is doing Ph.D. in the Department of Electronics Goa University, Goa. He is also working as an Assistant Professor in the Department of Electronics, St. Xavier's College, Mapusa, Goa. He is having seven years of teaching experience. His areas of interest are Embedded Systems and Biomedical Instrumentation.

Gourish Naik obtained his Ph.D from Indian Institute of Science, Bangalore (1987) and served the institute as research associate in the areas of Optoelectronics and Communication till 1993. For the last 15 years, he is associated with Goa University Electronics Program. He has to his credit around 50 odd research papers published in National and International Journals and has presented research works at various National and International Forums. He has authored a book on Embedded Systems published by Springer (Holland). Presently he is the Head of Electronics and Instrumentation division at Goa University.

Jivan S. Parab obtained his Ph.D on 'Non-Invasive Glucometer', funded by Indian Council of Medical Research, New Delhi. He is currently working as Assistant Professor, Department of Electronics, Goa University. He has co-authored two books with Springer (Netherland), in the area of Embedded System and programming. His areas of interest are Digital Signal Processing, Embedded Systems, Digital communication. He has published many research papers in reputed international and nation journals.