An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

**Organized by**

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

# Modelling and Comparison of Two DVR System Topologies using MATLAB

Jimson Varghese<sup>1</sup>

Assistant Professor, Dept. of EEE, Mar Baselios Institute of Technology and Science, Nellimattom, Kerala, India

**ABSTRACT**: The DVR (Dynamic Voltage Restorer) is a series connected device, which primarily can protect sensitive electric consumers against voltage dips and surges in the low voltage distribution grid. The paper presents a comparison study of two system topologies of DVR for voltage sag and harmonics compensation with an independent energy source or constant dc voltage supply and without using an energy source or taking voltage from the supply itself. The THD values of the output waveform is also taken separately to confirm the comparison study between the two topologies. The two DVR's are modelled and simulated using SIMULINK/MATLAB environment. Time domain simulations are given to verify the operation of the DVR with linear loads.

KEYWORDS: Power Quality, Dynamic Voltage Restorer, Custom Power Devices, Voltage Sag Mitigation.

## **I.INTRODUCTION**

Power quality has been a topic of great interest for decades and several issues have triggered interest in monitoring and improving the power quality. The power disturbances were categorized into four major events: low RMS events, high RMS events, transients and interruptions. More than 26% of the power disturbances came from the low RMS events, while 13% of that came from the high RMS events. The majority of the low RMS events (90%) lasted less than one minute, while 4% lasted more than thirty minutes.

Voltage sags and swells in the medium and low voltage distribution grid are considered to be the most frequent type of power quality problems based on recent power quality studies. Their impact on sensitive loads is severe. The impact ranges from load disruptions to substantial economic losses up to millions of dollars. Different solutions have been developed to protect sensitive loads against such disturbances but the DVR is considered to be the most efficient and effective solution. Its appeal includes lower cost, smaller size and its dynamic response to the disturbance. This paper presents the DVR principles and voltage restoration methods for voltage sags and swells in a distribution system. Simulation results were presented to illustrate and understand the performances of DVR under voltage sags/swells conditions.

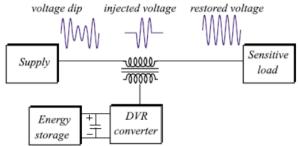

The dynamic voltage restorer (DVR)<sup>[12], [14]</sup> is a series connected device, which by voltage injection can control the load voltage. In the case of a voltage dip the DVR injects the missing voltage and it avoids any tripping of the load. Fig. 1 illustrates the operating principle of a DVR.

Fig. 1: Operating principle of a DVR.

# An ISO 3297: 2007 Certified Organization Vol. 4, Special Issue 1, March 2015 National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

Using the 'SimPowerSystems' library controls in MATLAB/SIMULINK an adequate simulation model of DVR is developed. Two system topologies, DVR with no energy storage device is compared with DVR with constant DC voltage energy source. DC-to-DC step up converter has been introduced in DVR without energy storage device. Both the proposed DVR's can compensate deep and long duration voltage sag and compensate steady-state harmonics.

## **II. CONFIGURATION OF DVR**

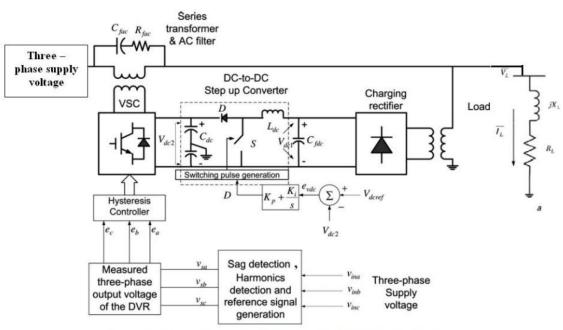

The configuration of the DVR <sup>[2]</sup> without separate energy source is shown in Fig. 2. The shunt converter connected to the load side is uncontrolled rectifier, which has uncontrollable dc output voltage  $V_{dc1}$ . The uncontrolled rectifier is connected to the load bus through a step down transformer. The dc output voltage of the rectifier Vdc1 is the input voltage of the dc-to-dc step up converter. The output voltage of the step up converter  $V_{dc2}$  is the input dc voltage of the VSC in the DVR. Although, with this configuration, the uncontrolled rectifier draws non-linear current, the DVR is able to eliminate all harmonics associated with the load voltage <sup>[15]</sup>. The load applied is an R - L linear load. In the Fig. 2 if we apply a constant dc voltage to the inverter instead of using the charging rectifier and dc-to-dc step up converter it will give the DVR configuration with separate dc energy source <sup>[7], [16]</sup>.

Fig. 2. Schematic diagram of the proposed DVR without energy source.

## II.A. DC Voltage Control of DVR

The step up converter controls the duty cycle, D to maintain its dc output voltage  $V_{dc2}$  at the reference set value  $V_{dcref}$ . This is done by using proportional and integral (PI) controller as shown in Fig. 2. The PI controller compares between  $V_{dcref}$  and  $V_{dc2}$  to produce the error  $e_{vdc}$ . The error  $e_{vdc}$  is passed through the PI controller to produce the suitable duty cycle, D which in turns fed into the switching pulse generation block to generate the switching pulses of the MOSFET. Here, the switching frequency of the MOSFET is selected to be 1027Hz<sup>[1]</sup>.

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

#### **Organized by**

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

#### **II.B.** Voltage Sag Detection Scheme

The sag detection method used here is Software Phase Locked Loop (SPLL) system <sup>[9]</sup>. <sup>[13]</sup>. The SPLL operating principle is based on the concept of voltage tracking where the SPLL tracks the positive sequence of the utility voltage. When voltage sag takes place in a three-phase power system, it causes voltage unbalance by generating negative and zero sequence voltages. The voltage unbalance causes an oscillation error in the measurement of the phase angle.

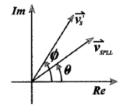

In Fig. 3, the SPLL output vector V<sub>SPLL</sub>. The Phase shift between the actual normalised utility voltage vector Vs' and the nominal unity vector VSPLL can be described as:

$$\phi - \theta = \arctan\left(\frac{V'_{s\beta}}{V'_{s\alpha}}\right) - \theta \approx \sin(\phi - \theta) = V'_{s\beta} \cos\theta - V'_{s\alpha} \sin\theta \quad (1)$$

Fig.3. Phase Shift of Vectors

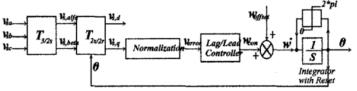

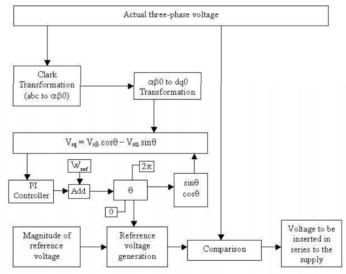

This phase shift <sup>[11]</sup> could be eliminated by using a PI controller or loop filters. Under locked conditions, the argument of the nominal unity vector is equal to the argument of the fundamental positive sequence vector of the utility voltages. The actual implementation of the above idea is shown in Fig. 4 where the instantaneous phase utility and  $\alpha$  voltages,  $V_{sa}$ ,  $V_{sb}$ ,  $V_{sc}$  are sampled and converted into  $V_{s\alpha}$  and  $V_{s\beta}$

Fig. 4. Block Diagram of Software Phase-Locked Loop (SPLL)

The transformed voltages are converted into Synchronous Rotating Frame (SRF), producing V<sub>sd</sub> and V<sub>sq</sub>, by using the output angle of the SPLL.

$$\begin{bmatrix} V_{s\alpha} \\ V_{s\beta} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \sqrt{3}/2 & -\frac{1}{2} \end{bmatrix} \begin{bmatrix} V_{s\alpha} \\ V_{sb} \\ V_{sc} \end{bmatrix} (2)$$

$$\begin{bmatrix} V_{sd} \\ V_{sq} \end{bmatrix} = \begin{bmatrix} \cos\theta & \sin\theta \\ -\sin\theta & \cos\theta \end{bmatrix} \begin{bmatrix} V_{s\alpha} \\ V_{s\beta} \end{bmatrix} (3)$$

In order to simplify the control,  $V_{sq}$  is normalized using the following equation. (4)

$$V_{sq} = V_{s\beta} \cos \theta - V_{s\alpha} \sin \theta$$

When the utility voltages are ideal and balanced, the dq components of the utility voltage vector, V<sub>s</sub> appear as DC values. Therefore, by regulating  $V_{sq}$ , it's possible to track accurately the argument of the positive space vector of utility voltages. Typically, a second order feedback control system is implemented for regulating  $V_{sq}$  and filtering the higher order harmonics.

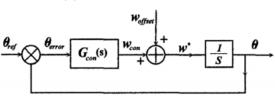

Fig. 5. Simplified Linear Model of SPLL.

In the SRF frame, if the output angle  $\theta$  is identical to the argument of the positive sequence space vector of the utility voltages, then the phase shift is equal to zero. This results in the dq components of the utility voltage vector Vs to appear as DC values. When the phase shift is small enough,  $(\phi - \theta)$  becomes valid. The SPLL can thus be treated as a linear control system shown in Fig.5. If  $G_{con}(S)$  is a PI controller or a lag/lead controller, the whole SPLL becomes a second order linear system.

## An ISO 3297: 2007 Certified Organization

## Vol. 4, Special Issue 1, March 2015

National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

For the PI controller,  $G_{con}(s)$  can be described as  $G_{con}(S) = (K_p + K_i / s)$  and the open and closed loop transfer functions of the SPLL <sup>[13]</sup> are given by:

$$G_{open}(s) = \frac{1}{s} (K_p + K_i / s); G_{close}(s) = \frac{2\xi \sigma_n s + \sigma_n^2}{s^2 + 2\xi \sigma_n s + \sigma_n^2}$$

(5)

where,  $\xi$  (DampingRatio) =  $\frac{K_p}{2} \cdot \frac{1}{\sqrt{K_i}} = 0.707$ ,

$\sigma_n$  (NaturalFrequncy) =  $\sqrt{K_i} = 22.36$

.and,  $K_p = 31.61, K_i = 499.97$

The proposed experimental SPLL system is shown in the flowchart diagram in Fig.6. The angle and frequency information is used to control the PWM converter applied to a Dynamic Voltage Restorer.

Fig.6. Flowchart showing the working of SPLL

The three-phase instantaneous output voltage ( $v_{sa}$ ,  $v_{sb}$  and  $v_{sc}$ ) from the voltage sag/swell detection block is the input to the hysteresis controller block.

## **II.C. Harmonic's Compensation**

Harmonic's compensation is done by using a single tuned filter. The signal generation is done by the voltage sag compensation subsystem itself. Here, the filter is used only to eliminate the fifth harmonics. It has the same configuration as the linear load connected to the system [4].

## II.D. AC voltage control of DVR

Conventional two-level hysteresis voltage control, which is one type of non-linear voltage control based on the voltage error, is implemented <sup>[5]</sup> in the DVR . It consists of a comparison between the output voltage  $V_0$  and the tolerance limits  $(V_H, V_L)$  around the reference voltage  $V_{ref}$ . While the output voltage  $V_0$  is between upper limit  $V_H$  and lower limit  $V_L$ , no switching occurs and when the output voltage crosses to pass the upper limit (lower band) the output voltage is decreased (increased). The hysteresis band is given as  $h = V_H - V_L$ . Here, the hysteresis band is taken as 0.000208pu. The hysteresis controller generates the switching pulses that are fed to the VSC. The generated three-phase voltage of the DVR is injected through a series transformer. As shown in Fig. 2, ac filters ( $R_{fac}$  and  $C_{fac}$ ) are connected across the series transformer to eliminate the switching ripples produced by the VSC.

## **III. DESIGN OF DVR COMPONENTS**

The design of the dc capacitor  $C_{fdc}$  of the uncontrolled rectifier, the dc capacitor  $C_{dc}$  and the inductor  $L_{dc}$  of the dc-to-dc step up converter based on single-phase voltage sag which induces a voltage fluctuation with twice the line frequency of the dc capacitor <sup>[6]</sup> is discussed. The parameters of the series and shunt transformers are the default parameters of the transformer model in SIMULINK/MATLAB. The voltage sag factor Ksag is defined as

$$\overline{K}_{sag} = \frac{V_{ssag}}{\overline{V}_{spre-sag}} \tag{6}$$

where  $V_{ssag}$  is the sag load voltage and  $V_{spre-sag}$  is the pre-sag load voltage.

$$D_{sag} = \left| \overline{K}_{sag} \right| \tag{7}$$

The magnitude of the voltage sag factor  $K_{sag}$  is equal to the depth of the voltage sag  $D_{sag}$ ; that is, the power ratings of the series PWM and the shunt uncontrolled (passive) converters in per unit of the load power are given as <sup>[10]</sup>

An ISO 3297: 2007 Certified Organization

## Vol. 4, Special Issue 1, March 2015

## National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

#### **Organized by**

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

$$S_{shunt} = S_{series} = \left| \frac{1 - \overline{K}_{sag}}{\overline{K}_{sag}} \right|$$

(8)

where  $S_{shunt}$  is the pu power rating of the shunt converter and  $S_{series}$  is the pu power rating of the series converter.

#### III.A. Sizing the dc capacitor C<sub>fdc</sub>

Single-phase voltage sag brings a negative-sequence component to the source voltage. In this case, the series converter injects the three-phase compensating voltages including the negative-sequence component, the amplitude of which is the same as that of the positive-sequence component. The negative-sequence voltage induces a voltage fluctuation with twice the line frequency to the dc capacitor. This section discusses the required capacity of the dc capacitor to smooth the voltage fluctuation when voltage sag occurs in the u-phase. When voltage sag occurs in the u-phase, the voltage depth is given as follows <sup>[6]</sup>:

$$\Delta V_{Su} = \sqrt{\frac{2}{3}} \delta V_s \cos \omega t$$

$$\Delta V_{Sv} = 0$$

$$\Delta V_{Sw} = 0$$

(9)

It is assumed that both the load current  $i_L$ , and the input current to the shunt converter,  $i_R$  are sinusoidal with unity power factor. Moreover, the u-phase source current is also assumed to be sinusoidal as follows:

$$i_{Su} = i_{Lu} + i_{Ru} = \sqrt{2}I_s \cos \omega t, \tag{10}$$

where  $I_s$  is the rms value of  $i_{su}$ . The series converter injects a compensating voltage to the load. The released active power PC is given by

$$P_C = \frac{\delta V_s I_s}{\sqrt{3}} + \frac{\delta V_s I_s}{\sqrt{3}} \cos 2\omega t.$$

(11)

The first term on the right hand side in above equation means an average value of  $P_c$ . The shunt converter should take in the average power to maintain the dc mean voltage across the dc capacitor. The power taken in,  $P_R$  is given by

$$P_R = \sqrt{3}V_s I_R = \frac{\delta V_s I_s}{\sqrt{3}},\tag{12}$$

where I<sub>R</sub> is the rms value of i<sub>R</sub>. Substituting this equation to i<sub>su</sub> yields,

(13)

$$I_s = \frac{3I_L}{3-\delta}.$$

On the other hand, the second term in  $P_C$  causes a voltage fluctuation to the dc capacitor. The energy stored in the dc capacitor,  $W_{store}$  is given by

$$W_{store} = \int (P_R - P_C) dt = -\int \frac{\delta V_s I_s}{\sqrt{3}} \cos 2\omega t dt$$

$$= \overline{W}_{store} - \frac{\delta V_s I_s}{2\sqrt{3}\omega} \sin 2\omega t \tag{14}$$

where  $W_{store}$  is the average energy of  $W_{store}$ .

It is assumed that the dc-capacitor voltage  $v_{dc}$  is the sum of the average voltage  $V_{dc}$  and the voltage fluctuation  $\Delta v_{dc}$ . The stored energy  $W_{store}$  is given by

$$W_{store} = \frac{C_{dc}}{2} v_{dc}^2 = \frac{C_{dc}}{2} (V_{dc}^2 + 2V_{dc}\Delta v_{dc} + \Delta v_{dc}^2).$$

(15)

Assuming that  $\Delta v_{dc} \ll V_{dc}$ , the voltage fluctuation is represented by

$$\Delta v_{dc} = -\frac{\delta V_s I_s}{2\sqrt{3}\omega C_{dc} V_{dc}} \sin 2\omega t = -\frac{\delta P_L}{2\omega C_{dc} V_{dc} (3-\delta)} \sin 2\omega t \quad (16)$$

Thus, the required capacity of the dc capacitor,  $C_{dc}$  is obtained by

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

## National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

#### **Organized by**

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

$$C_{dc} = \frac{\delta P_L}{2\omega\varepsilon V_{dc}^2(3-\delta)}$$

(17)

where  $\varepsilon$  is the ratio of the amplitude of the voltage fluctuation where with respect to the dc capacitor voltage V<sub>dc</sub>. The experimental setup rated at 415 V and 4.2 kW requires a dc capacitor of C<sub>dc</sub> = 30µF when the voltage fluctuation is limited within  $\varepsilon$  = 2.5% for compensation of a single-phase voltage sag with  $\delta$  = 0.3. The unit capacitance constant H is given by

$$H = \frac{\delta}{4\omega\varepsilon(3-\delta)}.$$

(18)

Substituting the previous conditions to the above equation yields H = 7.5 ms. Now the required capacitance of the dc capacitor  $C_{fdc}$  is given as follows:

$$C_{fdc} = \frac{D_{sag} V_{SL-L} I_L Cos\phi}{2\sqrt{3}\omega\varepsilon V_{dc1}^2 (3 - D_{sag})}$$

(19)

where  $V_{sL-L}$  is the line-to-line rated load voltage,  $I_L$  is the rated load current,  $\cos \phi$  is the power factor of the load,  $\omega$  is the angular speed ( $\omega = 2\Pi f$ ),  $\varepsilon$  is the allowable dc voltage fluctuation ( $\varepsilon = \Delta v_{dc1} / V_{dc1}$ ) and  $V_{dc1}$  is the dc voltage of the uncontrolled rectifier.

The dc voltage of the uncontrolled rectifier  $(V_{dc1})$  is almost equal to the magnitude of line-to-line load voltage  $(V_{dc1} = V_{sL-L})$ . Therefore the above equation can be rewritten as

$$C_{fdc} = \frac{D_{sag}I_L Cos\phi}{2\sqrt{3}\omega\varepsilon V_{SL-L}(3 - D_{sag})}$$

(20)

With the line-to-line voltage  $V_{sL-L} = 415$  V,  $\omega = 2\Pi f$  (f = 50Hz) and  $\varepsilon = 2.5\%$ , the C<sub>fdc</sub> is selected to be 200µF for 0.3 voltage sag depth and 0.8 lagging power.

## III.B. Sizing the inductor L<sub>dc</sub> and the dc capacitor C<sub>dc</sub>

The inductor  $L_{dc}$  and the capacitor  $C_{dc}$  of the dc-to-dc step up converter are given by <sup>[1]</sup>

$$L_{dc} = \frac{V_{dcl}D}{\Delta I_{dc2}f_s}$$

(21)

$$C_{dc} = \frac{I_{dc2}D}{\Delta V_{dc2}f_s}$$

(22)

where D is the duty cycle of the dc-to-dc step up converter,  $f_s$  is the switching frequency of the switch (MOSFET) of the dc-to-dc step up converter ( $f_s = 1027$  Hz),  $\Delta I_{dc2}$  output current ripple of the dc-to-dc step up converter ( $\Delta I_{dc2} = 0.02\%$ ),  $I_{dc2}$  is the dc output current of the dc-to-dc step up converter and  $\Delta V_{dc2}$  is the ripple dc output voltage of the dc-to-dc converter ( $\Delta Vdc2 = 0.02\%$ ).

The inductor  $L_{dc}$  is directly proportional to the duty cycle D and the dc voltage of the uncontrolled converter  $V_{dc1}$ . Since  $V_{dc1} = V_{sL-L}$ <sup>[10]</sup> and by setting  $D = D_{max}$ , we can write,

$$L_{dc} = \frac{V_{SL-L}D_{\max}}{\Delta I_{dc2}f_s}$$

(23)

The maximum duty cycle Dmax is given by

$$D_{\max} = \frac{V_{dc2} - V_{dc1\min}}{V_{dc2}}$$

(24)

where  $V_{dc2}$  is the dc output voltage of the dc-to-dc converter ( $V_{dc2} = 500V$ ) and  $V_{dc1min}$  is the minimum dc voltage of the uncontrolled rectifier.

The minimum dc voltage of the uncontrolled  $(V_{dc1min})$  corresponds to the maximum voltage sag occurred in the distribution system. Therefore  $V^{dc1min}$  can be given by

$$V_{dcl\min} = 1 - D_{sag} V_{sL-L} \tag{25}$$

By substituting  $V_{dc1min}$  into  $D_{max}$  and then the result is substituted in  $L_{dc}$ , the value of the inductor  $L_{dc}$  can be given by

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

## National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

#### Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

$$L_{dc} = \frac{V_{SL-L}(V_{dc2} + D_{sag}V_{SL-L} - 1)}{\Delta I_{dc2}f_s V_{dc2}}$$

(26)

Since  $D_{sag} = 0.3$ , the value of the inductor  $L_{dc}$ , which corresponds to the same voltage sag depth, is selected to be  $L_{dc} = 12$  mH.

Following the same procedure, the dc capacitor of the dc-to-dc step converter C<sub>dc</sub> can be given by

$$C_{dc} = \frac{I_{dc2}(V_{dc2} + D_{sag}V_{SL-L} - 1)}{\Delta V_{dc2}f_s V_{dc2}}$$

(27)

The active power injected by the DVR during the voltage sag, ignoring the losses in the PWM converter, is given <sup>[6]</sup> by

$$P_{inj} = D_{sag} \frac{V_{SL-L}}{\sqrt{3}} I_L \cos \phi = V_{dc2} I_{dc2}$$

(28)

The expression of the dc output current from the dc-to dc converter  $I_{dc2}$  can be obtained from the above equation and then substituted in  $C_{dc}$ . Thus, the dc capacitor  $C_{dc}$  can be given by

$$C_{dc} = D_{sag} \frac{V_{SL-L}}{\sqrt{3}} I_L \cos\phi \frac{(V_{dc2} + D_{sag}V_{SL-L} - 1)}{\Delta V_{dc2} f_s V_{dc2}^2}$$

(29)

For voltage sag depth  $D_{sag} = 0.3$  and power factor of 0.8, the value of capacitor  $C_{dc} = 30\mu$ F. It has to be mentioned that the size of  $C_{dc}$  is much smaller than the size of  $C_{fdc}$  since its main function is to reduce the ripple in the output dc voltage of the dc-to-dc step up converter  $V_{dc2}$ <sup>[1]</sup>.

## **IV. SIMULATION RESULTS**

## IV.A. DVR without any energy source

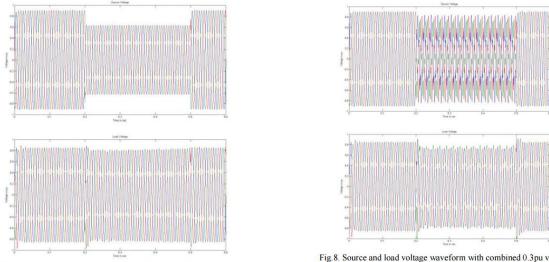

Fig. 7 shows the three phase source voltage and load voltage waveform of the system when 70% (0.3pu) voltage sag is applied to it. Here the sag was introduced for  $0.3 \sec (0.2 \sec - 0.5 \sec)$ . The first graph shows the sag affected source voltage and second graph shows the compensated load voltage.

Fig.7.Source and load voltage waveform of DVR with 0.3pu voltage sag.

Fig.8. Source and load voltage waveform with combined 0.3pu voltage sag and fifth harmonics.

Fig. 8 shows the three phase source voltage and load voltage waveform, when 70% (0.3pu) voltage sag and fifth harmonics was applied to the system for  $0.3 \sec (0.2 \sec - 0.5 \sec)$ . The first graph shows the source voltage waveform and second graph shows the load voltage waveform.

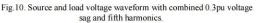

## IV.B. DVR with any energy source

Fig. 9 shows the three phase source voltage and load voltage waveform of the system when 70% (0.3pu) voltage sag is applied to it. Here the sag was introduced for  $0.3 \sec (0.2 \sec - 0.5 \sec)$ . The first graph shows the sag affected source voltage and second graph shows the compensated load voltage.

#### An ISO 3297: 2007 Certified Organization Vol. 4, Special Issue 1, March 2015 National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) **Organized by**

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

Fig. 10 shows the three phase source voltage and load voltage waveform, when 70% (0.3pu) voltage sag and fifth harmonics was applied to the system for  $0.3 \sec (0.2 \sec - 0.5 \sec)$ . The first graph shows the source voltage waveform and second graph shows the load voltage waveform.

Fig.9.Source and load voltage waveform of DVR with 0.3pu voltage sag.

Each topology has been rated by its expected performance for same main parameters. Although the best topology cannot be absolutely stated some main differences can be seen.

With the comparison system adopted, System 2 has the highest total point score, with a generally high performance score and relatively low cost and complexity. However, the negative grid effects and requirement for a high rated series converter could disqualify this solution for certain applications. System 1 is ranked as the second best topology with the highest performance scores, particularly for deep voltage sags, but with significant drawbacks regarding complexity, converter rating and overall cost (energy storage and power converter). System 1 and System 2 represent two conceptually different topologies (without energy storage and with energy storage) and might be the best alternatives depending on the applications.

| TABLE I                       |

|-------------------------------|

| THD values of the test system |

TABLE II Comparison of the two different DVR topologies

| L Conditions                                | Converter<br>with Stored<br>Energy<br>Source | Constant DC Linl<br>Voltage with No<br>Stored Energy<br>Source |

|---------------------------------------------|----------------------------------------------|----------------------------------------------------------------|

| Voltage sag of 0.3pu                        | 4.91                                         | 4.49                                                           |

| Voltage swell of 0.3pu                      | 4.91                                         | 4.49                                                           |

| B Fifth harmonics in the system             | 4.89                                         | 4.37                                                           |

| Voltage sag and fifth<br>harmonics combined | 4.91                                         | 4.49                                                           |

| Load current during 0.3pu sag               | 4.74                                         | 4.25                                                           |

| Load current during fifth<br>harmonics      | 4.79                                         | 4.1                                                            |

| Load current during combined distortions    | 4.74                                         | 4.25                                                           |

| Voltage sag of 0.5pu                        | 4.25                                         | 4.49                                                           |

| SI.<br>No. | Properties                                | Load Side Connected<br>Converter with<br>Stored Energy<br>Source | Constant DC Link<br>Voltage with No<br>Stored Energy<br>Source |

|------------|-------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------|

| 1          | Long voltage sag<br>duration compensation | Good (-)                                                         | Better (+)                                                     |

| 2          | Deep voltage sag<br>compensation          | Better (+)                                                       | Good (-)                                                       |

| 3          | DC link for voltage control               | No need (+)                                                      | Needed (-)                                                     |

| 4          | Size of energy storage                    | Large size (-)                                                   | No need (+)                                                    |

| 5          | Effects on grid                           | Medium (-)                                                       | Less (+)                                                       |

| 6          | Rating of shunt converter                 | Less rating (-)                                                  | No need (+)                                                    |

| 7          | Rating of series converter                | Less rating (+)                                                  | Less rating (+)                                                |

| 8          | System complexity                         | Less (+)                                                         | More (-)                                                       |

| 9          | Cost estimation                           | More (-)                                                         | Less (+)                                                       |

| 10         | Control of complexity                     | More (-)                                                         | Less (+)                                                       |

|            | Total (+)                                 | 4                                                                | 7                                                              |

## V. CONCLUSION

Power electronic solutions have gained increased interest, to solve well-known power quality problems. Voltage dips have been reported as a major power quality problem and a series connected converter, like the DVR, is considered to be an effective and cost-effective solution to mitigate voltage dips. Two system topologies for DVR have been

An ISO 3297: 2007 Certified Organization

#### Vol. 4, Special Issue 1, March 2015

## National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

#### Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India On 26<sup>th</sup> & 27<sup>th</sup> March 2015

compared through modeling and analysis. It includes one topology with stored energy and the other which uses the supply voltages and increase the supply current to restore the load voltages. The result shows that the topology without stored energy has got the better performance.

#### References

- [1] Rashid M.H.: \_Power Electronics, Circuits, Devices, and Applications', Prentice-Hall, 1993, 2nd Edn., ISBN 0-13-678996-2, 1993.

- [2] Jowder, F.A.L.: Design and analysis of dynamic voltage restorer for deep voltage sag and harmonic compensation', IET, Generation, Transmission and Distribution, Volume 3, Issue 6, Page(s):547-560, June 2009.

- [3] P. Boonchiam and N. Mithulananthan, —Understanding of Dynamic Voltage Restorers through MATLAB Simulation, I Thammasat Int. J. Sc. Tech., Vol. 11, No. 3, July-Sept 2006.

- [4] Asiminoaei L., Blaabjerg F., Hansen S.: Detection is key harmonic detection methods for active power filter applications', IEEE Ind. Appl. Mag., 2007, 13, Pp. 22–33.

- [5] Fawzi Al Jowder, Member IEEE, \_Modeling and simulation of DVR based on Hysteresis voltage control<sup>6</sup>, Electrical and Electronics Engg. Department, University of Bahrain, Kingdom of Bahrain. 33rd Annual conference of IEEE Industrial Electronics Society (IECON), Nov.5-8, 2007, Taipei, Taiwan.

- [6] Takushi J., Hideaki F., Hirofumi A.: Design and experimentation of a Dynamic Voltage Restorer capable of significantly reducing an energy storage element', IEEE Trans. Ind. Appl., 2008, 44, (3), Pp. 817–825.

- [7] Yan Li, Yun-ling Wang, Bu-han Zhang, Cheng-xiong Mao, Senior member IEEE, Modeling and simulation of DVR based on super capacitor energy storage', College of Electrical and Electronics Engineering, Huazhong University of Science and Techonology, Wuhan 430074, Hubei Province, China.

- [8] Rosli Omar, Nasrudin Abd Rahim, \_Mitigation of voltage sags/swells using DVR', Department of Electrical Engg., University Teknikal Malaysia, Melaka and University of Malaya, Kualalumpur, Malaysia. ARPN Journal of Engg. And Applied Sciences, Vol.4, No.4, June 2009.

- [9] Chris Fitzer, Mike Barnes, Member IEEE and Peter Green, \_Voltage sag detection techniques for a DVR<sup>4</sup>, Research Engineer in UMCST. IEEE transactions on Industry Appllications, vol.4, No.1, January/February 2004.

- [10] Nielsen J.G., Blaabjerg F.: A detailed comparison of system topologies for Dynamic Voltage Restorers', IEEE Trans. Ind. Appl., 2005, 41, (5), Pp. 1272–1280.

- [11] Nielsen J.G., Blaabjerg F., Mohan N.: Control strategies for Dynamic Voltage Restorer compensating voltage sags with phase jumps'. Proc. Ieee Apec'01, 2001, Vol. 2, Pp. 1267–1273.

- [12] C. Benachaiba, S. DIB, O. Abdelkhalek, B. Ferdi Bechar, -Voltage quality improvement using DVRI in 2002 IEEE 33rd Annual Power Electronics Specialists Conference, 2002, pp. 88-93.

- [13] Zhan C., Fitzer C., Ramachandaramurthy V.K., Arulampalam A., Barns M., Jenkins N.: \_Software phase-locked loop applied to Dynamic Voltage Restorer (DVR)<sup>c</sup>. IEEE Power Engineering Society Winter Meeting 2001, 2001, Vol. 3, Pp. 1033–1038.

- [14] Woodley N.H., Sundaram A., Coulter B., Morris D.: \_Dynamic Voltage Restorer demonstration project experience<sup>6</sup>. Presented At The Proc. 12th Conf. Elect. Power Supply Ind., Pattaya, Thailand, 1998.

- [15] Wei Li Y., Mahindav., Blaabjergf., Chiang Lohp.: A robust control scheme for medium-voltage-level DVR implementation', IEEE Trans. Ind. Electron., 2007, 54, (4), Pp. 2249–2261.

- [16] Ho C.N.-M., Chung H.S.H., Au K.T.K.: \_Design and implementation of a fast dynamic control scheme for capacitor-supported Dynamic Voltage Restorers<sup>4</sup>, IEEE Trans. Power Electron., 2008, 23, (1), Pp. 237–251.