International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

# Hybrid Compensation Scheme for Mitigating Voltage Fluctuation in Grid and Mitigate SSR

P.Cornelius Gunaraj

Lecturer, Dept. of EEE, VELTECH Institution, Chennai, Tamilnadu, India

**ABSTRACT:** In the recently developed schemes for voltage fluctuation and SSR has been proposed. In this paper it proposes the most advanced concepts has introduced with hybrid compensation scheme. The compensation measures taken to mitigate the voltage fluctuation is done with cascade scheme of static synchronous series compensation(SSSC) in addition to the voltage Source to compensate the grid voltage deviations and has the tendency to mitigate the sub synchronous resonance (SSR). The system maintains the grid voltage very closer to the current angle and continuous monitoring of grid voltage to mitigate the sub synchronous resonance. The DC voltage source with cascade circuit form the hybrid circuit and gives effective mitigation of voltage flickering and damping of sub synchronous resonance. Reliability of operating the power stations without interruption due to SSR will be achieved.

**KEYWORDS:** Mitigation of voltage fluctuation, AC Transmission System (FACTS), Sub Synchronous Resonance(SSR), series compensation, static synchronous series compensator (SSSC), voltage balancing, voltage-sourced converter.

### **I.INTRODUCTION**

Recently, it has been generally accepted that Static Synchronous Series Compensator (SSSC) using voltage source inverters has tremendous advantages for long- distance ac power transmission, such as improving power system stability and increasing the capacity of the transmission lines [1]. Because of high voltage and high power operation, proper multilevel topology of SSSC inverter been always discussed. between common multilevel inverters topologies, the cascaded H-bridge converter fits more for this application, because it has compact structure, easy scalability, fast response and good power quality [1, 2]. Particularly, its modularity simplifies the manufacturing and packaging of VSC hardware, thereby reducing the system costs and improving the system reliability [1-3]. But this topology has one big problem, unbalancing of the capacitors voltage [2-4].

It which is increases switches voltage stress which may lead to switch failure. Also increasing the capacitors voltage more than their nominal value decreases their life. Therefore balancing the modules voltage is necessary. The most application of multilevel topology in FACTS devices has been suggested for STATCOM, and some methods has been proposed for voltage balancing in [2-5].

The capacitor used in cascade bridge is the voltage balancing method as the capacitors voltage deviate or the voltage increased due to external factors there may be a chance of capacitor damage[1]&[2]. So as to overcome this draw drawback in the existing systems DC voltage source is introduced in the proposed system. The proposed system is to balance the transmission grid voltage, if unbalancing in capacitors may occur due to fluctuation in transmission line as because the capacitors charging voltage supplied from transmission line[5].

### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

# National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

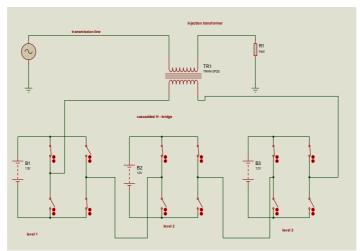

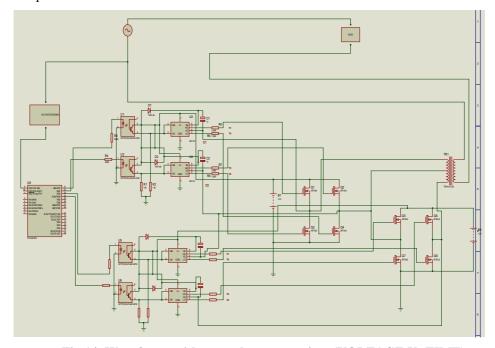

Fig. 1. Schematic diagrams of Hybrid model compensation.

The main objective of this system is to compensate the active power in transmission line and maintain the voltage to be inphase with line current or at reduced phase angle displacement. Also the power transmission system stability could be maintained and mitigation of flickering. Harmonics presence will also be reduced to remarkable level.

### II. CASCADE MODEL

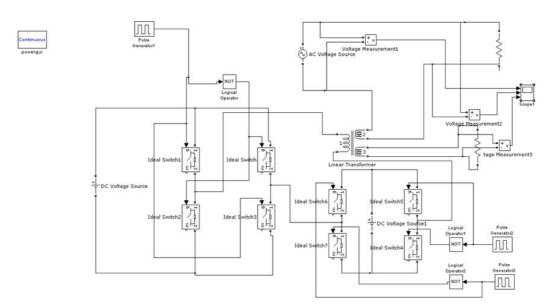

The Fig.2 shows the Cascaded Hybrid model. In this proposed SSSC model it is described in detail about the working principle and wave forms . To compensate the voltage in transmission line several methods are discussed in recent published systems. In all those methods the voltage compensating methodology is different since the injecting voltage to transmission lines are in series to the transmission line. The line current fully depends on the load and load fluctuation. The main concept of this system is to maintain the displacement angle between the line voltage and current should be maintained constant or very closer to the actual value. Transmission line voltage compensation method are mostly employed to maintain the voltage stability and this can be achieved by synchronous condenser, static VAR compensators etc[3].

Fig:2 Cascade Hybrid model.

### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

# National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

The cascade H-bridge technic base STATCOM and DSTATCOM are used in the existing system for vlotage balancing[10]. Difference in capacitor voltage may be due to imbalanced charging of capacitors[4]. In the proposed system DC voltage source will be connected in series at various switching sequence depending upon the PWM signals[8]. PWM signals are generated based on the transmission grid voltage. Transmission voltage parameters are sensed by PT(potential transfromer) and corresponding signals are given to the controller in which the PWM generation is decided.

In this switching device used is MOSFET. In this fig.2 the PWM pulse switches the MOSFET and the cascade connection is executed. Depending on the switching sequence the DC voltage source is connected in series as per the transmission voltage conditions. The compensating voltage is generated in cascade bridge circuit and injected to transmission line in series with help of injecting transformer. The load used may be resistive or resistive-inductive combination. The output voltage will appear as sine wave with reduced harmonics. In output of the cascade bridge multilevel sine wave form will be obtained[9]. When this multilevel sine wave is given to injection transformer and output of injection transformer will be sine wave with negligible harmonics. Thus this system does no need any special filter for harmonic reduction.

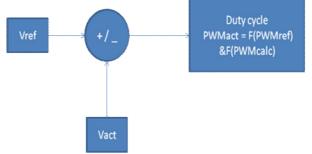

#### III. CONTROLLER

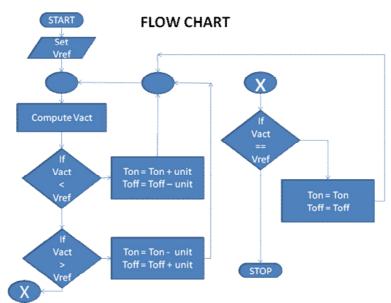

In the generation of PWM pulse controller should monitor the transmission line voltage parameters and depending on this parameters the duty cycle is decided. When the transmission voltage deviate from its inphase value the duty cycle varies with respect to the variation in the transmission line parameters. The actual voltage is taken from the transmission line and a reference voltage is set. Comparator combines the reference voltage and actual voltage which results in change of duty cycle. In the above give fig.3 show the controller diagram for proposed system. Actual PWM value decided by comparing the calculated value and reference value. The calculation for duty cycle is as follows.

Fig:3 Controller diagram.

PWM calc =  $(Ton/(T_{on}+T_{off}))$  Unit size is the min. size of the time(1ms).

$\underline{\text{If Vact} > \text{Vref}}$  Ton =Ton – unit size & Toff = Toff + unit size Duty cycle and firing angle will reduce.

If Vact<Vref Ton =Ton + unit size & Toff = Toff - unit size Duty cycle and firing angle will increase.

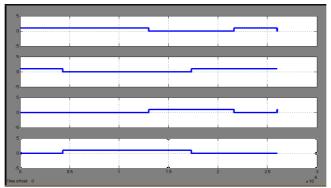

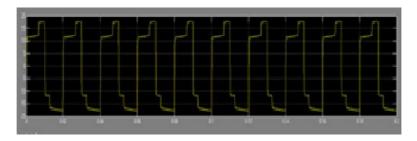

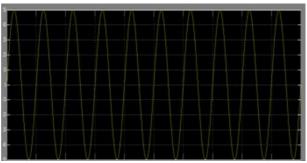

Fig.4 PWM generation for switches

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

# National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

The unit size is the time range which generated based on the controller calculated value. To maintain the voltage stability in the transmission line, the voltage in transmission line is sensed and then the compensation is to decieded as positive compensation and negative compensation[7]. If transmission line voltage is less than the reference voltage then positive compensation will be generated. If transmission voltage is greater than the reference voltage then negative compensation is initiated.[9]

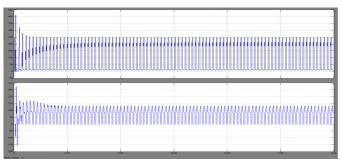

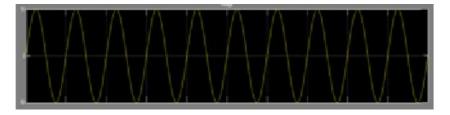

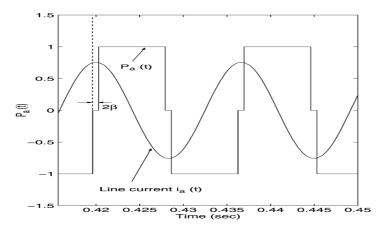

Fig.5 SSR Damping waveform

Fig.6 flow chart for controller logic.

The flow chart mentioned in the above fig.4 analysis the grid voltage condition and PWM is calculated by referring the grid voltage and standard reference voltage. Duty cycle is calculated and varied with respect to the actual gird voltage. If the computed voltage is less than the actual voltage then reference voltage then Ton =Ton + unit size. If actual voltage is greater than the reference voltage then Ton =Ton – unit size.

If the actual calculated voltage is equal to the reference voltage the system does not performs any and remains ideal. The controller check for the condition often and changes the duty cycle depending on the transmission voltage.

### IV. TEST SYSTEM RESULTS

The simulation work for the proposed system is done with help of simulink in MATLAB. The cascade H-bridge circuit is constructed and the MOSFET switches is used. In simulation instead of MOSFET switches are used. In ideal switch its assumed that the switching losses is nil. In most of the switching devices switching losses will there. Thus the

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

# National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

device selection for switching is to be done by referring the switching losses. In this system the operating principle describes ten mode of operation. In this five modes for positive half cycle and remaining modes for negative half cycle. The controller design is done in proteus software which could not be in MATLAB, because MATLAB does not support the microcontroller or some of the controllers not available in MATLAB simulink.

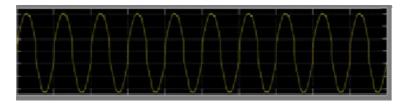

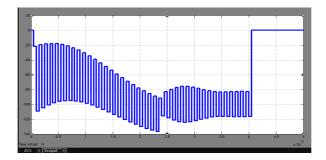

Fig.7 Output Waveforms of bridge(VOLTAGE Vs TIME)

Fig. 8. Simulation diagrams of the test system.

In the simulation the load used is resistive load. It can be replaced by RL load also. The pulse generator generates the PWM based on the controller and switching sequence is also decided based on the controller output. In simulation output it can be clearly obtained the positive compensation and negative compensation. The waveform obtained before the injection transformer appears like a rectangular wave form. The output waveform measured at the output or at the injection point will appear like a pure sine wave. Also as described earlier no filter design for to reduce the harmonics is needed because of negligible harmonic contents. The simulated circuit is shown in fig 5. The wave forms measured at different stage of transmission grid is illustrated below. In fig.6 shows the waveforms with positive compensation. The wave forms displayed in the order of actual transmission line voltage, positive compensation voltage and bridge output wave from.

International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

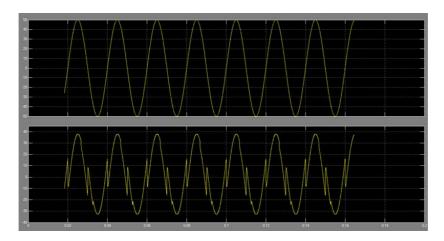

Fig.9 Waveforms with positive compensation.(VOLTAGE Vs TIME)

Fig.10 Waveforms at injection transformer output.(VOLTAGE Vs TIME)

In case if the transmission line voltage is greater then the actual voltage the negative compensation should be given. In this case the injecting voltage should be lesser than the actual voltage. This negative compensation is decided by the controller by referring the actual grid voltage and reference voltage.

Fig.11. Waveforms with negative compensation. (VOLTAGE Vs TIME)

In negative compensation the output wave form appears to be with 20% of harmonics when compare to the positive compensation. It also a negligible rating when the out if obtained from the injection transformer end. In the fig.8 the compensation scheme which remains inactive when the actual transmission line voltage is equal to reference voltage. The compensation scheme controller often monitors the transmission line voltage and corresponding signals are processed by the controller and generates the duty cycle which decides the PWM signals to the switching devices. Depending on the switching sequence the DC source connected in cascade and the compensation varies to the required level.[15].

### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

# National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

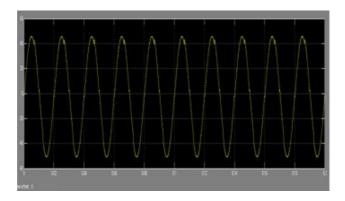

Fig.12 Waveforms with normal compensation. (VOLTAGE Vs TIME)

Fig.13 Waveforms with normal compensation. (VOLTAGE Vs TIME)

### V. HARDWARE PARAMETERS

Hardware implementation is done with reference to the above discussed simulation results.

Fig.14 Waveforms with normal compensation. (VOLTAGE Vs TIME)

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015)

Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

In the above fig.9 shown hardware layout diagram the voltage in the grid is to be maintained in phase with the current or very closer to the current. As to monitor the voltage in the transmission line the voltage sensing unit is established. The controller is checks the voltage in the transmission line via voltage sensing unit and activates the driver circuit which controls the gate of switching devices. The gate driver circuit consist of opto coupler with NPN configuration and gate driver IC- IR2101. Opto coupler prevents the controller from leakages if any. Gate drive IC generates the pulse that required to the switching devices. Thus operation of switching devices is done by the controller via gate drive circuit.

Fig.15 Waveforms for Switching

The controller parameters are adjusted through repeated time-domain simulations for different operating conditions. Increasing the proportional gain increases the sensitivity toward the error which, in turn, increases the response overshoot, while increasing the integral gain decreases the steady-state error at a cost of an increase in settling time. Thus, the choices of these gains are made so that fast settling time and minimum over- shoot (less than 10%) for a step change in input are achieved. The controller parameters are given in the Appendix.

For enhancing the damping of SSR, the SSSC is provided with a supplemental control [11], [14]. This control, shown in Fig. 5, has N channels that utilize the modal speeds as control signals. These modal speeds are derived from the turbine-gen-erator rotating mass speeds as [12] and [13]

The controller decides the switching sequence of the switching devices depending on the transmission voltage that that sensed via voltage sensing devices. By energizing the switching device in correct sequence the dc voltage source is made series connected or cut off depending on the required compensating level. By this process the stepped wave form is obtained which as less harmonics compared to square wave output in the existing methods.[15]

Fig.16 Waveform at cascade terminal(VOLTAGE Vs TIME)

#### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

# National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

For time-domain simulation studies, the synchronous gener- ators are represented in the d reference frame. The turbine generator mechanical systems are represented by a linear multimass-spring dashpot system. The transmission lines are modeled for the present study as transposed lumped parameters using series impedance representation. The infinite bus is represented as a constant amplitude sinusoidal voltage at syn-chronous frequency. Circuit breakers (CBs) are represented as ideal switches which can open at current zero crossings. Dy-namics of the turbine generator excitation and governor systems are included in the simulation model.

Figs. 7 and 8 show the time responses of systems I and II turbine-generator electrical output powers and shaft torsional torques during and after clearing a 4.5-cycle three-phase fault at bus B. The compensation degrees in systems I and II are assumed to be 57.4% and 65%, respectively. The compensation degree is defined by the ratio. As it can be seen from these figures the turbine-generator shaft torsional torques exhibit severe SSR instabilities. These two cases are adopted throughout this paper as the reference cases for comparisons with the considered hybrid series compensation scheme.

| Parameters           | Simulation             | Hardware                 |

|----------------------|------------------------|--------------------------|

| Coupling transformer | 300MVA,<br>30kV/ 6.6kV | 500VA, 230 V/ 12V        |

| Converter type       | Two – level PWM        | Two – level PWM          |

| DC voltage           | 14kV                   | 12V                      |

| AC voltage           | 33kV                   | 24V                      |

| Load                 | R = 200, L = 10mH      | R = 200  ohm, $L = 10mH$ |

| Switch               | Ideal switch           | MOSFET                   |

Table 1 parameters

#### VI. CONCLUSION

In this system the damping of SSR model is demonstrated with simulation results with appropriate wave forms. The current suppressor for sub synchronous frequency is to developed with an effective manner. The Harmonic content of the single level existing system is suppressed by using Cascaded H Bridge model SSSC and it gives smooth output wave form. Since Sine wave type output is produced at the output it can suppress harmonics that can travel through transmission line.

This system effective current suppresser calculation implemented to suppresses the sub synchronous resonance that interferes with protection and switchgear equipment. Using Cascaded H bridge SSSC model the Real Power in Transmission line is compensated.

### REFERENCES

- [1].Dipendra Rai, Sherif O. Faried, G.Ramakrishna and Abdel-Aty Edris, "An SSSC-Based Hybrid Series Compensation Scheme Capable of Damping Subsynchronous Resonance". *IEEE transaction on power delivery, vol27, no.2, april 2012.*

- [2]. Mohammad Hassan Ameri, Shahrokh Farhangi, "A New Simple Method for Capacitors Voltage balancing in Cascaded H-bridge SSSC" A New Simple Method for Capacitors Voltage balancing in Cascaded H-bridge SSSC, Member, IEEE 2010

- [3]. L. Gyugyi." Power electronics in electric utilities: Static VAR compensators". *Proceedings of the IEEE*. vol76, no.4 pp.483-493, Apr.1998

- [4]. Qiang Song, Wenham Liu, "DC Voltage Balancing Technique Using Multi-Pulse Optimal PWM for Cascade H-Bridge Inverters Based STATCOM", 35rh Annual IEEE Power Electronics Specialists Conference,2004

- [5]. M. Bongiorno, J. Svensson, and L. Ängquist, "Single-phase VSC based SSSC for subsynchronous resonance damping," *IEEE Trans. Power Del.*, vol. 23, no. 3, pp. 1544–1552, Jul. 2008.

- [6]. D. Rai, G. Ramakrishna, S. O. Faried, and A. Edris, "Enhancement of power system dynamics using a phase imbalanced series compensation scheme," *IEEE Trans. Power Syst.*, vol. 25, no. 2, pp. 966–974, May 2010.

- [7]. D. Rai, S. O. Faried, G. Ramakrishna, and A. Edris, "Hybrid series compensation scheme capable of damping subsynchronous resonance,"

### International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

An ISO 3297: 2007 Certified Organization

Vol. 4, Special Issue 1, March 2015

# National Conference on Recent Advances in Electrical & Electronics Engineering (NCREEE 2015) Organized by

Dept. of EEE, Mar Baselios Institute of Technology & Science (MBITS), Kothamangalam, Kerala-686693, India

On 26<sup>th</sup> & 27<sup>th</sup> March 2015

Proc. Inst. Eng. Technol. Gen., Transm. Distrib., vol. 4, no. 3, pp. 456–466, March 2010.

[8]. Chong Han, Alex Q. Huang , "A Generalized Control Strategy of Per-Phase DC Voltage Balancing for Cascaded Multilevel Converter based STATCOM". PESC 2007, pp.1746-1752,2007[9]. Jon Andoni Barrena\_, Luis Marroyo, "A Novel PWM Modulation Strategy for DC Voltage Balancing in Cascaded H-Bridge Multilevel Converters", EUROCON 2007, pp.1450-1456, 2007

[10] J.A.Barrenal, S.Aurtenecheal, J. M.Canales'M. "Design, Analysis and Comparison of Multilevel Topologies for DSTATCOM Applications", EPE 2005