> (An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 5, May 2015

# Simulation & Comparative Analysis of Diode Clamped Multilevel Inverter Using Sinusoidal PWM

Ravindra Kumar Tiwari<sup>1</sup>, Er. Vinaykumar Tripathi<sup>2</sup> PG Student [PE], Dept. of EE, SHIATS, Allahabad, UP, India<sup>1</sup> Assistant Professor, Dept. of EE, SHIATS, Allahabad, UP, India<sup>2</sup>

**ABSTRACT**: In industrial application there are requirements of such apparatus which could work at higher power and higher voltages. Traditionally we have been using two level inverters. These inverters are found not fit in case of high voltage. Multilevel inverter become very popular for high voltage and high power application. These multilevel start from three level converters. The concepts of these multilevel converter is that to achieve high power to use a series of power semiconductor switches with several lower voltage dc source to perform the power conversion by synthesizing a staircase voltage waveform. However, the output voltage is smother with smaller harmonics. At more level inverter the system become more complex and difficult to control but total harmonic distortion (THD) become reduced. In this paper, study of five level or seven level inverter with SPWM is investigated using MATLAB.

**KEYWORDS:**Multilevel Inverter, Total Harmonics Distortion.

## **I.INTRODUCTION**

One of the biggest problems in power quality aspects is the harmonic contents in the electrical system. Generally, harmonics may be divided into two types: 1) voltage harmonics, and 2) current harmonics. Current harmonics is usually generated by harmonics contained in voltage supply and depends on the type of load such as resistive load, capacitive load, and inductive load. Both harmonics can be generated by either the source or the load side. Harmonics generated by load are caused by nonlinear operation of devices, including power converters, arc-furnaces, gas discharge lighting devices, etc.

Load harmonics can cause the overheating of the magnetic cores of transformer and motors. On the other hand, source harmonics are mainly generated by power supply with non-sinusoidal voltage waveform. Voltage and current source harmonics imply power losses, Electromagnetic Interference (EMI) and pulsating torque in AC motor drives. Any periodic waveform can be shown to be the superposition of a fundamental and a set of harmonic components. By applying Fourier transformation, these components can be extracted. The frequency of each harmonic component is an integral multiple of its fundamental. There are several methods to indicate of the quantity of harmonics contents.

The most widely used measure in North America is the total harmonics distortion (THD) [3], which is defined in terms of the amplitudes of the harmonics, Hn, at frequency  $n\omega\theta$ , where  $\omega\theta$  is frequency of the fundamental component whose amplitude of H1 and n is integer. The THD is mathematically given by

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} H_{(n)}^2}}{H_1}$$

The multilevel voltage source inverter is recently applied in many industrial applications such as ac power supplies, static VAR compensators, drive systems, etc. One of the significant advantages of multilevel configuration is the harmonic reduction in the output waveform without increasing switching frequency or decreasing the inverter power output. The output voltage waveform of a multilevel inverter is composed of the number of levels of voltages, typically obtained from capacitor voltage sources. The so-called multilevel starts from three levels. As the number of levels

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 5, May 2015

reach infinity, the output THD approaches zero. The number of the achievable voltage levels, however, is limited by voltage unbalance problems, voltage clamping requirement, circuit layout, and packaging constraints.

## **II.MULTILEVEL INVERTER TOPOLOGY**

The basic three types of multilevel topologies used are

1) Diode-Clamped Multilevel Inverter.

2) Flying-Capacitor Multilevel Inverter.

3) Cascaded-Inverters with Separated DC Sources.

#### 1) Diode-Clamped Multilevel Inverter (DCMI)

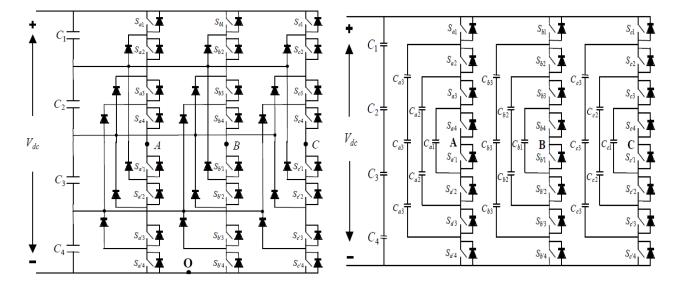

The diode-clamped multilevel inverter uses capacitors in series to divide up the dc bus voltage into a set of voltage levels. To produce m levels of the phase voltage, an m leveldiode-clamp inverter needs m-1 capacitors on the dc bus. A three-phase five-level diode-clamped inverter is shown in Fig. 2.1. The dc bus consists of four capacitors, i.e. C1, C2, C3, and C4. For a dc bus voltage *Vdc*, the voltage across each capacitor is *Vdc*/4, and each device voltage stress will be limited to one capacitor voltage level, *Vdc*/4, through clamping diodes. DCMI output voltage synthesis is relatively straightforward. To explain how the staircase voltage is synthesized, point O is considered as the output phase voltage reference point. Using the five-level inverter shown in Fig. 2.1, there are five switch combinations to generate five level voltages across A and O. Table 1 shows the phase voltage level and their corresponding switch states.

From Table 1, state 1 represents that the switch is on, and state 0 represents the switch is off. In each phase leg, a set of four adjacent switches is on at any given time. There exist four complimentary switch pairs in each phase, i.e., Sa1-Sa'1, Sa2-Sa'2, ..., and Sa4-Sa'4

Figure 2.1 A three-phase five-level diode-clamped inverterFigure 2.2 A 3  $\Phi$  five-level flying-capacitor inverter

#### 2) Flying-capacitor Multilevel Inverter (FCMI)

A FCMI shown in Fig. 2.6 uses a ladder structure of dc side capacitors where thevoltage on each capacitor differs from that of the next capacitor. To generate *m*-level staircase output voltage, *m*-1 capacitors in the dc bus are needed. Each phase-leg has an identical structure. The size of the voltage increment between two capacitors determines the size of the voltage levels in the output waveform.

It is obvious that three inner-loop balancing capacitors for phase leg A, Ca1, Ca2, and Ca3 are independent from those for phase leg B. All phase legs share the same dc link capacitors, C1-C4. Table 2 shows a possible switch combination of the voltage levels and their corresponding switch states.

(An ISO 3297: 2007 Certified Organization)

| Output                          |     |                 |                 | Switch          | h State          |                  |                  |                  | Output                              |                 |                 |                   | Swite           | h State          |                  |                    |                  |

|---------------------------------|-----|-----------------|-----------------|-----------------|------------------|------------------|------------------|------------------|-------------------------------------|-----------------|-----------------|-------------------|-----------------|------------------|------------------|--------------------|------------------|

| V <sub>AO</sub>                 | Sal | S <sub>a2</sub> | S <sub>a3</sub> | S <sub>a4</sub> | S <sub>a'1</sub> | S <sub>a'2</sub> | S <sub>a'3</sub> | S <sub>a'4</sub> | V <sub>AO</sub>                     | S <sub>a1</sub> | S <sub>a2</sub> | S <sub>am-1</sub> | S <sub>am</sub> | S <sub>a'1</sub> | S <sub>a'2</sub> | S <sub>a'm-1</sub> | S <sub>a'm</sub> |

| V <sub>5</sub> =V <sub>dc</sub> | 1   | 1               | 1               | 1               | 0                | 0                | 0                | 0                | V <sub>5</sub> =V <sub>dc</sub>     | 1               | 1               | 1                 | 1               | 0                | 0                | 0                  | 0                |

| V <sub>4</sub> =3Vdc/4          | 0   | 1               | 1               | 1               | 1                | 0                | 0                | 0                | V <sub>4</sub> =3V <sub>dc</sub> /4 | 1               | 1               | 1                 | 0               | 1                | 0                | 0                  | 0                |

| V <sub>3</sub> =Vdc/2           | 0   | 0               | 1               | 1               | 1                | 1                | 0                | 0                | V <sub>3</sub> =V <sub>dc</sub> /2  | 1               | 1               | 0                 | 0               | 1                | 1                | 0                  | 0                |

| V2=Vdc/4                        | 0   | 0               | 0               | 1               | 1                | 1                | 1                | 0                | V <sub>2</sub> =V <sub>dc</sub> /4  | 1               | 0               | 0                 | 0               | 1                | 1                | 1                  | 0                |

| V1=0                            | 0   | 0               | 0               | 0               | 1                | 1                | 1                | 1                | V1=0                                | 0               | 0               | 0                 | 0               | 1                | 1                | 1                  | 1                |

# Vol. 4, Issue 5, May 2015

Table 1 Diode-clamped five-level inverter voltageTable 2 A possible switch combination of the voltage

levels and their switch states.levels and their corresponding switch states.

.In fact, there is more than one combination to produce output voltages V2, V3, and V4. That makes the FCMI more flexibility than DCMI. Table 2, however, shows only one possible combination.

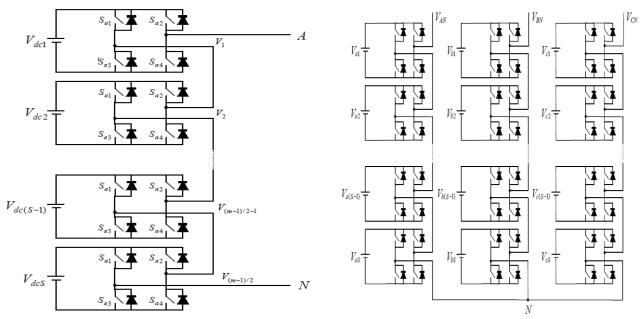

#### 3) Multilevel Inverter Using Cascaded-Inverters with Separated DC Sources

The last structure introduced in this thesis is a multilevel inverter, which uses cascaded inverters with separate dc sources (SDCSs). The general function of this multilevel inverter is the same as that of the other two previous inverters. The multilevel inverter using cascaded-inverter with SDCSs synthesizes a desired voltage from several independent sources of dc voltages, which may be obtained from either batteries, fuel cells, or solar cells. This configuration recently becomes very popular in ac power supply and adjustable speed drive applications. This new inverter can avoid extra clampingdiodes or voltage balancing capacitors. A single-phase m-level configuration of such an inverter is shown in Fig 2.3.

Figure 2.3 Single-phase structure of aFigure 2.4: A general three-phase Wyemultilevelcascaded inverterconfiguration cascaded-inverters based inverter.

#### (An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 5, May 2015

Each SDCS is associated with a single-phase full-bridge inverter. The ac terminal voltages of different level inverters are connected in series. By different combinations of the four switches, S1-S4, each inverter level can generate three different voltage outputs, +Vdc, -Vdc, and zero. The ac output of each of the different level of full-bridge inverters are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs. Note that the number of output phase voltage levels is defined in different way from those of two previous inverters. In this topology, the number of output phase voltage levels is defined by m = 2s+1, where s is the number of dc sources.

A 7-level cascaded-inverters based inverter, for example, will have three SDCSsand three full-bridge cells. Minimum harmonic distortion can be obtained by controlling the conducting angles at different inverter level, which will be proposed in section IV.For a three-phase system, the output voltage of the three cascaded inverters can be connected in either wye or delta configuration. For example, a wye-configured m-level inverter using cascaded-inverters with s separated capacitors is illustrated in Fig. 2.4.

#### **III. SIMULATION & RESULT**

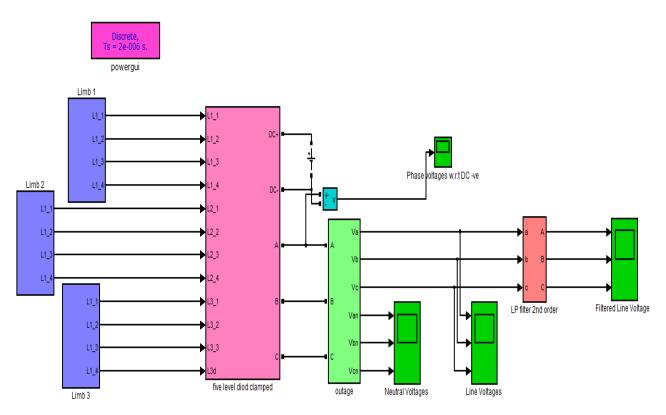

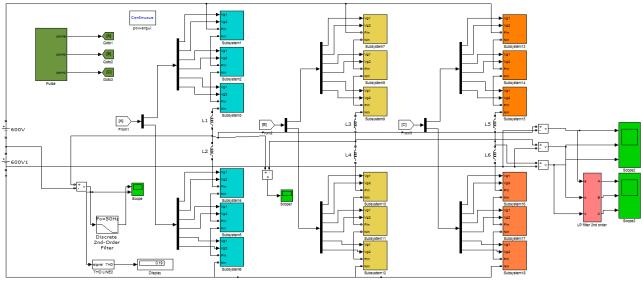

#### FIVE-LEVEL DCMI

The diode-clamped multilevel inverter uses capacitors in series to divide up the dc bus voltage into a set of voltage levels. To produce m levels of the phase voltage, an m-level diode-clamp inverter needs m-1 capacitors on the dc bus. A three-phase five-level diode-clamped inverter is shown in Fig. 3.1. The dc bus consists of four capacitors, i.e., C1, C2, C3, and C4. For a dc bus voltage Vdc, the voltage across each capacitor is Vdc/4, and each device voltage stress will be limited to one capacitor voltage level, Vdc/4, through clamping diodes. DCMI output voltage synthesis is relatively straight forward.

Fig. 3.1 Simulation circuit (5-level DCMI)

(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 5, May 2015

| Output                           | Swite | h State |     |     |     |     |     |     |

|----------------------------------|-------|---------|-----|-----|-----|-----|-----|-----|

| V <sub>AO</sub>                  | Sal   | Sa2     | Sa3 | Sa4 | Sa' | Sa' | Sa' | Sa' |

|                                  |       |         |     |     | 1   | 2   | 3   | 4   |

| V5=Vdc                           | on    | on      | on  | 011 | Off | off | off | off |

| V <sub>4</sub> =3V <sub>dc</sub> | off   | on      | on  | 011 | On  | off | off | off |

| /4                               |       |         |     |     |     |     |     |     |

| V3=Vdc/                          | off   | off     | on  | 011 | On  | on  | off | off |

| 2                                |       |         |     |     |     |     |     |     |

| V2=Vdc/                          | off   | off     | off | 011 | On  | on  | on  | off |

| 4                                |       |         |     |     |     |     |     |     |

| V1=0                             | off   | off     | off | off | On  | on  | on  | on  |

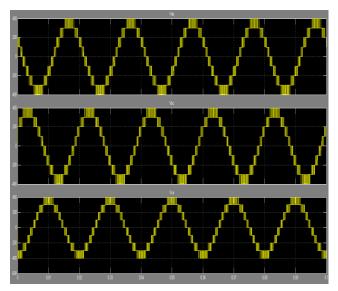

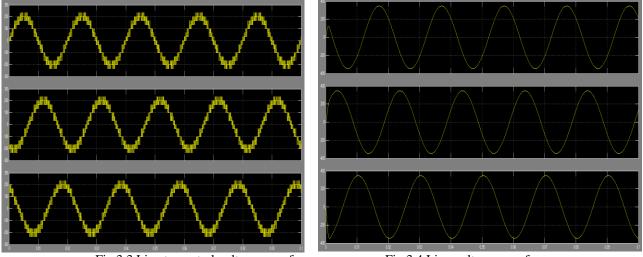

Table 3: 5-Level DCMI voltage levels Fig.3.2 Line to line voltage waveform & their switching States

Fig.3.3 Line to neutral voltage waveform

Fig.3.4 Line voltage waveform

## SEVEN-LEVEL DCMI

A three-phase seven-level diode-clamped inverter is shown in fig.3.5. Each phase is constituted by 12 switches (six switches for upper leg and six switches for lower leg). Switches Sa1 through Sa6 of upper leg form complementary pair with the switches Sa1' to Sa6' lower leg of the same phase.

The complementary switch pairs for phase 'A' are (Sa1, Sa1'), (Sa2, Sa2'),(Sa3, Sa3'),(Sa4, Sa4'),(Sa5, Sa5'),(Sa6, Sa6') and similarly for B and C phases. Clamping diodes are used to carry the full load current.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 5, May 2015

| Sa <sub>1</sub> | Sa <sub>2</sub> | Sa <sub>3</sub> | Sa <sub>4</sub> | Sa <sub>5</sub> | Sa <sub>6</sub> | V <sub>AB</sub>      | V <sub>AO</sub>      |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------------|----------------------|

| 1               | 1               | 1               | 1               | 1               | 1               | V <sub>dc</sub>      | V <sub>dc</sub>      |

| 0               | 1               | 1               | 1               | 1               | 1               | V <sub>dc</sub> / 6  | 2V <sub>dc</sub> /3  |

| 0               | 0               | 1               | 1               | 1               | 1               | 2V <sub>dc</sub> / 6 | V <sub>dc</sub> /3   |

| 0               | 0               | 0               | 1               | 1               | 1               | 3V <sub>dc</sub> / 6 | 0                    |

| 0               | 0               | 0               | 0               | 1               | 1               | 4V <sub>dc</sub> / 6 | -V <sub>dc</sub> / 3 |

| 0               | 0               | 0               | 0               | 0               | 1               | 5V <sub>dc</sub> / 6 | -2V <sub>dc</sub> /3 |

| 0               | 0               | 0               | 0               | 0               | 0               | 0                    | -V <sub>dc</sub>     |

Table 4:Pole Voltage and Line Voltage of a Seven Level Inverter

Fig. 3.5 Simulation circuit of three-phase seven-level diode-clamped inverter

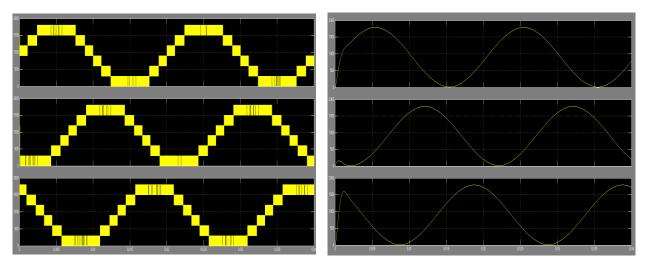

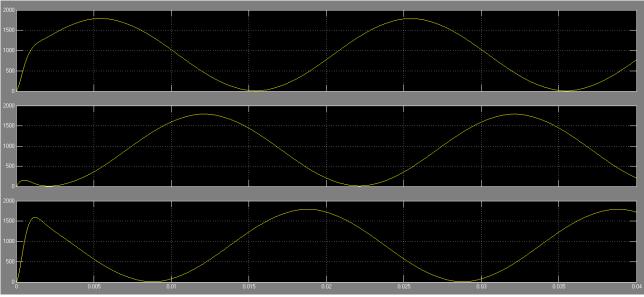

Fig 3.6 Three phase waveform of line to line voltage Fig 3.7 Line to Line filter voltage waveform

(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 5, May 2015

### Fig 3.8 Line to Line filter voltage waveform

| TABLE-III                                |      |

|------------------------------------------|------|

| <b>Diode Clamped Multilevel Inverter</b> | THD% |

|                                          |      |

|                                          |      |

| Five Level                               | 0.28 |

## Comparison of THD Level.

#### VI.CONCLUSION

In this paper, the multilevel topology is presented for industrial application. The multilevel inverters and percentage of total harmonic distortions of several levels of inverter are simulated and compared. The simulated results are 0.28 % THD and 0.19 % THD of five level and seven level inverters respectively. As the number of levels increases the harmonic distortion also decreases.

#### REFERENCES

- Ahmed M. Massoud, Shehab Ahmed, Prasad N. Enjeti, and Barry W. Williams, "Evaluation of a Multilevel Cascaded-Type Dynamic Voltage [1] Restorer Employing Discontinuous Space Vector Modulation", IEEE Trans. on Industrial Electronics, Vol. 57, No7, pp.2398-2410 July 2010.

- A. Nabae, I. Takahashi, and H. Akagi, "A new neutral- point clamped PWM inverter," IEEE Trans. Ind. Applicant. Vol. IA-17, pp. 518-[2] 523, Sept. /Oct. 1981. [2] E. Cengelci,

- B. Wu and F. DeWinter, "Voltage stress on induction motors in medium voltage (2300-6900-V) PWM GTO CSI drives," IEEE Trans. Power [3] Electron., vol. 12, no. 2, pp. 213-220, Mar. 1997.

- B.P.McGrath, Holmes, and T.Meynard, "Reduced PWM Harmonic distortion for multilevel inverter operating over a wide modulation range, [4] " IEEE Trans. Power.Electron., vol.21, no.4, pp.941-949. Jul.2006.

- [5] G.P. Adam, O. Anaya-Lara, G.M. Burt, D. Telford, B.W. Williams, and J.R. McDonald, "Modular multilevel inverter: pulse width modulation and capacitor balancing technique", Published in IET Power Electronics, Vol. 3, Iss. 5, pp. 702-715, 2010. J.M. Erdman, R. J. Kerkman, D.W. Schlegel, and G. L. Skibinski, "Effect of PWM inverters on ac motor bearing current shaft voltage," *IEEE*

- [6] Trans Ind. Appl., vol. 32, no. 2, pp. 250-259, Mar./Apr. 1996.

- Karthikeyan, R., Dr. chenthur, pandian, s., "An algorithm for minimizing THD in multi level inverters with space vector modulation", IEEE [7] Trans. On Industrial Electronics, Vol.3, NO.5, pp3915-3921, 2011.

- Moncef Ben Smida and Faouzi Ben Ammar, "Modeling and DBC-PSC-PWM Control of a Three-Phase Flying-Capacitor Stacked Multilevel [8] Voltage Source Inverter", IEEE Trans. On Industrial Electronics, Vol. 57, No. 7, pp. 2231-2239, July 2010.

- [9] Mohan M. Renge and Hiralal M. Suryawanshi, "Three-Dimensional Space-Vector Modulation to Reduce Common-Mode Voltage for Multilevel Inverter", IEEE Trans. On Industrial Electronics, Vol. 57, No. 7, pp. 2324-2331, July 2010.

- P.Palanivel and SubhransuSekhar Dash, "A FPGA based variable switching frequency multicarrier pulse width modulation for three phase [10] cascaded multilevel inverter," Proc. IEEE INCACEC-2009. Kongu Engineering college, Erode, India, pp.1-4. June 2009.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 5, May 2015

- [11] P.Palanivel, and SubhransuSekhar Dash, "Analysis and implementation of multicarrier pulse width modulation based three phase cascaded multilevel inverter," UPA Int. Journ. Power sys. and Power Electron. Vol2, no.1, pp.70-75. June 2009.

- [12] P.Palanivel, and SubhransuSekhar Dash, "Comparative study of constant switching frequency and variable switching frequency multicarrier pulse width modulation for three phase multilevel inverter," Aca. Pub. Int. Journ. recent trends in Eng. Vol.2, no.1, pp.49-52. June 2009.

- [13] P. W. Hammond, "A new approach to enhance power quality for mediumvoltage AC drives," *IEEE Trans. Ind. Appl.*, vol. 33, no. 1, pp. 202–208, Jan./Feb. 1997.

### BIOGRAPHY

**Ravindrakumar Tiwari** Belongs to UP received his Bachelor of Technology degree fromUtter Pradesh Technical University, Lucknow, in 2013. He is pursuing hisM.Tech in Electrical Engineering. (Power Electronics) from SHIATS, Allahabad, UP-India. His field of interest includes power quality, embedded system, programmable logic controller and electric drives.

**Er. Vinaykumartripathi** belongs to district Allahabad of uttarpradesh. He received his bachelor of technologydegreefrom UCER, allahabad in 2003. Heobtained his M. Tech. in electrical eng. (control &instrumentation) from MNNIT, allahabad, Uttar pradesh in 2006 andpusuingPhd. from samhigginbottom institute of agriculture technology and sciences university (SHIATS), allahabad, up, india. He is having10 years' experience in teaching and presently working as asst. prof.in electrical engineering department, SSET,SHIATS,allahabad. Hisfield of interest includes control and instrumentation,multiphasesystem, power quality and electric drive