(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

# THD Value in a Distribution System Using Seven Level CHB Inverter inside a D-STATCOM

Pranav. M.S<sup>1</sup>, Dhanya Rajan<sup>2</sup> Sruthi.P.K<sup>3</sup>

PG Student [Power Electronics], Dept. of EEE, Vidya Academy of Science and Technology, Thrissur, Kerala, India<sup>1</sup>

PG Student [Power Electronics], Dept. of EEE, Vidya Academy of Science and Technology, Thrissur, Kerala, India<sup>2</sup>

PG Student [Power Electronics], Dept. of EEE, Vidya Academy of Science and Technology, Thrissur, Kerala, India<sup>3</sup>

**ABSTRACT**: This paper shows the THD value in a distribution system using seven level CHB inverter inside a D-STATCOM. The advantages of CHB inverter are low harmonic distortion, reduced number of switches and suppression of switching losses. The D-STATCOM helps to improve power factor and eliminate THD drawn from a Non Linear Diode Rectifier Load(NLDRL).

**KEYWORDS:** DSTATCOM, Level shifted Pulse Width Modulation(LSPWM), CHB multilevel inverter.

### **I.INTRODUCTION**

Now a day's power quality is not reliable because of the presence of large number of non linear loads in the distribution system .Industries have to face power quality(PQ) problems like voltage sags and swells. We have two types of PQ compensators .One is shunt connected compensation device and the other is series connected compensation device. The DSTATCOM using multilevel inverter can reduce output harmonics by increasing the number of output voltage levels.

#### **II.LITERATURE SURVEY**

There are different multilevel converters such as diode-clamp, flying capacitors and cascaded inverters with separate dc sources. Among all these multilevel converters, cascaded inverters require least number of components. Each level has same structure, and there are no extra clamping diodes or voltage balancing capacitors[2].

### **III.CASCADED H-BRIDGE INVERTER(CHB)**

Among various multilevel inverter topologies cascaded H-Bridge topology is widely used as the voltage levels of output can be increased simply by increasing the number of H-Bridges. Different modulation methods can be applied to CHB. There are two types of CHB topologies. They are symmetrical and asymmetrical CHB.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

### IV. SEVEN LEVEL INVERTER BASED D-STATCOM

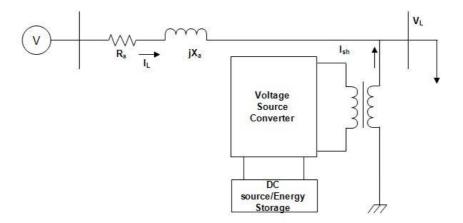

The schematic diagram of a D-STATCOM is shown in Fig .1

Fig. 1 Schematic diagram of a D-STATCOM

A D-STATCOM consists of a Voltage Source Converter (VSC), a dc energy storage device, a coupling transformer connected in shunt to the distribution network through a coupling transformer. The VSC converts the dc voltage across the storage device into a set of three-phase ac output voltages. These voltages are in phase and coupled with the ac system through the reactance of coupling transformer.

#### **V.PWM TECHNIQUES FOR CHB INVERTER**

Here we are adopting Level Shifted Carrier PWM for generating pulses. For a 7-level inverter, there will be three H-Bridges according to the equation L = 2n + 1 where 'L' is the number of levels and 'n' is the number of H-Bridges. So the number of triangular waves is 3.

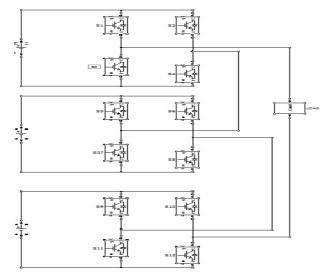

### VI.CIRCUIT DIAGRAM

The circuit diagram of a 7-level CHB inverter is shown in Fig .2

Fig. 2 Seven level CHB inverter

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 3, March 2015

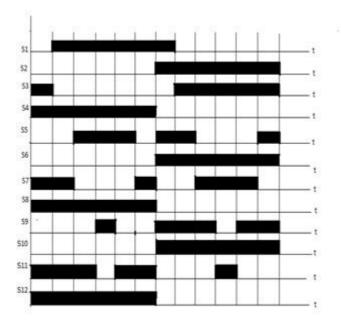

### VII.SWITCHING PATTERN

| VOLTAGE LEVELS | <b>S</b> 1 | <b>S</b> 2 | <b>S</b> 3 | <u>S4</u> | <b>S</b> 5 | <b>S6</b> | <b>S</b> 7 | <b>S</b> 8 | <b>S</b> 9 | S10 | S11 | S12 |

|----------------|------------|------------|------------|-----------|------------|-----------|------------|------------|------------|-----|-----|-----|

| 0              | 0          | 0          | 1          | 1         | 0          | 0         | 1          | 1          | 0          | 0   | 1   | 1   |

| $V_{dc}$       | 1          | 0          | 0          | 1         | 0          | 0         | 1          | 1          | 0          | 0   | 1   | 1   |

| $2V_{dc}$      | 1          | 0          | 0          | 1         | 1          | 0         | 0          | 1          | 0          | 0   | 1   | 1   |

| $3V_{dc}$      | 1          | 0          | 0          | 1         | 1          | 0         | 0          | 1          | 1          | 0   | 0   | 1   |

| 0              | 1          | 1          | 0          | 0         | 1          | 1         | 0          | 0          | 1          | 1   | 0   | 0   |

| $-V_{dc}$      | 0          | 1          | 1          | 0         | 1          | 1         | 0          | 0          | 1          | 1   | 0   | 0   |

| $-2V_{dc}$     | 0          | 1          | 1          | 0         | 0          | 1         | 1          | 0          | 1          | 1   | 0   | 0   |

| $-3V_{dc}$     | 0          | 1          | 1          | 0         | 0          | 1         | 1          | 0          | 0          | 1   | 1   | 0   |

Fig. 3 Switching pattern

### VIII.PULSE PATTERN

Fig. 4 Pulse pattern

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

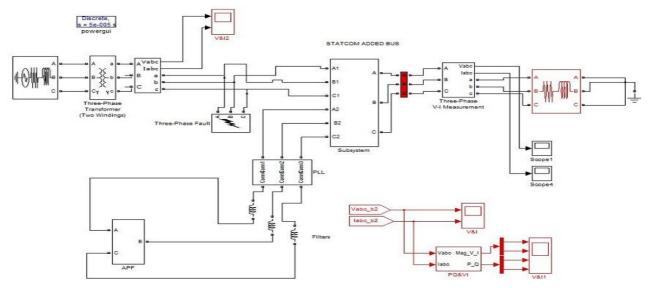

### IX.MATLAB/SIMULINK MODEL AND SIMULATION RESULTS

Fig. 5 Simulation diagram

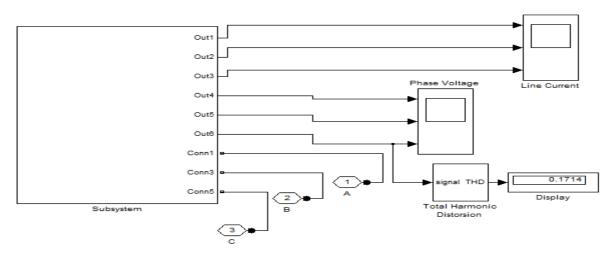

Fig. 6 APF block indicating THD

### **X.CONCLUSION**

The THD value is obtained as 0.1714 as indicated in Fig. 6 . This shows that as voltage level increases, the THD value get reduced.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 3, March 2015

#### REFERENCES

- [1] K.A Corzine. and Y.L Familiant, "A New Cascaded Multi-level HBridge Drive:' IEEE Trans. Power.Electron .• vol. I 7. no. I. pp. I 25-I 3 I. Jan 2002..

- J.S.Lai. and F.Z.Peng "Multilevel converters A new bread of converters, "IEEE Trans. Ind.Appli .• vol.32. no.3. pp.S09-S17. May/ Jun. [2] 1996.Fröhlich, B. and Plate, J. 2000. The cubic mouse: a new device for three-dimensional input. In Proceedings of the SIGCHI Conference on Human Factors in Computing Systems

- [3] T.A.Maynard. M.Fadel and N.Aouda. "Modelling of multilevel converter:' IEEE Trans. Ind.Electron .• vol.44. pp.3S6-364. Jun. 1997.Sannella, M. J. 1994 Constraint Satisfaction and Debugging for Interactive User Interfaces. Doctoral Thesis. UMI Order Number: UMI Order No. GAX95-09398., University of Washington.

- P.Bhagwat. and V.R.Stefanovic. "Generalized structure of a multilevel PWM Inverter:' IEEE Trans. Ind. Appln, Vol.IA-19. no.6, pp. I OS7-[4]

- 1069, Nov.!Dec .. 1983.Brown, L. D., Hua, H., and Gao, C. 2003. A widget framework for augmented interaction in SCAPE.

J. B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp.858-867, August 2002..