(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 3, March 2015

# **Design of Tunable Versatile Filter Using Operational Trans-conductance Amplifier**

Vijay Kumar<sup>1</sup>, Dr. Pardeep Kumar<sup>2</sup>, Dharam Vir<sup>3</sup>

Scholar, Dept of Electronics Engineering, YMCA University of Science & Technology, Faridabad, India.

Asst. Professor, Dept of Electronics Engineering, YMCA University of Science & Technology, Faridabad, India

HOS, Dept of Electronics Engineering, YMCA University of Science & Technology, Faridabad, India

**ABSTRACT**: In this paper, design of a CMOS tunable versatile filter using current conveyor (CC) is presented. The filter is realized at the same time as on the chip is tunable for low pass, band pass, high pass, and elliptical notch filter. The circuit is utilizes two current conveyors, one Operational Trans-conductance Amplifier (OTA), four resistors and two grounded capacitors, ideal for integration. It has only one output terminal and the number of input terminals may be used. Further, there is no further requirement of component matching in the circuit.

KEYWORDS: CMOS, Current Conveyor, OTA, Tunable Versatile Filter

### I. INTRODUCTION

The controlled quadrature optical filters are extremely useful for the circuits of various communication applications such as compact portable spectroscopy and hyper-spectral imaging for real-time, medical diagnostics, surveillance and defence. Now a day's Tunable optical filters having a very wide range of applications from spectroscopy to optical communication networks, to remote sensing as well as biomedical imaging and diagnostics [1]. The bi-layer Polarization Grating (BPG) is a novel diffractive optical element, which allows the implementation of a tunable photo sensitive filter completely un-responsive to input polarization and exhibiting the high peak value of transmittance and a potential in favor of very low cost and compact implementation. Consider the theory and fabrication. Introducing two configurations of a tunable optical filter is based on BPGs and analyzes it in terms of key filter parameters including bandwidth, free-spectral-range, peak transmittance and maximum tuning range [2]. The applications of tunable optical filters are many and varied ranging from astronomy to medicine, education, remote-sensing, optical communications and even the cosmetics industry [3].

#### **II. CURRENT CONVEYOR**

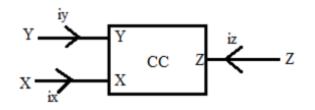

The current conveyor is a basic building block that can be implemented in analog circuit design. This was introduced by Sedra and Smith in 1968 [16]. In recent years, current-mode circuits have emerged as an important class of circuits with Current conveyors can be used in variety of applications ranging from universal and multifunction filters, oscillators etc. Current conveyors can provide larger band-width and are suitable for low voltage applications. Operational amplifier does not perform well where a current output signal is needed and consequently there is an application field for current conveyor circuits [4]. There is no feedback in current conveyor, so it is able to give high frequency behaviour as compared to Op-Amp. In a conventional Op-Amp there is a gain bandwidth product limitation so it is not suitable for high frequency. Block representation of current conveyor is given operations in fig. 1; a current is a three port network. Current conveyor represents emerging class of high performance analog circuit design based on current mode approach. It has simple architecture, wider bandwidth and capability to operate at low voltage developments in the field of current conveyor can be classifieds:-

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

Fig. 1 Block diagram of Current Conveyor

- First Generation Current conveyor, CCI.

- Second Generation Current conveyor, CCII.

- Third conveyor, CCIII. Generation Current

### A. First and Second Generation Current Conveyor

The concept of the current-conveyor was first accessible in 1968. The current-conveyor is proposed as a general building block as with the operational amplifier [7]. Because of the operational amplifier concept has been current since the late, it is difficult to get any other similar concept widely accepted. However, operational amplifiers do not perform well in applications where a current output signal is needed and consequently there is an application field for current. The second generation current conveyor (CCII) is one of the most versatile current-mode building block for many applications, a high impedance input port is preferable in order to avoid loading effect. So, second generation current than the two low impedance input ports of CCI [5] [6]. Since its introduction in 1970, it has been used in a wide range of applications and several circuits have been realized using this block. The CCII can be considered as the basic analog circuit design block because all the active devices can be made of a suitable connection of one or two CCIIs. It is a three terminal device. This current conveyor differs from the first generation current conveyor in a sense that the port Y is a high impedance port i.e. there is no current flowing into port Y. The port Y of the second generation current conveyor is used as a voltage input and port Z is used as a current output port [7]. Whereas, the port X can be used as a voltage output or as a current input port. Therefore, this current conveyor can be used to process both voltage and current signals. There are two types of second generation current conveyors:

• Positive current conveyor (CCII+) in which the currents is and iz have the s direction as in a current mirror.

• Negative current conveyor (CCII-) in which currents ix and iz have the different direction as in current buffer The class AB topology of second generation, to ensure correct operation the bias current Ibias1 and Ibias2 have to be equal. Unlike in the first generation push-pull conveyor, in this conveyor the quiescent current is set directly by to IB by two current sources. Here the current flow through X is nonlinearly divided in to signal path through either an NMOS or a PMOS current mirror which are summed up at port Z. characteristics is nearly 1 [8] [9]. Like CCI, the impedances at X and Y terminals of the CCIII are low. CCIII is very useful in many applications as it provides the current in the floating terminal. The main features of CCIII are low gain errors, high linearity and wide frequency response. In addition, the cascading of CCIII with other circuits is easier owing to high output impedance at Z-terminal, without need of additional active element. It may also be used as the input cell of probes.

#### III. DESIGN ISSUE WITH FILTER

The voltage-mode of filters employing current conveyors has been receiving attention these days. More-over, it is good for a circuit to employ only grounded passive elements especially grounded capacitors and not require passive component-matching conditions therefore it is convenient for fully integrated circuit technology. Second generation current controlled conveyors (CCCIIs) have recently become popular for realizing tunable functions as their port-X tunable resistance can be controlled through the bias current of conveyor. Thus several electronic functions using these devices have been reported in the introduction [10].

#### A. Description of the Circuit

Tank voltage amplitude has an important effect on the phase noise, as emphasized by the presence of qmax in the denominator of the expression for the single-sideband phase noise

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

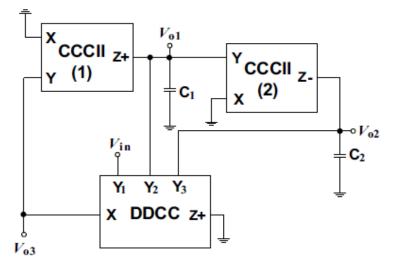

$$\frac{V_{o1}}{V_{in}} = \frac{sC_2G_{X1}}{s^2C_1C_2 + sC_2G_{X1} + G_{X1}G_{X2}}$$

$$\frac{V_{o2}}{V_{in}} = \frac{-G_{X1}G_{X2}}{s^2C_1C_2 + sC_2G_{X1} + G_{X1}G_{X2}}$$

$$\frac{V_{o3}}{V_{in}} = \frac{s^2C_1C_2}{s^2C_1C_2 + sC_2G_{X1} + G_{X1}G_{X2}}$$

Fig 2.Current flow when the stage is switched to one side

It is the power spectral density of the current where it is the rms value of the impulse noise, sensitivity function associated with that noise source,  $q_{max}$  is the maximum signal charge swing, and delta w is the offset frequency from the carrier [11]. A simple expression for the tank amplitude can be obtained assuming that the current in the differential stage switches quickly from one side to another. Fig. 2 shows the current flowing in the complementary cross-coupled differential LC oscillator when it is completely switched to one side. As the tank voltage changes, the direction of the current flow through the tank reverses. The differential pair thus can be modelled as a current source switching between  $I_{t_{a,il}}$  and  $-I_{t_{a,il}}$  in parallel with a resistance, inductance and capacitance (RLC) tank, as shown in Fig. 2 it is the equivalent parallel resistance of the tank [12] [13]..

Email address is compulsory for the corresponding author.

#### B. Rectangular current waveform

At high frequencies, the current waveform may be approximated more closely by a sinusoid due to finite switching time and limited gain. In such cases, the tank amplitude can be better approximated as

$$\omega_o = \sqrt{\frac{G_{X1}G_{X2}}{C_1C_2}} \quad \text{and} \quad Q = \sqrt{\frac{C_1G_{X2}}{C_2G_{X1}}}$$

This mode of operation is referred to as the current-limited regime of operation since, in this regime, the tank amplitude is solely determined by the tail-current source and the tank equivalent resistance. Fig. 2 shows the simulated node voltages as well as the drain currents of the NMOS transistors, M1 and M2, in this regime of operation. The value of L and C are such that the circuit oscillates at 1 GHz [14] [15].

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

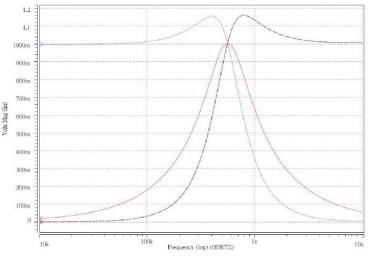

Fig. 3.The high pass, band pass and low pass amplitude-frequency response

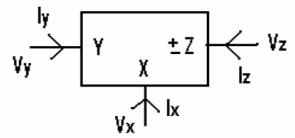

Fig. 4 Block diagram of the filter section

The amplitude approaches the supply voltage because of both NMOS and PMOS pairs that will be enter the triode region at the peaks of the voltage. Also the tail NMOS transistor may spend most (or even all) of its time in the linear region.

#### IV. DESIGN OF FILTER USING CURRENT CONVEYOR

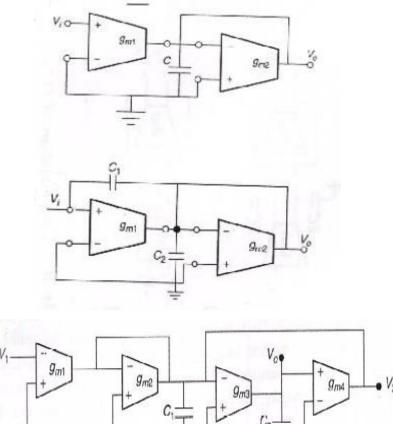

Active filters with current/voltage controllable frequency have a wide range of applications in the signal processing and instrumentation area. The realization on chip MOSFET as voltage controlled resistor. Their contributions and several other research papers may be considered to be motivation for the VLSI industry to make on chip tunable filters. These realizations have small range of variation in the frequency. The OTA-C structure is highly suitable for realizing electronically tunable continuous time filters. A number of voltage mode/current mode OTA-C bi-quard has been reported in the literature. Multiple-input multiple-output (MIMO), multiple-input single-output (MISO) and single-input multiple-output (SIMO) type circuits have also appeared in the literature. A third order current mode oscillator, based on current conveyor and VDTA. The features of the proposed circuits are that the oscillation conditions can be adjusted independently from the oscillation frequency by electronic method. The circuit construction consists of 1DDCC, 1 VDTA, 1 grounded resistor and 2 grounded capacitors. The PSPICE simulation results are shown; the electrical behaviours of the ideal DDCC are represented by the following hybrid matrixes which are in correspondence with the theoretical analysis.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

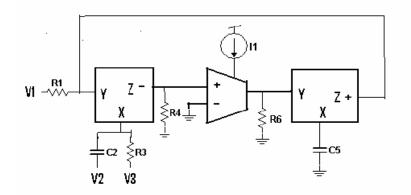

Fig. 5 Proposed circuit using current conveyor

#### 1) Design using CCIIs:

The circuit symbol of CC-II is shown in Fig. 4, where VP and VN are the input terminals, Z and X is the output ones. Hence, Z is the current output terminal; current through Z terminal follows the difference of the voltages at VP and VN terminals by trans-conductance of gm1. The voltage vZ on Z terminal is transferred into current using transconductance gm2, which flows into output terminal X.

$$V_{out} = \frac{1}{D(s)} \begin{pmatrix} s^2 C_2 C_5 R_1 R_3 R_4 R_6 g_m V_2 + R_3 V_1 + \\ s C_5 g_m R_1 R_4 R_6 V_3 \end{pmatrix}$$

Where

$$D(s) = s^{2}C_{2}C_{5}g_{m}R_{1}R_{3}R_{4}R_{6} + sC_{5}g_{m}R_{1}R_{4}R_{6} + R_{3}$$

The gm1 and gm2 are tuned by IB1 and IB2, respectively. In general, CDTA can contain an arbitrary number of x terminals, providing currents IX of both directions. All terminals of VDTA exhibit high impedance values. The characteristics of the ideal VDTA are represented by the following hybrid matrix: If the VDTA is realized using CMOS technology, gm1 and gm2 can be respectively written as

$$g_{m1} = \sqrt{kI_{B1}} ,$$

and

$$g_{m2} = \sqrt{kI_{B2}} \; .$$

Here k is the physical trans-conductance parameter of the CMOS transistor. IB1 and IB2 are the bias current used tocontrol the gm1 and gm2, respectively.

### (An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

| TABLE I.             | VARIOUS FILTER RESPONSES |    |       |

|----------------------|--------------------------|----|-------|

| <b>Filter</b> \Input | $V_1$                    | V2 | $V_3$ |

| Low-pass             | 1                        | 0  | 0     |

| High-pass            | 0                        | 1  | 0     |

| Band-pass            | 0                        | 0  | 1     |

| Notch                | 1                        | 1  | 0     |

$$\omega_{0} = \sqrt{\frac{1}{R_{1}R_{4}R_{6}C_{2}C_{5}g_{m}}}$$

$$\frac{\omega_{0}}{Q} = \frac{1}{R_{3}C_{2}}$$

$$Q = R_{3}\sqrt{\frac{C_{2}}{g_{m}R_{1}R_{4}R_{6}C_{5}}}$$

#### 2) General structure of CCIIs:

The oscillator is designed by cascading an inverting second order low-pass filter and the lossless integrators as systematically. Fig. 4, we will receive the characteristic equation as

$$s^3 + bs^2 + as + ck = 0$$

The condition of oscillation (OC) and frequency of oscillation (FO) can be written as

$$OC: ab = ck$$

and

$\omega_{osc} = \sqrt{a}$

From Eq. (5), if a = c, the oscillation condition and oscillation frequency can be adjusted independently, which are the oscillation condition able to be controlled by b and k, while the oscillation frequency can be tuned by a.

#### 3) Structure of proposed Filter

The completed 3rd current-mode quadrature oscillator is shown in Fig. 4. The condition of oscillation and frequency of oscillation can be written as

$$\frac{1}{C_1 R} = \frac{g_{m2}}{C_3},$$

and

$$\mathcal{O}_{osc} = \sqrt{\frac{g_{m1}}{C_1 C_2 R}} \,.$$

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 3, March 2015

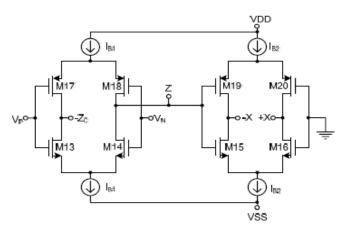

Fig. 6 Proposed current-mode oscillator

If m1 B1 g = kI, m2B2 g = kI and 1 2 3 C = C = C = C, the condition of oscillation and frequency of oscillation can be rewritten as

$$\frac{1}{R} = \sqrt{kI_{B2}} ,$$

and

$$\omega_{osc} = \frac{1}{C} \sqrt{\frac{(kI_{B1})^{\frac{1}{2}}}{R}} .$$

It is obviously found that, the condition of oscillation and frequency of oscillation can be adjusted independently; which are the oscillations of oscillation can be controlled by setting IB2, while the frequency of oscillation can be tuned by setting IB1. From the circuit in Fig. 4, the current transfer function from Io1 to Io2 is

$$\frac{I_{o2}(s)}{I_{o1}(s)} = \frac{g_{m1}}{sC_2}$$

For sinusoidal steady state, becomes

$$\frac{I_{o2}(j\omega)}{I_{o1}(j\omega)} = \frac{g_{m1}}{\omega C_2} e^{-j90^\circ}.$$

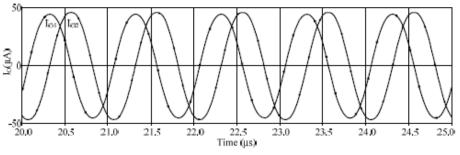

The phase difference  $\varphi$  between Io1 and Io2 is  $\varphi = -90^{\circ}$  ensuring that the currents Io2 and Io1 are in quadrature.

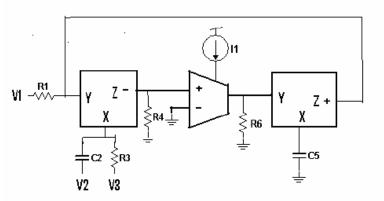

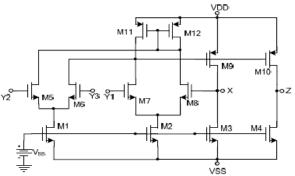

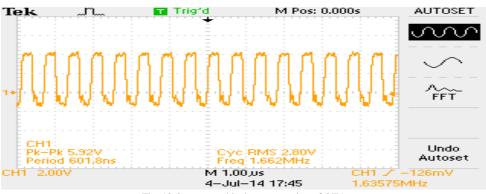

#### V. OUTPUT OF PROPOSED FILTER

The working of the proposed oscillator has been verified in PSpice simulation software. Internal constructions of DDCC and VDTA used in simulation are respectively shown in Fig. 6 and 7. The PMOS and NMOS transistors have been simulated by respectively using the parameters of a 0.25 $\mu$ m TSMC-CMOS technology. The transistor aspect ratios of PMOS and NMOS transistor are indicated in Table I. The circuit was biased with ±1.25V supply voltages, VBB=-0.55V, C1=C2=C3=50pF, IB1=IB2=60 $\mu$ A and R=3.5k $\Omega$ . This yields simulated oscillation frequency of 1MHz. Fig. 8 shows simulated quadrature output waveforms. Fig. 8 shows the simulated output spectrum, where the total harmonic distortion (THD) is about 2.95%. The quadrature relationship between the generated waveforms has been verified using Lissagous figure and shown in Fig. 8. The power consumption is approximately1.76mW.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

| TABLE I<br>DIMENSIONS OF THE TRANSISTORS |        |        |  |  |

|------------------------------------------|--------|--------|--|--|

| Transistor                               | W (μm) | L (µm) |  |  |

| M <sub>1</sub> -M <sub>4</sub>           | 3      | 0.25   |  |  |

| M <sub>5</sub> -M <sub>8</sub>           | 1      | 0.25   |  |  |

| M <sub>9</sub> -M <sub>10</sub>          | 10     | 0.25   |  |  |

| $M_{11}$ - $M_{12}, M_{13}$ - $M_{16}$   | 5      | 0.25   |  |  |

| M <sub>17</sub> -M <sub>20</sub>         | 8      | 0.25   |  |  |

Fig. 7 Internal construction of the CMOS DDCC

Fig. 8 Internal construction of the CMOS VDTA

Fig. 9 The simulation result of quadrature outputs

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

### VI. RESULT

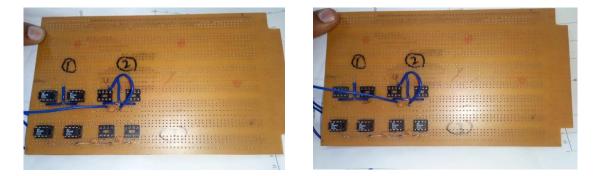

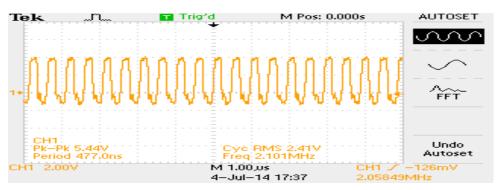

The complete circuit is simulated using commercially available AD844 and LM13700. The AD844 is used for the realization of CCII+ and CCII-. Table 1 displays the simulation result for the proposed filter. The circuit is designed for  $\omega 0 = 8.7$  KHz and Q=0.12 by considering R1 = R4 = R6 = 10K $\Omega$ , C2 = C5 = 10nF, R3 = 14K $\Omega$  and gm=13.2mS. The theoretical results have been are verified to match with simulation result. Figure 3 shows that the quality factor of the notch filter is very high. It is due to the transfer function of the notch filter is having complex conjugate zeros with zero real values. Figure 8 shows the cutoff/center frequency of the filter with respect to the changes in bias current of the OTA. The response is showing the when the bias current is higher than the output current of the OTA than the frequency variation is linear and circuit will be stable. The report which is obtained with the help of simulation contains different sections, of all the sections only the parameters obtained in the final report are shown.

Fig. 10 Experimental designed of OTA

(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 3, March 2015

Fig. 11 Experimental designed of OTA on PCB

Table 1 Results for the output obtained

| Frequency MHz | V <sub>Output</sub> (dB) | $Gain(dB)=V_0/V_1=20 \log V_0/V_1$ |

|---------------|--------------------------|------------------------------------|

| 80            | 0.001                    | -60                                |

| 82            | 0.003162                 | -50                                |

| 84            | 0.01                     | -40                                |

| 86            | 0.031623                 | -30                                |

| 88            | 0.1                      | -20                                |

| 90            | 0.316228                 | -10                                |

| 92            | 1                        | 0                                  |

### **Output Graphical representation of OTA**

Fig. 12 Output graphical representation of OTA

Fig. 13 Output graphical representation of OTA

#### (An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

### VII. CONCLUSION

The circuit proposed in this thesis generates low-pass, high pass, band-pass and notch filter using two current conveyors, four resistors and two capacitors. The circuit provides more number of filter realizations at the single output terminal. In addition of this proposed circuit does not have any matching constraint/cancellation condition. The circuit employs' grounded capacitor, suitable for IC fabrication. The circuit enjoys the othogonality between the cut-off frequency and the bandwidth. The OTA is linearly tunable when the bias current is higher than the output current. It has low sensitivities figure of both active and passive components.

#### REFERENCES

- E. Sanchez-sinnencio, R. L. Geiger and H. Nevarez-Lozano., "Generation of Continuous Time Two Integrator Loop OTA filter structures," *IEEE Trans. Circuits and Syst.*, Vol. 35, pp. 936-946, 1988.

- [2] Chun-Lung Hsu, Mean-Hom Ho, Yu-Kuan Wu and Ting-Hsuan Chen, "Design of Low-Frequency Low-Pass Filters for Biomedical Applications," *IEEE, Circuits and Systems*, pp. 690-695, December 2006.

- [3] Baidyanath Ray, "Design of OTA based Field Programmable Analog Array", IEEE, VLSI Design, pp. 494-498, January 2000.

- [4] Randall L. Geiger, Edgar Sánchez-Sinencio "Active Filter Design Using Operational Transconductance Amplifiers: A Tutorial," *IEEE Circuits and Devices Magazine*, vol. 1, pp.20-32, March 1985.

- [5] J. W. Horng, C. K. Chang, and J. M. Chu, "Voltage-mode universal biquadratic filter using single current-feedback amplifier," *IEICE Trans. Fundamentals*, vol. E85–A, no. 8, pp. 1970–1973, 2002.

- [6] E. Brunn., "CMOS high speed, high precision current conveyor and current-feedback amplifier structures," Int. J. Electron., Vol. 74, No.1, pp.93-100, 1993.

- [7] T. Thosdeekoraphat, S. Summart, C. Saetiaw, S.Sanatalunai and C. Thongsopa, Resistor-less current mode universal biquad filter using CCTAs and grounded capacitors, *World Academy Of Science, Eng. and Tec.* 69, 559-563, (2012).

- [8] T. R. Viswanathan., "CMOS transconductance element," Proc. IEEE., Vol. 74, pp. 222-224, 1986.

- [9] Prasant K. Mahapatra, Manjeet Singh, Neelesh Kumar, "Realization of active filters using operational transconductance amplifier (OTA)", *Journal of the Instrument Society of India*, pp 1-9.

- [10] J. Ramirez-Angulo, S. Thoutam, A. Lo'pez-Martin and R.G. Carvajal., "Low-voltage CMOS analogue four quadrant multiplier based on flipped voltage followers," *Electron. Letters*, Vol. 39, No.25, pp. 1771-1772, Dec., 2003.

- [11] Sajai Vir Singh, Sudhanshu Maheshwari "Current-Processing Current-Controlled, Universal BiquadFilter", Radio Engineering, Vol.21, no1, April 2012

- [12] A. Fabre, "Third-generation current conveyor: a new helpful active element," *Electronics Letters*, vol. 31, pp. 338–339, 1995.

- [13] C. M. Chang, T. H. Huang, S. H. Tu, C. L. Hou, and J. W. Horng, "Universal active current filter using single second-generation current controlled conveyor," *Int. J. of Circ., Syst. and Sign. Proc.*, vol. 1, pp. 194–198, 2007.

- [14] A.Fabre, O. Saaid, F. Wiest, and C. Baucheron, High frequency applications based on a new current controlled conveyor, *IEEE Transactions*. *Circuits System-I*, vol. 43,no. 2, pp. 82-90.

- [15] M.Y.Yasin, BalGopal "High Frequency Oscillator Design Using a Single 45 nm CMOS Current Controlled Current Conveyor (CCCII+) with Minimum Passive Components" *Circuits and Systems*, 2011, 2, 53-59, doi:10.4236/cs.2011.22009.

- [16] A. Sedra and K. C. Smith, "Design of computer controllable instrumentation." *presented at the 6th Nstl. Conf. of the Computer Sot. of Canada*, June 1968.

#### BIOGRAPHY

Vijay Kumar received the M.Tech Degree form YMCAUST Faridabad (Haryana) and B.E Degree in Electronics and Communication Engg. From Jamia Millia Islamia (Central University) New Delhi, 2014, 2010 respectively. In 2000 he started his carrier as Technical Assistant in the field of electronics. Since 2006 he is part of YMCA University of Science & Technology, Faridabad.

Dr. Pardeep Kumar received the M.Tech Degree from MDU Rothak (Haryana) and B.E Degree in Electronics and Communication Engg. From Jamia Millia Islamia (Central University), New Delhi 2003, 2010 respectively. In 1991 he started his carrier as Technical Assistant in the field of electronics. Since 1994 he is part of YMCA University of Science & Technology, Faridabad.

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 3, March 2015

DharamVir received the M.Tech Degree form MDU Rothak (Haryana) and B.E Degree in Electronics and Communication Engg. From Jamia Millia Islamia (Central University), New Delhi 2008, 2004 respectively. In 1989 he started his carrier as R&D Engineer in the field of computers and networking. Since 1992 he is part of YMCA University of Science & Technology and presently working as Head of Section (Electronics & Inst. Control) in the Department of Electronics Engineering.