> (An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 7, July 2015

# A Modified Three Phase Four-Wire UPQC Topology with Reduced DC-Link Voltage Rating

M. Nandhagopal<sup>1</sup>, S.Sundarrajan<sup>1</sup>, K.S.S. Prasad<sup>2</sup>

PG Scholar, Dept. of EEE, Bharath University, Chennai, Tamil Nadu, India<sup>1</sup>

Assistant Professor, Dept. of EEE, Bharath University, Chennai, Tamil Nadu, India<sup>2</sup>

**ABSTRACT:** This circuit consists of capacitor in series with the interfacing inductor of the shunt active filter. The series capacitor enables reduction in dc-link voltage requirement of the shunt active filter and simultaneously compensating the reactive power required by the load, so as to maintain unity power factor, without compromising its performance. This allows us to match the dc-link voltage requirements of the series and shunt active filters with a common dc link capacitor. Further, in this topology, the system neutral is connected to the negative terminal of the dc bus.. This will avoid the requirement of the fourth leg in VSI of the shunt active filter and enables Independent control of each leg of the shunt active filter, and the system neutral is connected to the negative terminal of the dc-link voltage to avoid the requirement of the fourth leg in the voltage source inverter (VSI) of the shunt active filter. The average switching frequency of the series capacitor and VSI parameters have been discussed in the paper. A simulation study of the proposed topology has been carried out using PSCAD simulator, and the results are presented. Experimental studies are carried out on three-phase UPQC prototype to verify the proposed topology.

# I. EXISTING SYSTEM

In existing system the three phase three WIRE UPQC has used. Mainly Voltage rating of dc-link capacitor largely influences the compensation performance of an active filter.[1-3] So the dc-link voltage for the shunt active filter has much higher value than the peak value of the line-to-neutral voltage.

## EXISTING SYSTEM METHODOLOGY

The three phase three wires UPQC system used for compensation of power quality issues.

## **DISADVANTAGES OF EXISTING SYSTEM:**

In this method the UPQC which requires more rating of series and shunt active filters. Additionally to maintain the Low harmonics level by adding passive filters.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 7, July 2015

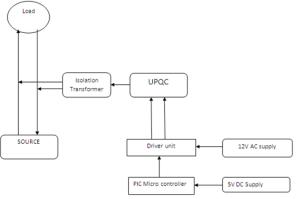

## **BLOCK DIAGRAM OF PROPOSED SYSTEM:**

Figure.1. Proposed System Block Diagram

# II. COMPONENTS IN THE PROPOSED SYSTEM

#### BASIC CONFIGURATION OF UPQC

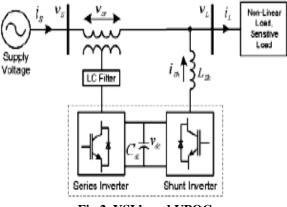

UPQCs consist of combined series and shunt APFs for simultaneous compensation of voltage and current.[4]The series APF inserts a voltage, which is added at the point of common coupling (PCC) such that the load end voltage remains un affected by any voltage disturbance, whereas, the shunt APF is most suitable to compensate for load reactive power demand and unbalance, to eliminate the harmonics from supply current, and to regulate the common DC link voltage and to supply current. The UPQC has two distinct parts:

Power circuit formed by series and shunt PWM Converters

UPQC controller

#### III. METHODOLOGY

Three phase four wire UPQC system for control the Power Quality issues.

## **PRINCIPLE:**

The UPQC is a combination of series and shunt active filters connected in cascade via a common DC link capacitor.[5] The main purpose of a UPQC is to compensate for supply voltage power quality issues such as, sags, swells, unbalance, flicker, harmonics, and for load current power quality problems such as, harmonics, unbalance, reactive current and neutral current. A UPQC that combines the operations of a Distribution Static Compensator (DSTATCOM) and Dynamic Voltage Regulator (DVR) together.[6]

Fig.2. VSI based UPQC

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 7, July 2015

## IV. CONSTRUCTION

Ultra capacitor consists of a porous electrode, electrolyte and a current collector (metal plates). There is a membrane, which separates, positive and negative plated is called separator. The following diagram shows the ultra capacitor module by arranging the individual cell.[7]

## WORKING:

• Alternating current (AC) is used for power line transmission and for high power devices like appliances and lights.

• The characteristics of AC make it ideal for transmission over long lines and for delivering large amounts of power for relatively unregulated uses, such as generating heat and light.

• Lower power appliances and devices require the closely regulated control of direct current power (DC). As a normal house is supplied with AC, it must be converted to DC for many uses.

• Two high power AC networks can be connected via a DC link, as that does not require both networks to be synchronized in frequency and phase, which is often difficult or impossible. [8]

• DC link exists between a rectifier and an inverter, for example, in a phase converter. On one end, the utility connection is rectified into a high voltage DC. On the other end, that DC is switched to generate a new AC power waveform. [9]

• It's a link because it connects the input and output stages. The term "DC link" is also used to describe the decoupling capacitor in the DC link. I assume that this is what you're asking about.

• The switching network on the output side generates very large transients at the switching frequency.

• The DC link capacitor helps to keep these transients from radiating back to the input. This can also help prevent the switching network from oscillating or triggering inadvertently at an inappropriate moment and causing a short. [10]

• Additionally, if the input is not multiple-phase, the capacitor helps provide a source of energy when the input waveform is near zero.[11]

## PERFORMANCE OF DRIVER UNIT

• The input to a TTL circuit is always through the emitter(s) of the input transistor, which exhibits a low input resistance.

• The base of the input transistor, on the other hand, is connected to the Vcc line, which causes the input transistor to pass a current of about 1.6 mA when the input voltage to the emitter(s) is logic '0', i.e.,near ground. [12]

• Letting a TTL input 'float' (left unconnected) will usually make it go to logic '1', but such a state is vulnerable to stray signals, which is why it is good practice to connect TTL inputs to Vcc using 1 kohm pull-up resistors.

• The most basic TTL circuit has a single output transistor configured as an inverter with its emitter grounded and its collector tied to Vcc with a pull-up resistor, and with the output taken from its collector.

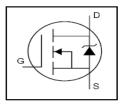

## **POWER MOSFET:**

The MOSFET, or Metal-Oxide-Semiconductor Field-Effect Transistor is far the most common field effect transistor in both digital and analog circuits. The MOSFET is composed of a channel of n-type or p-type semiconductor material, and is accordingly called an NMOSFET or a PMOSFET. Unfortunately, many semiconductors with better electrical properties than silicon, such as gallium arsenide, do not form good gate oxides and thus are not suitable for MOSFETs.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 7, July 2015

## Fig 3. Power MOSFET

## FEATURES OF POWER MOSFET:

• Power MOSFET has lower switching losses but its on-resistance and conduction losses are more.

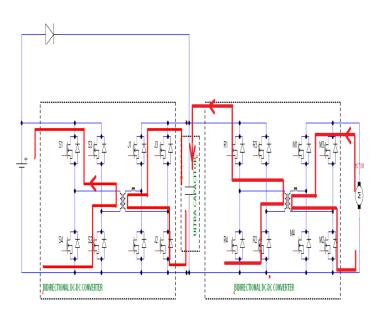

# **BIDIRECTIONAL DC-DC CONVERTER:**

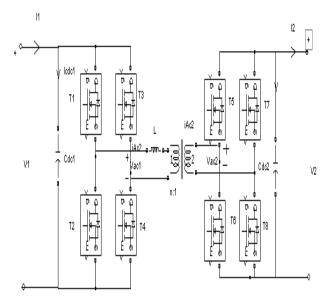

The bidirectional dc to dc converter along with energy storage has become a promising option for many power related system including power related systems and hybrid electric vehicles. [13-14] It is not only reducing the cost and improving the efficiency. MOSFET is the switches used in the converter. In this  $T_1,T_2,T_3,T_4$  are the switches used in the inverter bridge side and  $T_5,T_6,T_7,T_8$  are the switches used in the rectifier side . Where L is the leakage inductance used for the soft switching and the values for the leakage inductance is 27 µH, the capacitorsC<sub>dc1</sub>,C<sub>dc2</sub>used for the filtering purpose

Fig 4. Bidirectional dc-dc converter circuit diagram

• In ,Dual active-bridge bi-directional dc-dc converter, the one full bridge serves as High Frequency (HF) inverter and the other full bridge serves as rectifier.

(An ISO 3297: 2007 Certified Organization)

## Vol. 4, Issue 7, July 2015

## V. OPERATING PRINCIPLE

The operating principle of the proposed system can be explained by the following modes of operation

# MODES OF OPERATION MODE1:

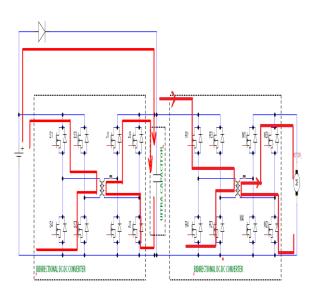

Fig 5. Energy flow of the Acceleration mode phase I

In Mode1 energy from the battery is directly supplied to Dual active bridge converter2(DAB2) and from DAB2 the energy is supplied to the motor and it starts running, meanwhile charging takes place in Ultra capacitor from battery through DAB1.'

# MODE 2

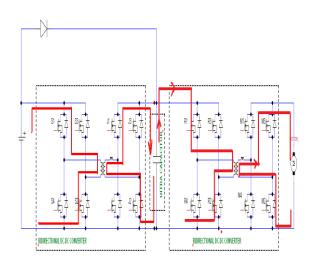

Fig 6. Energy flow of the Acceleration mode phase II

In Mode2 the motor draws energy from Ultra capacitor through Dual active birdge2. In this mode vehicle speed is increased.

(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 7, July 2015

MODE 3

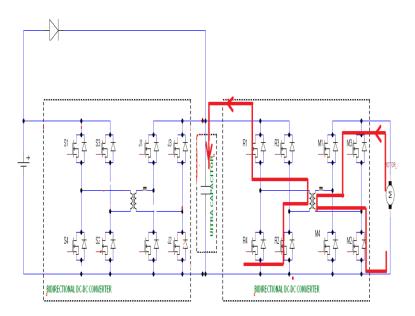

Fig 7. Energy flow of Regenerative braking phase I

InMode 3 theexcess energy from the motor is stored in ultra capacitor through Dual active bridge 2.

MODE 4

Fig 8. Energy flow of Regenerative braking phase II

In this mode when ultra capacitor is fully charged the energy from the motor is stored in battery through Dual active bridge1.

V<sub>in</sub> is the input voltage

(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 7, July 2015

$V_0 = 6V$

## VI. SIMULINK RESULTS

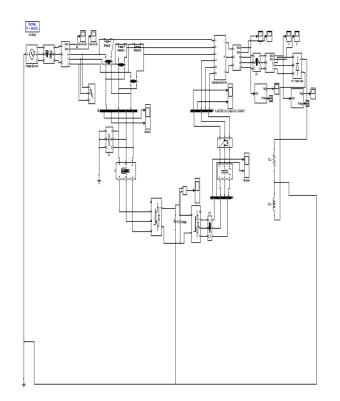

## SIMULINK MODEL

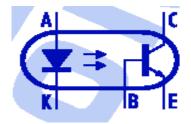

## **OPTOCOUPLERS**

The most important parameter for most Optocouplers is their transfer efficiency, usually measured in terms of their current transfer ratio or CTR. This is simply the ratio between a current change in the output transistor and the current change in the input LED which produced it. Typical values for CTR range from 10% to 50% for devices with an output phototransistor and up to 2000% or so for those with a Darlington transistor pair in the output. Note, however that in most devices CTR tends to vary with absolute current level. Typically it peaks at a LED current level of about 10mA, and falls away at both higher and lower current levels. Other optocoupler parameters include the output transistor's

Fig 9. Simulink Diagram

maximum collector-emitter voltage rating VCE (max), which limits the supply voltage in the output circuit; the input LED maximum current rating IF (max), which is used to calculate the minimum value for its series resistor; and the Optocouplers bandwidth, which determines the highest signal frequency that can be transferred through it ó determined mainly by internal device construction and the performance of the output Phototransistor.

Fig 10. Optocoupler

ISSN (Print) : 2320 – 3765 ISSN (Online): 2278 – 8875

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 7, July 2015

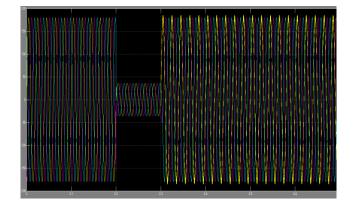

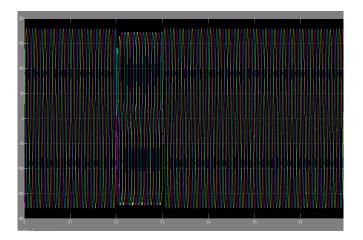

SIMULATION RESULT:

Fig 11.Output voltage with voltage sag

Fig 12.Output voltage after eliminating voltage sag

# VII. CONCLUSION

A modified UPQC topology for three-phase four-wire system has been proposed in this paper, which has the capability to compensate the load at a lower dc-link voltage under non stiff source. Design of the filter parameters for the series and shunt active filters is explained in detail. The proposed method is validated through simulation and experimental studies in a three-phase distribution system with neutral-clamped UPQC topology (conventional). The proposed modified topology gives the advantages of both the conventional neutral-clamped topol ogy and the four-leg topology. Detailed comparative studies are made for the conventional and modified topologies. From the study, it is found that the modified topology has less average switching frequency, less THDs in the source currents, and load voltages with reduced dc-link voltage as compared to the conventional UPQC topology.

# VIII. HARDWARE MODELLING

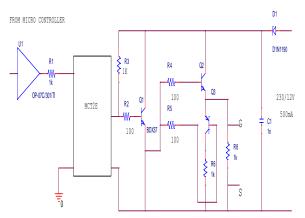

## **DRIVER CIRCUIT**

The IR2110 are high voltage, high speed power MOSFET and IGBT drivers with HARD independent high and low side referenced output channels. Proprietary HVIC and latch immune CMOS technologies enable ruggedized monolithic construction.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 7, July 2015

## **Circuit Diagram Of The Control Circuit**

#### **Fabrication Of Driver Circuit**

### ARCHITECTURE OF PIC16F877A

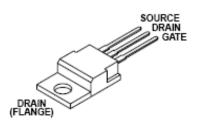

Make : FAIRCHILD Vdc : 500V Id :continuous : AT 25 °C , 20A Idm: Drain current- pulsed :80A Vgss : +-30V Iar avalanche current : 20 A Tl : maximum lead temp: 300 °c

#### **Clock Management**

- 2% internal oscillator

- Programmable PLL and oscillator clock sources

- Fail-Safe Clock Monitor (FSCM)

- Independent Watchdog Timer

- Low-power management modes

- Fast wake-up and start-up

#### **Core Performance**

- Up to 40 MIPS 16-bit dsPIC33F CPU

- Two 40 bit wide accumulators

- Single-cycle (MAC/MPY) with dual data fetch

- Single-cycle MUL plus hardware divide

- Motor Control PWM

- Up to four PWM generators with eight outputs

- Dead Time for rising and falling edges

- 25 ns PWM resolution

- PWM support for Motor Control: BLDC, PMSM, ACIM, and SRM

- Programmable Fault inputs

- Flexible trigger for ADC conversions and configurations.

ISSN (Print) : 2320 – 3765 ISSN (Online): 2278 – 8875

# International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 7, July 2015

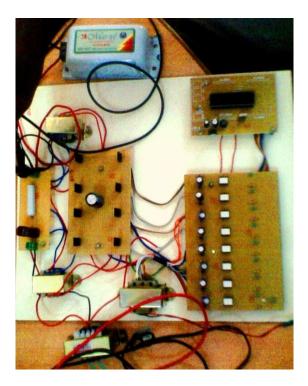

HARDWARE CIRCUIT

IX. CONCLUSION

A modified UPQC topology for three-phase four-wire system has been proposed in this paper, which has the capability to compensate the load at a lower dc-link voltage under non stiff source. Design of the filter parameters for the series and shunt active filters is explained in detail. The proposed method is validated through simulation and experimental studies in a three-phase distribution system with neutral-clamped UPQC topology (conventional). The proposed modified topology gives the advantages of both the conventional neutral-clamped topol ogy and the four-leg topology. Detailed comparative studies are made for the conventional and modified topologies. From the study, it is found that the modified topology has less average switching frequency, less THDs in the source currents, and load voltages with reduced dc-link voltage as compared to the conventional UPQC topology.

#### REFERENCES

[1] M. Bollen, Understanding Power Quality Problems: Voltage Sags and Interruptions. New York: IEEE Press, 1999.

[2]Subha Palaneeswari M., Abraham Sam Rajan P.M., Silambanan S., Jothimalar, "Blood lead in end-stage renal disease (ESRD) patients who were on maintainence haemodialysis", Journal of Clinical and Diagnostic Research, ISSN : 0973 - 709X, 6(10) (2012) pp.1633-1635.

[3]Sharmila S., Rebecca L.J., Saduzzaman M., "Effect of plant extracts on the treatment of paint industry effluent", International Journal of Pharma and Bio Sciences, ISSN : 0975-6299, 4(3) (2013) pp.B678-B686.

[4] S. V. R. Kumar and S. S. Nagaraju, "Simulation of DSTATCOM and DVR in power systems," ARPN J. Eng. Appl. Sci., vol. 2, no. 3, pp. 7–13, Jun. 2007.

[5]Jeyanthi Rebecca L., Dhanalakshmi V., Sharmila S., "Effect of the extract of Ulva sp on pathogenic microorganisms", Journal of Chemical and Pharmaceutical Research, ISSN: 0975 - 7384, 4(11) (2012) pp.4875-4878.

[6]Sharmila D., Saravanan S., "Efficacy of lead on germination growth and morphological studies of Horse Gram (Dolichos biflorus Linn)", Journal of Chemical and Pharmaceutical Research, ISSN: 0975 – 7384, 4(11) (2012) pp.4894-4896.

[7] B. T. Ooi, J. C. Salmon, J. W. Dixon, and A. B. Kulkarni, "A three phase controlled-current PWM converter with leading power factor, "IEEE Trans. Ind. Appl., vol. IA-23, no. 1, pp. 78–84, Jan. 1987.

[8] Y. Ye, M. Kazerani, and V. Quintana, "Modeling, control and implementation of three-phase PWM converters," IEEE Trans. Power Electron., vol. 18, no. 3, pp. 857–864, May 2003.

[9] R. Gupta, A. Ghosh, and A. Joshi, "Multiband hysteresis modulation and switching characterization for sliding-mode-controlled cascaded multilevel inverter," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2344–2353,Jul. 2010.

(An ISO 3297: 2007 Certified Organization)

## Vol. 4, Issue 7, July 2015

[10] S. Srikanthan and M. K. Mishra, "DC capacitor voltage equalization in neutral clamped inverters for DSTATCOM application," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2768–2775, Aug. 2010.

[11]Saduzaman M., Sharmila S., Jeyanthi Rebecca L., 'Efficacy of leaf extract of Moringa oleifera in treating domestic effluent", Journal of Chemical and Pharmaceutical Research, ISSN: 0975-7384, 5(2) (2013) pp.139-143.

[12] R. Gupta, A. Ghosh, and A. Joshi, "Switching characterization of cascaded multilevel-inverter-controlled systems," IEEE Trans. Ind. Electron., vol. 55, no. 3, pp. 1047-1058, Mar. 2008.

[13] B. Singh and J. Solanki, "Load compensation for diesel generator-based isolated generation system employing DSTATCOM," IEEE Trans. Ind. Electron., vol. 47, no. 1, pp. 238-244, Jan./Feb. 2011.

[14] R. Gupta, A. Ghosh, and A. Joshi, "Characteristic analysis for multi sampled digital implementation of fixed-switching-frequency closed loop modulation of voltage-source inverter," IEEE Trans. Ind. Electron., vol. 56, no. 7, pp. 2382–2392, Jul. 2009. [15] Lingeswaran, K., "Microcontroller-based MPPT control for standalone PV system with sepic converter", Middle - East Journal of Scientific

Research, v-20, i-8, pp:945-950, 2014.

[16] Thamarai, P., Karthik, B., Kumaran, E.B., "Optimizing 2:1 MUX for low power design using adiabatic logic", Middle - East Journal of Scientific Research, v-20, i-10, pp:1322-1326, 2014.

[17] Jayalakshmi, V., "Wireless sensor network for performance monitoring of electrical machine", Middle - East Journal of Scientific Research, v-20, i-8, pp:996-999, 2014.

[18] Prasad, K.S., "A design towards smart batteries", Middle - East Journal of Scientific Research, v-20, i-10, pp:1318-1321, 2014.

[19] Vijayaragavan, S.P., Karthik, B., Kiran Kumar, T.V.U., "Privacy conscious screening framework for frequently moving objects", Middle - East Journal of Scientific Research, v-20, i-8, pp:1000-1005, 2014.