(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 1, January 2015

# Improved Transformerless Inverter with Common-Mode Leakage Current Elimination for A Photo Voltaic Grid Connected Power System

B .Indhira Priyadharsini<sup>1</sup>, S. UmaMageswaran<sup>2</sup>

PG Student [EST], Dept. of EEE, Saveetha Engineering College, Thandalam, Kancheepuram, Tamilnadu, India<sup>1</sup> Assistant Professor, Dept. of EEE, T.J.S Engineering College, Peruvoyal, Gummidipoondi, Tamilnadu, India<sup>2</sup>

**ABSTRACT:** In order to eliminate the common mode leakage current in transformer less PV system, the concept of virtual DC bus is proposed in this project. By connecting the grid neutral line directly to the negative pole of the DC bus, the stray capacitance between the PV panels and the ground is bypassed. The CM ground leakage current can be suppressed completely. Virtual DC bus is created to provide the negative voltage level for the negative AC grid current generation. The virtual DC bus is realized with the switched capacitor technology that uses less number of elements. Therefore, the power electronic cost can be reduced. This topology can be modulated with the unipolar SPWM to reduce the output current ripple. A smaller filter inductor can be used to reduce the size and magnetic losses. The simulation result of the proposed topology using MATLAB/SIMULINK is presented.

**KEYWORDS:** Common mode (CM) current, photovoltaic (PV) system, switched capacitor, Transformerless inverter, unipolar sinusoidal pulse width modulation (SPWM), virtual dc bus.

### **I.INTRODUCTION**

Renewable energy sources become a more and more important contribution to the total energy production in the world. Today the energy production from solar energy compared to the other renewable energy sources is very low, but the PV systems are one of the fastest growing in the world. The price of PV system components, especially the PV modules are decreasing and the market for PV is expanding rapidly. Solar power will be dominant because of its availability and reliability. Photovoltaic inverters become more and more widespread within both private and commercial circles. These grid-connected inverters convert the available direct current supplied by the PV panels and feed it into the utility grid .Photovoltaic inverters can be divided into three main system configurations: central inverters, string inverters and module integrated inverters. The central and string inverters are based on the series and parallel connections of many photovoltaic panels by means of long DC cables and they exhibit problems such as:

- S Mismatching losses by using one maximum power point (MPP) control for a large group of PV modules.

- Extra losses and risk of electrical arc in the long DC wiring.

- Limited design flexibility.

Subsequently, the module integrated inverters are being developed to overcome the above problems. Each PV system has its dedicated small-sized inverter mounted on the back of panel [2,3,4,5]. Therefore, mismatching losses are significantly reduced since each module has its own MPP tracking circuit. DC wiring is minimized and the safety of the entire PV system is improved. In this case, the transformer which is heavy, bulky and inappropriate for individual solar panel installation would not be a requirement. Therefore, new Transformerless topologies have been developed and commercially available. However, the Transformerless inverter creates a common-mode resonant circuit including the filter, the inverter, the impedance of the grid and the DC source ground parasitic capacitance. In this case, a common-mode current is generated and superimposed to the grid, hence increasing its harmonics content [6,7] and causing an electromagnetic interference (EMI) between the PV system and the grid [8,9,10]. In addition, even though, the transformer ensures galvanic isolation between the grid and the PV system and provides protection and suppresses

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

the leakage current between the PV and the earth, its omission significantly increases the efficiency of the entire system.

#### **II. EXISTING SYSTEM**

Ideal Transformerless inverter generates constant common mode voltage. However, if the voltage varies with time, then a leakage current is produced. For the sake of minimizing this leakage current, different topologies were studied in detail. Among these are the full bridge with bipolar PWM, the half bridge, HERIC, H5, H6 and NPC all of which experience certain drawbacks which are discussed next.

In our existing system we have two types of inverters

- **•** Full Bridge Inverter

- Half Bridge Inverter

#### **A.FULL BRIDGE INVERTER:**

By using the full-bridge inverter with the bipolar sinusoidal pulse width modulation (SPWM), of which the CM voltage is fixed at half the dc bus voltage. Comparing with the bipolar SPWM, the unipolar SPWM has better performance in terms of the output current ripple and switching losses, but it cannot be directly used for the full-bridge inverter in the Transformerless application, because it generates the Common mode Leakage current.

#### **B.HALF BRIDGE INVERTER:**

The half-bridge inverter with the grid neutral line directly connected to the midpoint of the dc bus, The half bridge inverter, on the other hand, requires a high input voltage and a boost converter in the DC side that would increase the inverter size and cost and reduce its efficiency down to 92%. For this reason the half bridge is not recommended.

#### **REVIEW OF EXISTING INVERTER TOPOLOGIES:**

#### C. COMMON MODE CURRENT:

If the transformer is omitted, the common mode (CM) ground leakage current may appear on the parasitic capacitor between the PV panels and the ground. The existence of the CM current may reduce the power conversion efficiency, increase the grid current distortion, deteriorate the electric magnetic compatibility, and more importantly, give rise to the safety threats. The CM current path in the grid-connected Transformerless PV inverter system is illustrated in Fig.2. It is formed by the power switches, filters, ground impedance ZG and the parasitic capacitance CPV between the PV panels and the ground. According to [5], the CM current path is equivalent to an *LC* resonant circuit in series with the CM voltage, as shown in Fig.3. The CM voltage  $V_{CM}$  is defined by

$$v_{\rm CM} = \frac{v_{AO} + v_{BO}}{2} + (v_{AO} - v_{BO}) \frac{L2 - L1}{2(L1 + L2)}$$

(1)

Where

$V_{AO}$  is the voltage difference between point A and O,  $V_{BO}$  is the voltage difference between point B and O, and L1 and L2 are the output filter inductors.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

#### D. STATE-OF-THE-ART TOPOLOGIES:

One of the way to realize this goal is to use full bridge inverter with the bipolar sinusoidal pulse width modulation (SPWM). Though the unipolar SPWM has better performance when compared to bipolar SPWM, it cannot be used directly for the full bridge inverter because it generates switching frequency CM voltage. For this reason, some of the topologies based on the full bridge inverter with unipolar SPWM such as the H5 inverter, the HERIC inverter, H6 inverter with AC bypass and H6 inverter with DC bypass have been developed. Such inverter topologies require two filter inductors which may lead to a rise in the size and cost. The DC and AC sides cannot be perfectly disconnected by the power switches because of the switch parasitic capacitance, so the common mode current may still exist. If half bridge inverter, then the required DC bus voltage should be doubled compared with the full bridge topologies. Beside the classic circuits above, there are other topologies proposed in recent literatures. The Karschny inverter and the paralleled-buck inverter are derived from the buck-boost and buck circuits respectively. These solutions have high reliability, but are not capable of supplying the reactive power to the grid. The inverter proposed in employs a capacitor voltage divider to keep the CM voltage constant, but is regarded to be of higher conduction losses.

#### **III. PROPOSED SYSTEM**

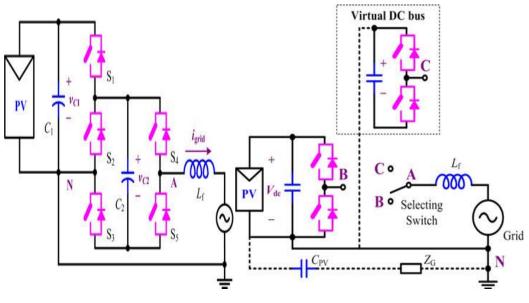

The concept of the virtual dc bus is depicted in our proposed system. By connecting the grid neutral line directly to the negative pole of the PV panel, the voltage across the parasitic capacitance  $C_{PV}$  is clamped to zero. This prevents any leakage current flowing through it. With respect to the ground point N, the voltage at midpoint B is either zero or  $+V_{dc}$ , according to the state of the switch bridge. The purpose of introducing the virtual dc bus is to generate the negative output voltage, which is necessary for the operation of the inverter. If a proper method is designed to transfer the energy between the real bus and the virtual bus, the voltage across the virtual bus can be kept the same as the real one.

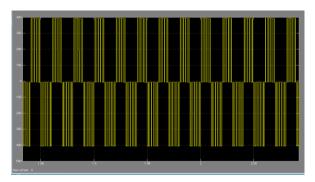

The positive pole of the virtual bus is connected to the ground point N, so that the voltage at the midpoint C is either zero or -Vdc. The dotted line in the figure indicates that this connection may be realized directly by a wire or indirectly by a power switch. With points B and C joined together by a smart selecting switch, the voltage at point A can be of three different voltage levels, namely +Vdc, zero, and -Vdc. Since the CM current is eliminated naturally by the structure of the circuit, there is not any limitation on the modulation strategy, which means that the advanced modulation technologies such as the unipolar SPWM or the double-frequency SPWM can be used to satisfy various PV applications.

### A.NEGATIVE VOLTAGE GENERATION:

Based on the virtual dc bus concept, a novel inverter topology is derived as an example to show the clear advantages of the proposed methodology, which is shown in Fig. 7. It consists of five power switches S1–S5 and only one single filter inductor Lf. The PV panels and capacitor C1 form the real dc bus while the virtual dc bus is provided by C2. With the switched capacitor technology, C2 is charged by the real dc bus through S1 and S3 to maintain a constant voltage. This topology can be modulated with the unipolar SPWM and double-frequency SPWM. The detailed analysis is introduced as follows.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

Fig 3.1 Proposed Topology

Fig 3.2Virtual Dc Bus Concept

Unipolar and Double Frequency Sinusoidal PWM Modulation Technique are used .when compared to double frequency unipolar has better performance.

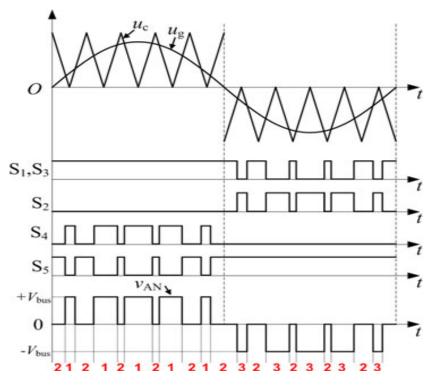

### **B.UNIPOLAR SPWM:**

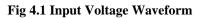

The waveform for the unipolar SPWM of the proposed inverter is displayed in Fig.. The gate drive signals for the power switches are generated according to the relative value of the modulation wave  $u_g$  and the carrier wave  $u_c$ . During the positive half grid cycle,  $u_g > 0$ . S1 and S3 are turned ON and S2 is turned OFF, while S4 and S5 commutate complementally with the carrier frequency. The capacitors C1 and C2 are in parallel and the circuit rotates between states 1 and 2 as shown in Fig.During the negative half cycle, ug < 0. S5 is turned ON and S4 is turned OFF. S1 and S3 commutate with the carrier frequency synchronously and S2 commutates in complement to them. The circuit rotates between states 3 and 2. At state 3, S1 and S3 are turned OFF while S2 is turned ON. The negative voltage is generated by the virtual dc bus C2 and the inverter output is at negative voltage level. At state 2, S1 and S3 are turned ON while S2 is turned OFF. The inverter output voltage  $V_{AN}$  equals zero; meanwhile, C2 is charged by the dc bus through S1 and S3.

(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 1, January 2015

Fig .3 Unipolar Spwm for The Proposed Topology.

#### C.DOUBLE-FREQUENCY SPWM:

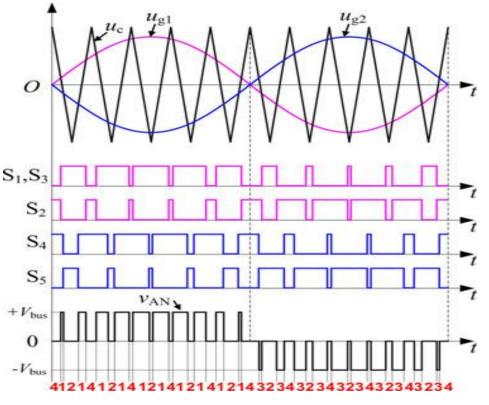

The proposed topology can also work with double-frequency SPWM to achieve a higher equivalent switching frequency, as shown in Fig. 9. In the double-frequency SPWM, the five power switches are separated into two parts, and are modulated with two inverse sinusoidal waves respectively. S1, S2, and S3 are modulated with ug1, while S4 and S5 are modulated with ug2.

During the positive half grid cycle, the circuit rotates in the sequence of "state 4 – state 1 – state 2 – state 1," and the output voltage  $V_{AN}$  varies between  $+V_{dc}$  and the zero with twice of the carrier frequency. During the negative half grid cycle, the circuit rotates in the sequence of "state 4 – state 3 – state 2 –state 3," and the output voltage  $V_{AN}$  varies between  $-V_{dc}$  and zero.

The aforementioned two modulation strategies both have their own advantages. The double-frequency SPWM can provide a higher equivalent switching frequency so that the size and weight of the filter inductor can be reduced. On the other hand, the unipolar SPWM can guarantee that the virtual dc bus C2 is charged by the real bus every switching cycle, so that the current stress on S1 and S3 caused by the operation of the switched capacitor can be reduced. In this paper, the unipolar SPWM is chosen as an example for the performance evaluation and experimental verification.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

### FIG .3 DOUBLE-FREQUENCY SPWM FOR THE PROPOSED TOPOLOGY.

### **IV. SIMULATION RESULTS**

### A.INTRODUCTION TO MATLAB:

MATLAB is a software package for computation in engineering, science, and applied mathematics. It offers a powerful programming language, excellent graphics, and a wide range of expert knowledge. MATLAB is published by and a trademark of The Math Works, Inc.The focus in MATLAB is on computation, not mathematics: Symbolic expressions and manipulations are not possible (except through the optional Symbolic Toolbox, a clever interface to maple). All results are not only numerical but inexact, thanks to the rounding errors inherent in computer arithmetic. The limitation to numerical computation can be seen as a drawback, but it's a source of strength too: MATLAB is much preferred to Maple, Mathematical, and the like when it comes to numeric.

Most successful computing languages and environments acquire a distinctive character or culture. In MATLAB, that culture contains several elements: an experimental and graphical bias, resulting from the interactive environment and compression of the write-compile-link-execute analyze cycle; an emphasis on syntax that is compact and friendly to the interactive mode, rather than tightly constrained and verbose; a kitchen-sink mentality for providing functionality; and a high degree of openness and transparency (though not to the extent of being open source software).

#### **B. SIMULINK:**

Simulink (Simulation and Link) is an extension of MATLAB by Math works Inc. It works with MATLAB to offer Modeling, simulating, and analyzing of dynamical systems under a graphical user interface (GUI) environment

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

#### **C.SIM POWERSYSTEMS:**

SimPowerSystems is a modern design tool that allows scientists and engineers to rapidly and easily build models that simulate power systems. SimPowerSystems uses the Simulink environment, allowing you to build a model using simple click and drag procedures. Not only can you draw the circuit topology rapidly, but your analysis of the circuit can include its interactions with mechanical, thermal, control, and other disciplines. This is possible because all the electrical parts of the simulation interact with the extensive Simulink modelling library. Since Simulink uses MATLAB® as its computational engine, designers can also use MATLAB toolboxes and Simulink block sets. SimPowerSystems and Sim Mechanics share a special SimPowerSystems Libraries.

#### **D.SIMULATION RESULTS:**

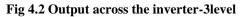

Fig 4.3 Output across the grid

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 1, January 2015

#### **VI.CONCLUSION**

The concept of the virtual DC bus is proposed to solve the CM current problem for the Transformerless grid-connected PV inverter. By connecting the negative pole of the DC bus directly to the grid neutral line, the voltage on the stray PV capacitor is clamped to zero. This eliminates the CM current completely. Meanwhile, a virtual DC bus is created to provide the negative voltage level. The required DC voltage is only half of the half bridge solution, while the performance in eliminating the CM current is better than the full bridge based inverters. Based on this idea, a novel inverter topology is proposed with the virtual DC bus concept by adopting the switched capacitor technology. It consists of only five power switches and a single filter inductor. The proposed topology is especially suitable for the small power single phase applications, where the output current is relatively small so that the extra current stress caused by the switched capacitor does not cause serious reliability problem for the power devices and capacitors. With excellent performance in eliminating the CM current, the virtual DC bus concept provides a promising solution for the Transformerless grid-connected PV inverters. The software tool used in this project is MATLAB 2012b.

#### REFERENCES

[1] P. Benner and L. Kazmerski, "Photovoltaic's gaining greater visibility," IEEE Spectr., vol. 36, no. 9, pp. 34–42, Sep. 1999.

[2] Z. Zhao, M. Xu, Q. Chen, J.-S. Lai, and Y. Cho, "Derivation of boost-buck converter based high-efficiency robust PV inverter," in *Proc. IEEE Energy Convers. Cong. Expos., Sep. 12–16, 2010, pp. 1479–1484.*

[3] R.W. Erickson and A. P. Rogers, "A micro inverter for building-integrated photovoltaic," in *Proc. 24th Annu. IEEE Appl. Power Electron. Conf. Expos., Feb. 15–19, 2009, pp. 911–917.*

[4] S. B. Kjaer, J. K. Pedersen, and F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," *IEEE Trans. Ind. Appl.*, vol. 41, no. 5, pp. 1292–1306, Sep./Oct. 2005.

[5] E. Koutroulis and F. Blaabjerg, "Design optimization of grid-connected PV inverters," in *Proc. 26th Annu. IEEE Appl. Power Electron. Conf. Expos., Mar. 6–11, 2011, pp. 691–698*