> (An ISO 3297: 2007 Certified Organization) Vol. 4, Issue 1, January 2015

# Ordinary Distribution Circulated Reckoning Technique with Equivalent Totaling Paths Used Efficient Multi Standard Transform Core Sustaining Standards

P.Sethupriyan

Assistant Professor, Dept. of ECE, Bharath University, Chennai, Tamil Nadu, India

**ABSTRACT:** This paper proposes a low-cost high-throughput multi standard transform (MST) core, which can support MOVING PICTURE EXPERTS GROUP- transforms. ordinary didtribution circulated reckoning technique combines factor sharing sharing techniques, proficiently reducing the number of adders for high hardware-sharing capability. This achieves a reduction in adders in the proposed MST, compared with the direct implementation method. With eight parallel computation paths, the proposed MST core has an eightfold operation frequency throughput rate.The CSDA-MST core thus achieves a high-throughput rate supporting multi standard transformations at low cost.

# I. INTRODUCTION

STANDARD and VC are popular video compression standards. The VC codec is designed to achieve state-of-the-art compressed video quality at bit rates that may range from very low to very high. VC Advanced Profile is also transport and container independent. This provides even greater flexibility for device manufacturers and content services.

# **Innovations:**

VC includes a number of innovations that enable it to produce high quality content. This section provides brief descriptions of some of these features.

# Adaptive Block Size Transform:

Traditionally,  $8 \times 8$  transforms have been used for image and video coding. However, there is evidence to suggest that  $4 \times 4$  transforms can reduce ringing artifacts at edges and discontinuities. VC is capable of coding an  $8 \times 8$  block using either an  $8 \times 8$  transform, two  $8 \times 4$  transforms, two  $4 \times 8$  transforms, or four  $4 \times 4$  transforms. This feature enables coding that takes advantage of the different transform sizes as needed for optimal image quality.

# **16-Bit Transforms:**

In order to minimize the computational complexity of the decoder, VC uses 16-bit transforms. This also has the advantage of easy implementation on the large amount of digital signal processing (DSP) hardware built with 16-bit processors. Among the constraints put on VC transforms is the requirement that the 16-bit values used produce results that can fit in 16 bits. The constraints on transforms ensure that decoding is as efficient as possible on a wide range of devices.

# Motion Compensation:

Motion compensation is the process of generating a prediction of a video frame by displacing the reference frame. Typically, the prediction is formed for a block (an  $8 \times 8$  pixel tile) or a macro block (a  $16 \times 16$  pixel tile) of data. The displacement of data due to motion is defined by a motion vector, which captures the shift along both the x- and y-axes. The efficiency of the codec is affected by the size of the predicted block, the granularity of sub-pixel data that can be captured, and the type of filter used for generating sub-pixel predictors. VC uses  $16 \times 16$  blocks for prediction, with the ability to generate mixed frames of  $16 \times 16$  and  $8 \times 8$  blocks. The finest granularity of sub-pixel information supported by VC is 1/4 pixel. Two sets of filters are used by VC for motion compensation. The first is an approximate bicubic

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

filter with four taps. The second is a bilinear filter with two taps. VC combines the motion vector settings defined by the block size, sub-pixel granularity, and filter type into modes. The result is four motion compensation modes that suit a range of different situations. This classification of settings into modes also helps compact decoder implementations.

# **Loop Filtering:**

VC uses an in-loop de-blocking filter that attempts to remove block-boundary discontinuities introduced by quantization errors in interpolated frames. These discontinuities can cause visible artifacts in the decompressed video frames and can impact the quality of the frame as a predictor for future interpolated frames. The loop filter takes into account the adaptive block size transforms. The filter is also optimized to reduce the number of operations required.

### **Interlace Coding:**

Interlaced video content is widely used in television broadcasting. When encoding interlaced content, the VC codec can take advantage of the characteristics of interlaced frames to improve compression. This is achieved by using data from both fields to predict motion compensation in interpolated frames.

### **Advanced B Frame Coding:**

A bi-directional or B frame is a frame that is interpolated from data both in previous and subsequent frames. B frames are distinct from I frames (also called key frames), which are encoded without reference to other frames. B frames are also distinct from P frames, which are interpolated from previous frames only. VC includes several optimizations that make B frames more efficient.

### Fading Compensation:

Due to the nature of compression that uses motion compensation, encoding of video frames that contain fades to or from black is very inefficient. With a uniform fade, every macro block needs adjustments to luminance. VC includes fading compensation, which detects fades and uses alternate methods to adjust luminance. This feature improves compression efficiency for sequences with fading and other global illumination changes.

# **Differential Quantization:**

Differential quantization, or dquant, is an encoding method in which multiple quantization steps are used within a single frame. Rather than quantize the entire frame with a single quantization level, macro blocks are identified within the frame that might benefit from lower quantization levels and greater number of preserved AC coefficients. Such macro blocks are then encoded at lower quantization levels than the one used for the remaining macro blocks in the frame. The simplest and typically most efficient form of differential quantization involves only two quantizer levels (bilevel dquant), but VC supports multiple levels, too.

# **Existing system:**

A significant amount of research has been conducted to efficiently combine and implement the transform units for multiple codec's. On the other hand little research is focused on the implementation of multi-quantized unit. Among the multiple-transform units, a unified Inverse Discrete Cosine Transform (IDCT) architecture to support five standards (such as, AVS, STANDARD, VC, MOVING PICTURE EXPERTS GROUP-2/4 and JPEG) is presented. The authors in offer an area efficient architecture to perform a DCT-based transform for JPEG, MOVING PICTURE EXPERTS GROUP-4, VC and STANDARD using delta mapping. The design in is an IDCT and IQ circuit for STANDARD, MOVING PICTURE EXPERTS GROUP-4 and VC. The MJPEG standard defines quantization as the division operation of the DCT coefficient coming from the transform unit by the corresponding Q value (specified by the quantization matrix). MJPEG allows specification of Q-matrices that facilitates the allocation of more bits for the representation of coefficients which are visually more significant.

The intercommunications between the video devices using different standards are so much inconvenient, thus video codec supporting multiple standards are more useful and more attractive. In this brief, low cost very large scale integration (VLSI) architecture is designed for multi standard inverse Discrete Cosine transform. It is used in multi standard decoder of MOVING PICTURE EXPERTS GROUP-2, MOVING PICTURE EXPERTS GROUP-4 ASP, and VC .Two circuit share strategies, factor share (FS) an adder share (AS) are applied to the inverse transform architecture

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

for saving its circuit resource. Pipelined stages are used in this Multistandard inverse transform to increase the operational speed.

The possibility to employ hierarchical prediction structures for providing temporal scalability with several layers while improving the coding efficiency and increasing the effectiveness of quality and spatial scalable coding. New methods for inter-layer prediction of motion and residual improving the coding efficiency of spatial scalable and quality scalable coding. The concept of key pictures for efficiently controlling the drift for packet-based quality scalable coding with hierarchical prediction structures. Single motion compensation loop decoding for spatial and quality scalable coding providing a decoder complexity close to that of single-layer coding.

# **Proposed system:**

The proposed CSDA algorithm combines the FS and DA methods. By expanding the coefficients matrix at the bit level, the FS method first shares the same factor in each coefficient; the DA method is then applied to share the same combination of the input among each coefficient position. An example of the proposed CSDA algorithm in a matrix inner product is as follows the proposed CSDA combines the FS and DA methods. The FS method is adopted first to identify the factors that can achieve higher capability in hardware resource sharing, where the hardware resource in defined as the number of adder usage. Next, the DA method is used to find the shared coefficient based on the results of the FS method. The adder-tree circuits will be followed by the proposed CSDA circuit. Thus, the CSDA method aims to reduce the nonzero elements to as few as possible. The CSDA shared coefficient is used for estimating and comparing thereafter the number of adders in the CSDA loop.

The proposed 2-D CSDA-MST core consists of two 1-D CSDA-MST core (Core-1 and Core-2) with a transposed Memory (TMEM). Core-1 and Core-2 are different in word length for each arithmetic, MUX, and register, and the TMEM is designed using sixty-four 12-bit registers, where the output data from Core-1 can be transposed and fed into Core-2. The registers in TMEM are designed the same way as the architecture. Each core has four pipeline stages: two in the even and odd part CSDA circuit, and two in ECATs. Therefore, the proposed 2-D CSDA-MST core has a latency of 16 clock cycles (= 4 + 8 + 4), and the TMEM executes transposed operation after 12 clock cycles (= 4 + 8) when 8 pixels are input.

The CSDA-MST core can achieve high performance, with a high throughput rate and low-cost VLSI design, supporting MOVING PICTURE EXPERTS GROUP-1/2/4, STANDARD, and VC MSTs. By using the proposed CSDA method, the number of adders and MUXs in the MST core can be saved efficiently. Measured results show the CSDA-MST core with a throughput rate of 1.28 G-pels/s, which can support (4928 × 2048@24 Hz) digital cinema format with only 30 k logic gates. Because visual media technology has advanced rapidly, this approach will help meet the rising high-resolution specifications and future needs as well.

#### Modules:

- 1-D Common sharing distributed arithmetic-MST

- Even part Ordinary didtribution circulated reckoning techniquecircuit

- Odd part Ordinary didtribution circulated reckoning circuit

- 2-D Ordinary didtribution circulated reckoning technique-MST core

#### Module description:

#### **1-D** common sharing distributed arithmetic-MST:

Based on the proposed CSDA algorithm, the coefficients for MOVING PICTURE EXPERTS GROUP-1/2/4, STANDARD, and VC transforms are chosen to achieve high sharing capability for arithmetic resources. To adopt the searching flow, software code will help to do the iterative searching loops by setting a constraint with minimum nonzero elements. In this paper, the constraint of minimum nonzero elements is set to be five. After software searching, the coefficients of the CSD expression, where 1 indicates -1. Note that the choice of shared coefficient is obtained by some constraints. Thus, the chosen CSDA coefficient is not a global optimal solution. It is just a local or suboptimal solution. Besides, the CSD codes are not the optimal expression, which have minimal nonzero bits. However, the chosen coefficients of CSD expression can achieve high sharing capability for arithmetic resources by using the

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

proposed CSDA algorithm. More information about CSDA coefficients for MOVING PICTURE EXPERTS GROUP-1/2/4, STANDARD, and VC transforms.

#### Even part ordinary didtribution circulated reckoning technique circuit:

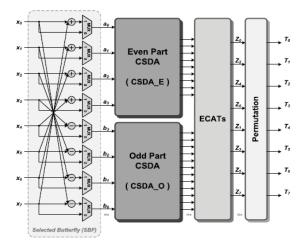

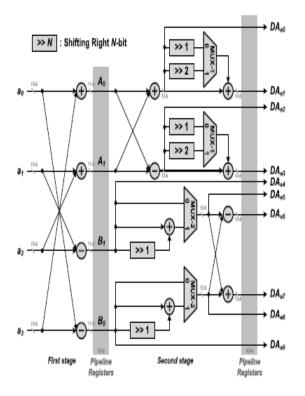

The SBF module executes for the eight-point transform and bypasses the input data for two four-point transforms. After the SBF module, the CSDA\_E and CSDA\_O execute and by feeding input data a andb, respectively. The CSDA\_E calculates the even part of the eight-point transform, similar to the four-point Trans form for STANDARD and VC standards. Within the architecture of CSDA\_E, two pipeline stages exist (12-bit and 13-bit). The first stage executes as a four-input butterfly matrix circuit, and the second stage of CSDA\_E then executes by using the proposed CSDA algorithm to share hardware resources in variable standards.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

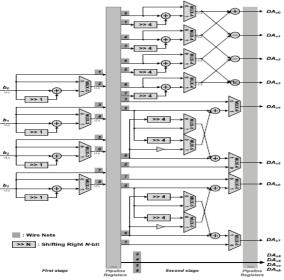

### Odd part ordinary didtribution circulated reckoning technique circuit:

Similar to the CSDA\_E, the CSDA\_O also has two pipeline stages. Based on the proposed CSDA algorithm, the CSDA\_O efficiently shares the hardware resources among the odd part of the eight-point transform and four-point transform for variable standards. It contains selection signals of multiplexers (MUXs) for different standards. Eight adder trees with error compensation (ECATs) are followed by the CSDA\_E and CSDA\_O, which add the nonzero CSDA coefficients with corresponding weight as the tree-like architectures. The ECATs circuits can alleviate truncation error efficiently in small area design when summing the nonzero data all together.

# 2-D ordinary didtribution circulated reckoning technique-MST core:

This section provides a discussion of the hardware resources and system accuracy for the proposed 2-D CSDA-MST core and also presents a comparison with previous works. Finally, the characteristics of the implementation into a chip are described.

| 1-D      | Transposed | 1-D      |

|----------|------------|----------|

| CSDA-MST | Memory     | CSDA-MST |

| Core-1   | (TMEM)     | Core-2   |

#### **Common Sharing Distributed Arithmetic**

Distributed Arithmetic (DA) has been wildly adopted for its computational efficiency in many digital signal processing applications such as DCT (Discrete Cosine Transform), DFT (Discrete Fourier Transform), FIR (Finite Impulse Response), and DHT (Discrete Hartley Transform). These applications involve the computation of inner products between two vectors, one of which is a constant. The general method to generate the products is to use a MAC (multiply and accumulate) unit, which is fast but has a high cost in the case of long-length inner-products. In contrast, DA provides an efficient solution to realize the inner products by using memory look-up and accumulation operations. The idea behind the conventional DA, called ROM-based, is to replace multiplication operations by pre-computing all possible values and storing these in a ROM. According to the ROM based DA can reduce the circuit size by 50-80% on average. Custom reconfigurable technology emerged to satisfy the simultaneous demand for flexibility and efficiency. Custom/domain-specific reconfigurable arrays can be programmed to adapt for different applications, so the efficiency of the hardware and flexibility of the whole system is improved. Earlier works, such as, show good performance in area, power consumption and speed. Since a domain-specific reconfigurable architecture targets few application fields, it achieves better performance than a general purpose FPGA device.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

### PROPOSED 2-D CSDA-MST CORE DESIGN

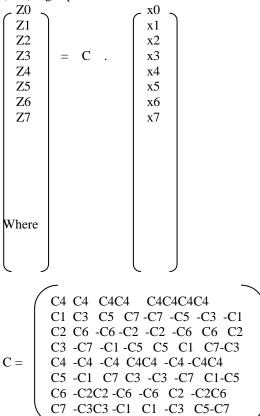

We introduces the proposed 2-D CSDA-MST core implementation. Neglecting the scaling factor, the one dimensional (1-D) eight-point transform can be defined as follows

Because the eight-point coefficient structures in MOVING PICTURE EXPERTS GROUP- 1/2/4, STANDARD, and VC standards are the same, the eight-point transform for these standards can use the same mathematic derivation. According to the symmetry property, the 1-D eight point transform in (8) can be divided into even and odd two four-point transforms, Zeand Zo, as listed in (9) and (10), respectively

$$Ze = \begin{bmatrix} Z0 \\ Z2 \\ Z4 \\ Z6 \end{bmatrix} \begin{pmatrix} C4 & C4 & C4C4 \\ C2 & C6 & -C6 & -C2 \\ C4 & -C4 & -C4 & C4 \\ C6 & -C2 & C2 & -C6 \end{pmatrix} \begin{bmatrix} a0 \\ a1 \\ a2 \\ a3 \end{bmatrix}$$

$$= Ce.a$$

$$Zo = \begin{bmatrix} Z1 \\ Z3 \\ Z5 \\ Z7 \end{bmatrix} \begin{pmatrix} C1 & C3 & C5 & C7 \\ C3 & -C7 & -C1 & -C5 \\ C5 & -C1 & C7 & C3 \\ C7 & -C3 & C3 & -C1 \end{pmatrix} \begin{bmatrix} b0 \\ b1 \\ b2 \\ b3 \end{bmatrix}$$

$$= Co.b$$

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

Where

|     | ( )           | 1     | ( )   |

|-----|---------------|-------|-------|

|     | X0+X7         |       | x0-x7 |

| a = | X1+X6         | , b = | x1-x6 |

|     | X2+X5         |       | x2-x5 |

|     | X3+X4         |       | x3-x4 |

|     | $\sim$ $\sim$ |       | < >   |

The even part of the operation in (10) is the same as that of the four-point STANDARD and VC transformations. Moreover, the even part Zecan be further decomposed into even and odd parts: Zee and Zeo

$$Zee = \begin{bmatrix} Z0 \\ Z4 \end{bmatrix} = \begin{bmatrix} C4 & C4 \\ C4 & -C4 \end{bmatrix} \begin{bmatrix} A0 \\ A1 \end{bmatrix}$$

$$= Cee.A$$

$$Zeo = \begin{bmatrix} Z2 \\ Z6 \end{bmatrix} \begin{bmatrix} C2 & C6 \\ C6 & -C2 \end{bmatrix} \begin{bmatrix} B0 \\ B1 \end{bmatrix}$$

Where

|     | ( )   |       | $\boldsymbol{\mathcal{C}}$ | 7 |

|-----|-------|-------|----------------------------|---|

|     | a0+a3 | a0 -  | a3                         |   |

| A = |       | , B = |                            |   |

|     | a1+a2 | a1 -  | a2                         | J |

|     |       |       | $\overline{\ }$            |   |

Ceo.B

# **Applications:**

• Video and image applications

# **Future Enhancement:**

I will modify the proposed system by reducing the Area of converting one dimensional to two dimensional core designs. And also will reduce the total number of adders by using the CSDA Ordinary didtribution circulated reckoning techniquemethod in the proposed system.

#### **Conclusion:**

The CSDA-MST core can achieve high performance, with a high throughput rate and low-cost VLSI design, supporting MOVING PICTURE EXPERTS GROUP-1/2/4, STANDARD, and VC MSTs. By using the proposed CSDA method, the number of adders and MUXs in the MST core can be saved efficiently. Measured results show the CSDA-MST core with a throughput rate of 1.28 G-pels/s, which can support ( $4928 \times 2048@24$  Hz) digital cinema format with only 30 k logic gates. Because visual media technology has advanced rapidly, this approach will help meet the rising high-resolution specifications and future needs as well.

#### REFERENCES

[1] S. Uramoto, Y. Inoue, A. Takabatake, J. Takeda, Y.Yamashita, H. Terane, and M. Yoshimoto, "A 100- MHz 2-D discrete cosine transform core processor," IEEE J. Solid-State Circuits, vol. 27, no. 4, pp.

[2] S. Yu and E. E. Swartzlander, "DCT implementation with distrib- uted arithmetic," IEEE Trans. Comput., vol. 50, no. 9, pp. 985–991, Sep. 2001.

[3] Lydia Caroline M., Vasudevan S., "Growth and characterization of pure and doped bis thiourea zinc acetate: Semiorganic nonlinear optical single crystals", Current Applied Physics, ISSN : 1567-1739, 9(5) (2009) pp. 1054-1061.

(An ISO 3297: 2007 Certified Organization)

# Vol. 4, Issue 1, January 2015

[4] A. M. Shams, A. Chidanandan, W. Pan, and M. A. Bayoumi, "NEDA: A low-power high-performance DCT architecture," IEEE Trans. Signal Process., vol.54, no. 3, pp. 955-964, Mar. 2006.

[5] Lydia Caroline, M., Kandasamy, A., Mohan, R., Vasudevan, S., "Growth and characterization of dichlorobis l-proline Zn(II): A semiorganic nonlinear optical single crystal", Journal of Crystal Growth, ISSN: 0022-0248, 311(4) (2009) pp. 1161-1165.

[6] C. Y. Huang, L. F. Chen, and Y. K. Lai, "A high- speed 2-D transform architecture with unique kernel for multi-standard video applications," in Proc. IEEE Int. Symp. Circuits Syst., May 2008, pp. 21–24.

[7] Nagarajan, C., Madheswaran, M., "Experimental study and steady state stability analysis of CLL-T series parallel resonant converter with fuzzy controller using state space analysis", Iranian Journal of Electrical and Electronic Engineering, ISSN : 1735-2827, 8(3) (2012) pp.259-267. [8] Y. H. Chen, T. Y. Chang, and C. Y. Li, "High throughput DA-based DCT with high accuracy error- compensated adder tree," IEEE Trans.

Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 4, pp. 709–714, Apr. 2011.

[9] Parthasarathy R., Ilavarasan R., Karrunakaran C.M., "Antidiabetic activity of Thespesia Populnea bark and leaf extract against streptozotocin

induced diabetic rats", International Journal of PharmTech Research, ISSN : 0974-4290, 1(4) (2009) pp. 1069-1072.

[10] Poongothai S., Ilavarasan R., Karrunakaran C.M., "Simultaneous and accurate determination of vitamins B1, B6, B12 and alpha-lipoic acid in multivitamin capsule by reverse-phase high performance liquid chromatographic method", International Journal of Pharmacy and Pharmaceutical Sciences, ISSN : 0975 - 1491, 2(\$4) (2010) pp. 133-139. [11] Y. H. Chen, T. Y. Chang, and C. Y. Li, "A high performance video transform engine by using space- time scheduling strategy," IEEE Trans.

Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 4, pp. 655–664, Apr. 2012.

[12] R.Balaji, HR Role in Change, Transformation and Job Effectiveness, International Journal of Innovative Research in Science, Engineering and Technology, ISSN: 2319-8753,pp 2961-2964, Vol. 2, Issue 7, July 2013

R.Balaji, Empowering Generation-Y Entrepreneurs, International Journal of Innovative Research in Science, Engineering and [13] Technology, ISSN: 2319-8753,pp 15903-15906, Vol. 3, Issue 9, September 2014

R.Balaji, Role of Human Resource Manager in Managing Stress of Employees in Manufacturing Concerns, International Journal of [14] Innovative Research in Science, Engineering and Technology, ISSN: 2319-8753, pp 11070-11073, Vol. 3, Issue 4, April 2014

R.Balaji, Role of Trade Unions in Manufacturing Concerns, International Journal of Innovative Research in Science, Engineering and [15] Technology, ISSN: 2319-8753,pp 12251-12255, Vol. 3, Issue 5, May 2014

R.Balaji,, A Study on the Problems, Perspectives and Implications of the New Direct Benefit Transfer Scheme With Reference To [16] Kanchipuram District of Tamilnadu, International Journal of Innovative Research in Science, Engineering and Technology, ISSN: 2319-8753,pp 4655-4658, Vol. 2, Issue 9, September 2013