(An ISO 3297: 2007 Certified Organization)

Vol. 4, Issue 2, February 2015

# Pulse Width Modulation Used in Multilevel Inverters

Jafar Ali, S.P.Vijayaragavan

Dept. of EEE, Bharath University, Chennai, Tamil Nadu, India

Assistant Professor, Dept. of EEE, Bharath University, Chennai, Tamil Nadu, India

**ABSTRACT:** The multilevel inverter topology gives the advantages of usage in high power and high voltage application with reduced harmonic distortion without a transformer. This paper presents a comparative study of nine level diode clamped inverter for constant Switching frequency of sinusoidal Pulse width Modulation and sinusoidal Natural Pulse width Modulation with switching frequency.

#### I. INTRODUCTION

MULTILEVEL Pulse Width Modulation (PWM) in-verters have been gained importance in high per-formance power applications without requiring high ratings on individual devices, as static var compen-sators, drives and active power filters. A multilevel inverter divides the dc rail directly or indirectly, so that the output of the leg can be more than two discrete levels. As both amplitude modulation and pulse width modulation are used in this, the quality of the output waveform gets improved with low distortion. The advantages of multi-level inverter are good power quality, low switching losses, reduced output dv/dt and high voltage capability. Increasing the number of voltage levels in the inverter increases the power rating. The three main topologies of multilevel inverters are the Diode clamped inverter, Fly-ing capacitor inverter, and the Cascaded H-bridge inverter [1][2]. The PWM schemes of multilevel inverters are classified in to two types the multicarrier sub-harmonic PWM (MC-SHPWM) and the Multicarrier switching frequency optimal pulse width modulation (MC-SFOPWM) [4][5]. The MC-SHPWM diode clamped multilevel inverter strategy reduced total harmonic distortion and the MC-SFOPWM technique for multilevel inverter strategy enhances the fundamental output voltage [6]. This paper considered the most popular structure among the trans-formerless voltage source multilevel inverters, the diode-clamped converter based on the neutral point converter proposed by Akagea et al [1].

#### II. MULTILEVEL INVERTER SCHEMATIC DIAGRAMS

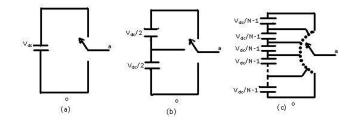

Fig 1(a) shows a two level inverter. Fig 1(b) shows a three level inverter. Fig 1(c) shows N level inverter. All the capacitors comprises to a voltage of  $V_{dc}$ .

Figure 1 Schematic Diagram of (a) Two level Inverter (b) Three Level Inverter (c) N Level Inverter

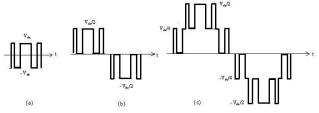

Fig 2(a) shows the output voltage of a two level inverter. Fig 2(b) shows the output voltage a three level inverter. Fig

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 2, February 2015

2(c) shows the output voltage of an N level inverter.

Figure 2 Output Voltage of (a) Two Level Inverter (b) Three Level Inverter (c) Five Level Inverter

#### III. DIODE CLAMPED MULTILEVEL INVERTER

For an N level (between the phase and the negative rail) diode clamped inverter, The number of levels in the line-to-line voltage waveform will be k=2N-1(1)The number of levels in the line to load neutral of a star or wye load will be p=2k-1(2)The number of capacitors required, independent of the number of phase, is N<sub>cap</sub>=N-1 (3)While the number of clamping diodes per phase is  $D_{clamp}=2(N-1)$ (4) nstates=Nphases (5) and the number of switches in each leg is Sn=2(N-1)(6)

The number of possible switch states is

#### IV. PWM METHODS FOR MULTILEVEL INVERTERS

The two basic approaches used to generate the PWM sig-nals for multilevel inverters are Sub harmonic or Sub-Oscillation carrier based PWM-modulating waveform comparison with offset triangular carriers Space Vector PWMspace vector modulation based on a rotating vector in multilevel space and these are the extensions of traditional two level con-trol strategies to several levels.

The two main advantages of PWM inverters in compari-son to square-wave inverters are (i) control over output voltage magnitude (ii) reduction in magnitudes of un-wanted harmonic voltages. Good quality output voltage in SPWM requires the modulation index (m) to be less than or equal to 1.0. For m>1 (over-modulation), the fun-damental voltage magnitude increases but at the cost of decreased quality of output waveform. The maximum fundamental voltage that the SPWM inverter can output (without resorting to over-modulation) is only 78.5% of the fundamental voltage output by square-wave inverter. In this paper one more PWM techniques have been considered. The merits and demerits of these two PWM tech-niques are compared under comparable circuit conditions on the basis of factors like (i) quality of output voltage (ii) obtainable magnitude of output voltage (iii) ease of con-trol etc. The peak obtainable output voltage from the giv-en input dc voltage is one important figure of merit for the inverter.[9]

Carrara considered different methods of disposing the many carrier bands required in multilevel PWM.[10] Four alternative carrier PWM strategies with differing phase relationships for a multilevel inverter [15] are as follows:

1) In-phase disposition (IPD), where all the carriers are in phase- Technique A1;

2) Phase opposition disposition (POD), where the carri-ers above the zero reference are in phase, but shifted by  $180^{\circ}$

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 2, February 2015

from those carriers below the zero reference-Technique A2;

- 3) Alternative phase opposition disposition (APOD), where each carrier band is shifted by  $180^{\circ}$  from the ad-jacent bands- Technique A3;

- 4) Phase Disposition (PD), all the carriers are phase shifted by 2 /(N-1) radians- Technique B.

PD strategy is used most frequently because it pro-duces minimum harmonic distortion for the line-to-line output voltage [13], [14], [15], [16], [17].

#### 4.1 SubHarmonic Pulse Width Modulation SHPWM Technique

In SHPWM technique the intersection of the triangular carrier and the modulation wave determines the genera-tion of the pulse. This requires a carrier of much higher frequency than the modulation frequency. [6-8]The generated rectilinear output voltage pulses are modulated such that their duration is proportional to the instantaneous value of the sinusoidal waveform at the centre of the pulse; that is, the pulse area is proportional to the corresponding value of the modulating sine wave.[10-11]

If the carrier frequency is very high, an averaging effect occurs, resulting in a sinusoidal fundamental output with highfrequency harmonics, but minimal low-frequency harmonics.

#### 4.2 Switching Frequency Optimal Pulse width Modulation SFOPWM Technique

Steinke [12] proposed SFOPWM, a carrier based method where addition of triplen harmonic to the fundamental frequency Sinusoidal lowers the peak magnitude, thus allowing operating in over modulation region. This in-creases the inverter output voltage without compromising on the quality of the output waveform [3][4]. Equations (9) to (12) are used to obtain the modulating wave.

| $V_{offset} = (max (V_a, V_b, V_c) + min (V_a, V_b, V_c))/2$ | (9)  |

|--------------------------------------------------------------|------|

| VaSFO = Va - Voffset                                         | (10) |

| VbSFO = Vb - Voffset                                         | (11) |

| VcSFO = Vc - Voffset                                         | (12) |

Where m is the number of carrier waves also the level of the inverter, required for pulse generation.

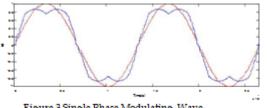

A sinusoidal and its modulated wave obtained from (13), (14) are shown in Fig.3 for a modulation index of 1.

Figure 3 Single Phase Modulating Wave

#### 4.3 Sinusoidal Natural PWM and Sinusoidal PWM Techniques

Operation of a multilevel inverter at low switching fre-quency is the Sinusoidal natural PWM and alternately sinusoidal PWM technique is operation at high switching frequency.

#### ANALYSIS OF NINE LEVEL DIODE CLAMPED INVERTER V.

A three-phase nine-level diode-clamped inverter is shown in Fig.4 [15][17]. Each phase is constituted by 16 switches (eight switches for upper leg and eight switches for lower leg). Switches  $S_{a1}$  through  $S_{a8}$  of upper leg form complementary pair with the switches Sal to Sal lower leg of the same phase. The complementary switch pairs for phase 'A' are  $(S_{a1}, S_{a1})$ ,  $(S_{a2}, S_{a2})$ ,  $(S_{a3}, S_{a3})$ ,  $(S_{a4}, S_{a4})$ ,  $(S_{a5}, S_{a5})$ ,  $(S_{a6}, S_{a6})$ ,  $(S_{a7}, S_{a7})$ ,  $(S_{a8}, S_{a8})$  and similarly for B and C phases [1],[2],[3],[4],[5],[6],[7],[8],[17]. Clamping diodes are used to carry the full load current.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 2, February 2015

low-harmonic distortion waveform characteristics with well-defined harmonic spectrum, the fixed switching frequency, and implementation simplicity. Simple tech-niques for generating the modulation waves of the highperformance PWM methods are described. [19]The two novel methodologies Natural Sinusoidal PWM and Sinusoidal PWM for 3<sup>rd</sup> harmonic injected modulated wave called SFOPWM using constant switching frequency are compared[4],[5]. The one most important modulator charac-teristics—the total harmonic distortion is analytically modeled and compared for various carrier pwm methods applied to a nine level Neutral point clamped or Diode clamped inverter. Simulations of the controller and of the inverter have been made in the MATLAB SIMULINK environment.[18]

A nine level inverter is simulated for a normal modula-tion index of 0.8 and over modulation index of 1.1 at a switching frequency of 450Hz for Sinusoidal natural PWM and 1050Hz for Sinusoidal PWM technique.

#### VI. SIMULATION RESULTS AND DISCUSSIONS

Table 2 show at normal modulation index of 0.8 im-proved performance with reduced harmonic distortion is observed with SPWM technique for A1through B tech-niques for nine level diode clamped inverter.

| TABLE 2                                               |

|-------------------------------------------------------|

| LINE-LINE VOLTAGE AND THD FOR NORMAL MODULATION INDEX |

|    | SNPWM |       | SPWM  |       |  |

|----|-------|-------|-------|-------|--|

|    | Vab   | THD   | Vab   | THD   |  |

| A1 | 44.94 | 10.27 | 46.55 | 9.46  |  |

| A2 | 45.53 | 12.24 | 46.72 | 9.29  |  |

| A3 | 45.59 | 11.38 | 46.63 | 9.49  |  |

| В  | 59.58 | 17.32 | 60.61 | 13.50 |  |

Table 1 shows phase to fictitious midpoint 'o' of capacitor string voltage ( $V_{AO}$ ) and line to line voltage ( $V_{AB}$ ) for various switchings'.

TABLE 1

POLE VOLTAGE AND LINE VOLTAGE OF A NINE LEVEL INVERTER

| <sup>s</sup> a1 | <sup>s</sup> a2 | <sup>s</sup> a3 | <sup>s</sup> a4 | <sup>s</sup> a5 | <sup>s</sup> a6 | <sup>s</sup> a7 | <sup>s</sup> a8 | <sup>V</sup> AB     | <sup>v</sup> A0      |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------------|----------------------|

| 1               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | <sup>v</sup> dc     | <sup>v</sup> dc      |

| 0               | 1               | 1               | 1               | 1               | 1               | 1               | 1               | $V_{dc}/8$          | $3V_{dc}/4$          |

| 0               | 0               | 1               | 1               | 1               | 1               | 1               | 1               | $2V_{dc}/8$         | $2V_{dc}/4$          |

| 0               | 0               | 0               | 1               | 1               | 1               | 1               | 1               | $3V_{dc}/8$         | $V_{dc}/4$           |

| 0               | 0               | 0               | 0               | 1               | 1               | 1               | 1               | $4V_{dc}/8$         | 0                    |

| 0               | 0               | 0               | 0               | 0               | 1               | 1               | 1               | $5V_{dc}/8$         | -V <sub>dc</sub> /4  |

| 0               | 0               | 0               | 0               | 0               | 0               | 1               | 1               | 6V <sub>dc</sub> /8 | -2V <sub>dc</sub> /4 |

| 0               | 0               | 0               | 0               | 0               | 0               | 0               | 1               | $7V_{dc}/8$         | -3V <sub>dc</sub> /4 |

| 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0               | 0                   | -V <sub>dc</sub>     |

This paper provides analytical methods for the study, performance evaluation, and design of the modern car-rier-based PWM's, like bipolar and unipolar suboscilla-tion carrier PWM methods which are widely employed in PWM multilevel voltage-source inverter drives due to the

(An ISO 3297: 2007 Certified Organization)

### Vol. 4, Issue 2, February 2015

A table 3 show at over modulation index of 1.1 im-proved performances with reduced harmonic distortion is observed with SPWM technique for A1through B techniques for nine level diode clamped inverter.[20-22]

TABLE 3

LINE-LINE VOLTAGE AND THD FOR OVER MODULATION INDEX

|    | SNPWM |       | SPWM  |       |  |

|----|-------|-------|-------|-------|--|

|    | Vab   | THD   | Vab   | THD   |  |

| A1 | 65    | 7.89  | 65.67 | 6.89  |  |

| A2 | 65.78 | 9.13  | 66.09 | 7.93  |  |

| A3 | 65.84 | 8.55  | 66.02 | 7.42  |  |

| В  | 66.49 | 16.51 | 67.1  | 13.39 |  |

Fig 5 to Fig 10 shows the pole voltage, line voltage and its THD for normal modulation index of 0.8 for phase disposition technique A1 for SNPWM tecchnique with a frequency of 450Hz and SPWM for 1050Hz frequency.[23]

Fig 10 to Fig 16 shows the pole voltage, line voltage and its THD for over modulation index of 1.1 for phase

(An ISO 3297: 2007 Certified Organization)

#### Vol. 4, Issue 2, February 2015

disposition technique A1 for SNPWM tecchnique with a frequency of 450Hz and SPWM for 1050Hz frequency.

#### VII. CONCLUSION

A third harmonic injected modulated wave is used to generate the gating signals for a modeled nine level diode clamped multilevel inverter..

#### REFERENCES

- José Rodríguez, Jih-Sheng Lai, Fang Zheng Peng "Multilevel Inverters: A Survey of Topologies, Controls, and Applications", IEEE Trans., 1. VOL. 49, NO. 4, AUGUST 2002

- 2 Sukumaran V.G., Bharadwaj N., "Ceramics in dental applications", Trends in Biomaterials and Artificial Organs, ISSN : 0971-1198, 20(1) (2006) pp.7-11.

- G.Carrara, S.Gardella, M.Marchesoni, R.Salutari and G.Sciutto, "A New Multilevel PWM Method: A theoretical Analysis", IEEE Transactions 3. on Power Electronics, Vol. 7, No. 3, July 1992, pp.497-505.

- Selva Kumar S., Ram Krishna Rao M., Balasubramanian M.P., "Chemopreventive effects of Indigofera aspalathoides on 20-4. methylcholanthrene induced fibrosarcoma in rats", International Journal of Cancer Research, ISSN: 1811-9727, 7(2) (2011) pp.144-151.

- A. Nabae, I. Takahashi, H. Akagi. "A neutral-point clamped PWM inverter", IEEE Trans. on I.A., Vol. IA-17, No. 5, 1981, pp. 518-523. 5. Menon R., Kiran C.M., "Concomitant presentation of alopecia areata in siblings: A rare occurrence", International Journal of Trichology, ISSN 6.

- : 0974-7753, 4(2) (2012) pp.86-88 7. [7]P.Palanivell, Subhransu Sekhar Dash, "Comparative Study of Constant Switching Frequency and Variable Switching Frequency Multicarrier Pulse width Modulation for Three Phase Cascaded Mul-

[8]Rayen R., Hariharan V.S., Elavazhagan N., Kamalendran N., Varadarajan R., "Dental management of hemophiliac child under general anesthesia", Journal of Indian Society of Pedodontics and Preventive Dentistry, ISSN: 0970-4388, 29(1) (2011) pp.74-79.

[9]P.Palanivel1, Subhransu Sekhar Dash, "Multicarrier Pulse Width Modulation Based Three Phase Cascaded Multitlevel Inverter Includ-ing Over Modulation and Low Modulation Indices", International Journal of Engineering Studies ISSN 0975- 6469 Volume 1, Number 2 (2009), pp. 71–82 [10]Shanthi B., Revathy C., Devi A.J.M., Subhashree, "Effect of iron deficiency on glycation of haemoglobin in nondiabetics", Journal of Clinical

and Diagnostic Research, ISSN: 0973 - 709X, 7(1) (2013) pp.15-17.

[11]A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," IEEE Trans. Ind. Applicat., pp. 518–523, Sept./Oct.1981. [12]J. S. Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters," IEEE Trans. Ind. Applicat., Vol. 32, pp. 509–517, May/June 1996.

[13]M. Carpita, M. Fracchia. S. Tenconi. "A novel multilevel struc-ture for voltage source inverter", Proceedings of the 4th Euro-pean Conf, on Power Electronics and Applications (EPE'91), Firenze, Italy, September 1991, pp.1-090/1-094.

[14] J. Holtz, "Pulsewidth modulation—A survey," IEEE Trans. Ind. Electron., Vol. 39, pp. 410–420, Oct. 1992.

[15] Nguyen Van Nho, Quach Thanh Hai, Hong Hee Lee," Carrier Based Single-State Pwm Technique In Multilevel Inverter", Inter-national Symposium on Electrical & Electronics Engineering 2007 - Oct 24, 25 2007

[16]B. P. McGrath, D.G. Holmes, M. Manjrekar, T. A. Lipo, "An Improved Modulation Strategy For A Hybrid Multilevel Inver-ter" 2000. [17]J.K. Steinke, "Control Strategy for a Three Phase AC Traction Drive with a 3-level GTO PWM Inverter", IEEE PESC, 1988, pp. 431-438.

[18]Ivo Pereira, António Martins, "Experimental Comparison of Car-rier and Space Vector PWM Control Methods for Three-Phase NPC Converters" International Conference on Renewable Energies and Power Quality (ICREPQ'09), Valencia (Spain), 15th to 17th April, 2009.

[19]A.Tahri, A.Draou "A Comparative Modelling Study of PWM Control Techniques for Multilevel Cascaded Inverterr", Leo-nard Journal of Sciences ,Jan-Jun 2005 , pp 42-58.

[20]leon M. Tolbert, Fang Z.Peng, Thomas G. Habetler, "Multile-vel PWM Methods at Low Modulation Indices" APEC '99, Dallas, Texas, March 14-18, pp 1032-1039.

[21] Leon M. Tolbert, Fang Z.Peng, ,Thomas G. Habetler, "Novel Multilevel Inverter Carrier-Based PWM" IEEE IAS 1998, Mis-souri, October 10-15, 1998, pp. 1424-1431.

[22]Samir Kouro, IEEE, Pablo Lezana, Mauricio Angulo, and José Rodríguez, "MulticarrierPWMWith DC-Link Ripple Feedforward compensation for Multilevel Inverters" IEEE Transactions On Power Electronics, VOL. 23, NO. 1, JANUARY 2008. [23]Jang-Hwan Kim, Seung-Ki Sul and Prasad N. Enjeti, "A Carri-er-Based PWM Method with Optimal Switching Sequence for a Multi-level Four-

leg VSI" IEEE, June 2005, pp 99-105. for spwm,sfopwm,npc.

[24] B.Vamsi Krishna, A New Technique for Elimination of Harmonics Using Three Phase Shunt Active Filter, International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, ISSN (Online): 2278 - 8875, pp 5596-5602, Vol. 2, Issue 11, November 2013 [25] P.Thamarai, B.Karthik, ARM Based Automatic Meteorological Data Acquisition System, International Journal of Advanced Research in

Electrical, Electronics and Instrumentation Engineering, ISSN (Online): 2278 - 8875, pp 6461-6465, Vol. 2, Issue 12, December 2013 [26] M.Bharathi, Effective Transfer Function Approach for Decentralized Controller, International Journal of Advanced Research in Electrical,

Electronics and Instrumentation Engineering, ISSN 2278 - 8875, pp 21-27, Vol. 1, Issue 1, July 2012.

[27] Vijayan T , Energy-efficient MAC for Wireless Sensor Networks, International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, ISSN 2278 - 8875, pp 51-57, Vol. 1, Issue 1, July 2012.

[28] Sridhar raja. D & Suresh Kumar ,PLC application in automated Building Management System, International Journal of P2P Network Trends and Technology(IJPTT), ISSN (Print) : 2320 – 3765, pp 8339-8342, Vol. 3, Issue 4, April 2014.