(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 7, July 2014

### DOI: 10.15662/ijareeie.2014.0307010

# Five-Input Complex Gate with an Inverter Using QCA

Tina Suratkar<sup>1</sup>

Assistant Professor, Department of Electronics & Telecommunication Engineering, St. Vincent Pallotti College Of

Engineering and Technology, Nagpur, Maharashtra, India<sup>1</sup>

**ABSTRACT**: This paper presents the basics of quantum dot cellular automata along with the QCA logic devices such as the QCA wire, inverter and the majority gate. The four phases of the clocking have been discussed and also the implementations of the complex gate have been done using the QCADesigner tool. The logical structures such as NAND and NOR gates using a quantum dot cellular automata complex gate composed of 3 input majority gate and an inverter have been implemented.

**KEYWORDS:** QCA, majority gate, inverter, complex gates, QCA Designer.

### **I.INTRODUCTION**

Current silicon transistor technology faces challenging problems, such as high power consumption and difficulties in feature size reduction. Nanotechnology is an alternative to these problems. The Quantum dot cellular automata (QCA) is one of the attractive alternatives [1]. Since QCAs were introduced in 1993 by lent et al, and experimentally verified in 1997. QCA is expected to achieve high device density, extremely low power consumption and very high switching speed.QCA structures are constructed as an array of quantum cells with in which every cell has an electrostatic interaction with its neighboring cells [2]. QCA applies a new form of computation, where polarization rather than the traditional current, contains the digital information. In this trend, instead of interconnecting wires, the cells transfer the information throughout the circuit [4].

This paper describes the design of different logical structures in QCA such as NAND and NOR. These structures are designed based on the basic logical devices. The paper is organized as follows, the background of QCA technology is explained in section 2. Section 3, provides the QCA clocking and section 4 describes the QCA Designer tool. Section 5 shows the design and implementation of logical structures in QCA using three input majority and an inverter. Simulation results follow in section 6 and conclusions are presented in section 7.

### II.BACKGROUND

### A. QCA basics

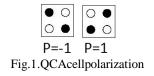

QCA technology is based on the interaction of bi-stable QCA cells constructed from four quantum dots. The cell is charged with two free electrons, which are able to tunnel between adjacent dots. These electrons tend to occupy antipodal sites as a result of their mutual electrostatic repulsion. Thus, there exist two equivalent energetically minimal arrangements of the two electrons in the QCA cell, as shown in Fig. 1. These two arrangements are denoted as cell polarization P = +1 and P = -1.By using cell polarization P = +1 to represent logic "1" and P = -1 to represent logic "0," binary information is encoded in the charge configuration of the QCA cell [2][5].

(An ISO 3297: 2007 Certified Organization)

Vol. 3, Issue 7, July 2014

#### B. QCA logic devices

#### DOI: 10.15662/ijareeie.2014.0307010

The fundamental QCA logic primitives include a QCA wire, QCA inverter, and QCA majority gate[4]-[6], as described below.

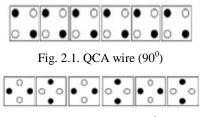

QCA Wire: In a QCA wire, the binary signal propagates from input to output because of the electrostatic interactions between cells. The propagation in a 90° QCA wire is shown in Fig. 2. Other than the 90° QCA wire, a 45° QCA wire can also be used. In this case, the propagation of the binary signal alternates between the two polarizations [4].

Fig. 2.2 QCA wire  $(45^{\circ})$

*QCA inverter:* The QCA cells can be used to form the primitive logic gates. The simplest structure is the inverter shown. Fig. 3, which is usually formed by placing the cells with only their corners touching. The electrostatic interaction is inverted, because the quantum-dots corresponding to different polarizations are misaligned between the cells [3].

Fig. 3.QCA inverter

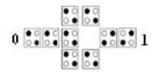

$\label{eq:gamma} QCAMa jority Gate: The QCA majority gate performs a three-input logic function. A layout of a QCA majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the input sarea, bandc, the logic function of the majority gate is shown in Fig. 4.1. Assuming the majority gate is shown in Fig. 4.1. Assuming the majority gate is shown in Fig. 4.1. Assuming the majority gate is shown in Fig. 4.1. Assuming the majority gate is shown$

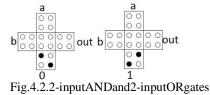

Thetendencyofthemajoritydevicecelltomovetoagroundstateensuresthatittakesonthepolarizationofthemajorityofitsneighb ours. Thedevicecellwilltendtofollowthemajoritypolarizationbecauseitrepresentsthelowestenergystate[3].Byfixingthepola rizationofoneinputtotheQCAmajoritygateaslogic "1" orlogic "0" anANDgateorORgatewillbeobtained, respectively, as shown in Fig. 4.2.

(An ISO 3297: 2007 Certified Organization)

### Vol. 3, Issue 7, July 2014

### DOI: 10.15662/ijareeie.2014.0307010

### **III.CLOCKING**

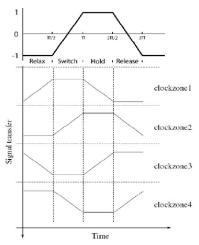

The QCA circuits require a clock, not only to synchronize and control information flow but also to provide the power torun the circuit ts ince there is no external source for powering cells. With the use of four phases clocking scheme incontrol ling cells, QCA processe sand forwards information within cells in an arranged timing scheme. Cells can be grouped into zoness othat the field influencing al the cells in the zones will be the same. A zone cycles through 4 phases. In the**Switch**phase, the tunneling barriers in a zone are raised. While this occurs, the electrons within the cell can be influenced by the Columbic charges of neighboring zones. Zones in the**Hold**phase have a high tunneling barrier and will not change state, but influence other adjacent. Lastly, the**Release**and**Relax**decrease the tunneling barriers othat the zone will not influence other zones. These zones can be of irregular shape, but the irsizem us the within certain limits imposed by fabrication and dissipation concerns. Proper placement of the sezone siscritical to design efficiency. This clocking method makes the design of QCA different from CMOS circuits. [7].

The Fig. 5. Shows the four available clock signals. Each signal is phase shifted by 90° degrees. When the clock signal is low the cells a relatched. When the clock signal is high the cells are relaxed and have no polarization. In between the cells are either latching or relaxing when the clock is decreasing/increasing respectively.

Fig. 5.Four phases of the clock.

#### **IV.QCA DESIGNER TOOL**

QCA logic and circuit designers require a rapid and accurate simulation and design layout tool to determine the functionality of QCA circuits. QCADesigner gives the designer the ability to quickly layout a QCA design by providing an extensive set of CAD tools. As well, several simulation engines facilitate rapid and accurate simulation. It is the first publicly available design and simulation tool for QCA. Developed at the ATIPS Laboratory, at the University of Calgary, QCADesigner currently supports three different simulation engines, and many of the CAD features required for complex circuit design. [8],[9].

#### V. QCA IMPLEMENTATION

The AND and OR gates are realized by fixing the polarization to one of the inputs of the majority gate to either  $P=-1(\log c 0)$  or  $P=1(\log c 1)$ .

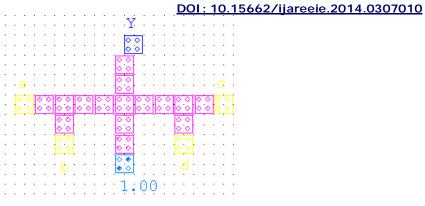

The same logic is used in the five-input complex gate with an inverter. This gate is composed of a 3-input majority gate which is placed in the middle of the complex gate. Here the input 'e' functions as a control input that is used to specify the functionality of the circuit. The remaining four inputs a, b, c and d are used to implement logical functions such as AND and OR. This implementation along with an inverter gives the logical functions NAND and NOR. The two cell-

(An ISO 3297: 2007 Certified Organization)

### Vol. 3, Issue 7, July 2014

### DOI: 10.15662/ijareeie.2014.0307010

inverter is created by translating the output cell 'Y' by 9 nm horizontally. The functionality of this gate for four input NAND and NOR configurations has been simulated using QCA Designer. Fig. 6 shows five-input complex gate with a majority gate placed in the middle and a two cell-inverter made by translating the output Y.

| • •                                            | •        | ·   | • | •        | •        | • | • | •  | • | •        |            | ÷  | • | • | •   | •   | •          | •   | • | •        |          |

|------------------------------------------------|----------|-----|---|----------|----------|---|---|----|---|----------|------------|----|---|---|-----|-----|------------|-----|---|----------|----------|

| • •                                            | •        | •   | • | •        | •        | • | • | •  | • | •        | ٠I         | •  | • | • | •   | •   | •          | •   | • | •        | • •      |

| • •                                            | ·        | ·   | • | •        | •        | • | • | •  | • | •        |            | 5  |   | • | •   | •   | •          | •   | • | •        | • •      |

|                                                |          |     | • |          |          | • | • | •  |   |          | Ľ.         | ХI |   | • |     | •   |            |     |   |          |          |

|                                                |          |     |   |          |          |   |   |    |   | -        | Ľ,         | ž  |   |   |     |     |            |     |   |          |          |

|                                                |          |     |   |          |          |   |   |    |   | 12       | . <u>°</u> |    |   |   |     |     |            |     |   |          |          |

|                                                |          |     |   |          |          |   |   |    |   | <u>Ľ</u> | ~          |    |   |   |     |     |            |     |   |          |          |

|                                                | a        |     |   |          |          |   |   |    |   | .0       | .°         |    |   |   |     |     |            |     |   | . C      | : .      |

|                                                | <u> </u> |     |   |          |          |   |   |    |   | <u>e</u> | 0          |    |   |   |     |     |            |     |   |          |          |

|                                                | 00       | 0   | 0 | 0        | 0        | 0 | 0 | ि  | 0 | ि        | 0          | 0  | 0 | 0 | 0   | 0   | 0          | 0   | 0 | े        | <u> </u> |

|                                                | 00       | 0   | 0 | 0        | 0        | 0 | 0 | ∣⊙ | 0 | <u> </u> | 0          | 0  | 0 | 0 | 0   | 0   | 0          | 0   | 0 | <u> </u> | 0        |

| • •                                            |          |     |   | 0        | 0        |   |   |    |   | 0        | 0          | (  |   |   |     | 0   | 0          |     |   |          | • •      |

| • •                                            | •        | •   | • | 0        | 0        |   | • | •  | • | 0        | 0          |    | • | • | •   | 0   | 0          |     | • | •        | • •      |

| • •                                            | •        | •   | • | 0        | 0        |   | • | •  | • | ত        | 0          | Ċ. | • | • | •   | ত   | 0          |     | • | •        | • •      |

| • •                                            | •        | •   | • | 0        | 0        |   | • | •  | • | 0        | 0          |    | • | • | •   | 0   | 0          |     | • | •        | • •      |

| • •                                            | ·        | •   | • | <u> </u> |          | • | • | •  | • | 5        | 0          |    | • | • | •   | _   |            |     | • | •        | • •      |

| • •                                            | •        | ·   | • | · ]      | 5        | • | • | •  | • | 16       | 6          |    | • | • | •   | • ( | <u>d</u> . | •   | • | •        |          |

| • •                                            |          | ·   | • | • •      | <u> </u> |   | • | ·  | • | <u> </u> |            |    |   | • |     |     | •          |     | • | •        |          |

|                                                |          |     |   |          |          |   |   |    |   | - 6      | 5          |    |   |   |     |     |            |     |   |          |          |

| ·                                              |          | ÷ _ | ÷ | •        |          |   |   |    |   | · _`     |            |    |   |   | • . | •   |            | • . |   |          |          |

| Fig.6 Five-Input complex gate with an inverter |          |     |   |          |          |   |   |    |   |          |            |    |   |   |     |     |            |     |   |          |          |

### A. Four-Input NAND Gate

The five-input gate of Fig. 6 can be used to form a 4-input NAND gate as shown in Fig. 7.1 by restricting input e to have a fixed polarity that is equal to -1. The selection of e is unique, either a or b can be restricted rather than e, and similarly c or d can be selected for restriction rather than g. For the example circuit as shown in Fig. 8, the function represented is  $Y=\overline{abcd}$

|   |                              |     |    |     |            |          |     |          |   |          |    | Y        | 2  |          |    |          |          |          |   |            |     |          |   |   |

|---|------------------------------|-----|----|-----|------------|----------|-----|----------|---|----------|----|----------|----|----------|----|----------|----------|----------|---|------------|-----|----------|---|---|

| · | ·                            | ·   | ·  | ·   | •          | •        | •   | •        | • | •        | •  | 5        | -  | r i      |    | •        | •        | •        |   | ·          | ·   | ·        | · | · |

|   |                              |     |    |     |            |          |     |          |   |          |    | 2        | 2  |          |    |          |          |          |   |            |     |          |   |   |

|   |                              |     |    |     |            |          |     |          |   |          | -  | Ĕ        | ř  |          |    |          |          |          |   |            |     |          |   |   |

|   |                              |     |    |     |            |          |     |          |   |          | 12 | <u>.</u> |    |          |    |          |          |          |   |            |     |          |   |   |

|   |                              |     |    |     |            |          |     |          |   |          | Ľ  | ~        |    |          |    |          |          |          |   |            |     |          |   |   |

|   |                              | a   |    |     |            |          |     |          |   |          | 12 | 2        | L  |          |    |          |          |          |   |            | . ( | 2        |   |   |

|   |                              |     |    |     |            |          |     |          |   |          | _으 | <u>~</u> |    |          |    |          |          |          |   |            |     |          |   |   |

|   | 1                            | 0.0 | 1  | 0.0 | l o        | ۰.       | 0   | .0       | 0 | .•       | 0  | <u>,</u> | 0  | <u>,</u> | 0  | <u>,</u> | 0        | .•       | 0 | <u>,</u> ° | 0   | .0       | L |   |

|   | 19                           | 2.0 | 12 | 0   | <u>ا</u> ا | <u>•</u> | l٥  | <u>_</u> | 0 | <u> </u> | P  | <u> </u> | P  | <u> </u> | 0  | <u>^</u> | 0        | <u> </u> | P | <u>_</u>   | P   | <u>_</u> | Ļ |   |

|   |                              |     |    |     | 0          | 0        | l   |          |   |          | 0  | 0        |    |          |    |          | 0        | 0        |   |            |     |          |   |   |

|   |                              |     |    |     | 0          | 0        | [   |          |   |          | 0  | 0        | [  |          | -  |          | 0        | 0        |   |            |     |          |   |   |

| • | •                            | •   | •  | •   | 0          | 0        | Ĺ   |          | • | •        | 0  | 0        | Ĺ  |          | •  | •        | 0        | 0        | ĺ | •          | •   | •        | • | · |

| • | ·                            |     | •  | •   | 0          | ۲        | í – |          | • | •        | 0  | 0        | 1  |          | •  | •        | <u> </u> | 0        |   | •          | •   | •        | • |   |

| • |                              |     | •  | •   | Ċ.,        |          |     |          | • | •        | ۲  | 0        | Ì. |          |    | •        | <u> </u> |          |   |            |     | •        |   |   |

| • | •                            |     | •  | •   | 1          | б.       |     |          | • |          | 6  | ٠        |    |          | •  | •        | 1 (      | 1        |   |            |     | •        | • | 1 |

| • | ·                            | •   | •  | •   |            |          | •   | •        | • | •        |    | •        |    | ۰.       |    |          |          | •        | • | •          | ·   | •        | • | · |

| · | ·                            | •   | ·  | ·   | •          | •        | •   |          | • | •        | •  | - 1      | 1. | : (      | 90 | )        |          | •        | • | •          | ·   | ·        | • | · |

| • |                              |     | •  | ·   |            | •        |     |          | • | •        | •  |          | •  |          |    |          |          | •        |   |            | •   | •        | • |   |

|   | Fig.7.1 Four input NAND gate |     |    |     |            |          |     |          |   |          |    |          |    |          |    |          |          |          |   |            |     |          |   |   |

## B. Four-Input NOR Gate

Similarly, the five-input gate of Fig. 6 can also be used to form a 4-input NOR gate as shown in Fig. 7.2. For this configuration the input e is restricted to have a fixed polarity that is equal to 1. As for the NAND gate, the selection of e is unique The function represented is  $Y=\overline{a+b+c+d}$

(An ISO 3297: 2007 Certified Organization)

### Vol. 3, Issue 7, July 2014

Fig. 7.2 Four input NOR gate

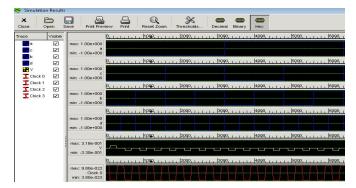

#### VI.SIMULATION RESULTS

With QCADesigner, the circuit functionality is verified. The following parameters are used for a bistable approximation: Cell size 18nm, Number of samples 12800, Convergence tolerance 0.001000, Radius of effect 65nm, Relative permittivity 12.9, Clock high 9.8e-22J, Clock low3.8e-23J, Clock amplitude factor2, Layer separation 11.5nm, Maximum Iterations per sample 100.

| 🎯 Simulation Results   |                                             |                    |                          |                           |                                         |                    |                        |                                                     |

|------------------------|---------------------------------------------|--------------------|--------------------------|---------------------------|-----------------------------------------|--------------------|------------------------|-----------------------------------------------------|

|                        | ave Print Previe                            | w Print            | Reset Zoom               | X<br>Thresholds           | Decimal                                 | Binary Hex         |                        |                                                     |

| Trace Visible          | max: 1.00e+000                              | بابابابا           | 1pqo, <sub>1 , 1 ,</sub> | , j2pqo, <sub>1</sub> , , | H , I ,  3090,                          | L , L , L ,  4pqo, | 1.1.1. <b> </b> 5090,1 | , <sub>1</sub> , <sub>1</sub> ,  eçqo, <sub>1</sub> |

|                        | min: -1.00e+000                             |                    | 1000                     | 2000, <del>_</del>        | H., I, 3000,                            | L. L. L.  40QO,    | 1                      |                                                     |

| V V<br>Clock 0 V       | max: 1.00e+000<br>c<br>min: -1.00e+000      |                    |                          |                           |                                         |                    |                        |                                                     |

| Clock 1 Z<br>Clock 2 Z | max: 1.00e+000                              | 41.1.1.1.          | 11000. 1. 1. 1.          | 2090,,•                   | н.,,  зрао,                             | L. L. L. (4090,    | <b> </b> 5990          | eçqo, .                                             |

| T Clock 3 🗹            | b<br>min: -1.00e+000                        |                    | 11000                    | 2000                      | Isono                                   | 4000               | 1  spqo                | lenno                                               |

|                        | max: 1.00e+000<br>d                         |                    | 1000                     | 12000                     | , , , , , , , , , , , , , , , , , , , , | 1 1 1 1000         |                        |                                                     |

|                        | : =                                         | ).   .   .   .   . | 1000, 1, 1,              | 2000,                     | <b>+</b> , , ,  3000,                   | L , L , L ,  4pqo, | 1.1.1.  5090,1         | , , , , , , , , , , , , , , , , , , ,               |

|                        | max: 3.30e-001<br>Y<br>min: -3.18e-001      |                    |                          |                           |                                         |                    |                        | <u> </u>                                            |

|                        | max: 9.80e-022<br>Clock 0<br>min: 3.80e-023 |                    |                          | 1,  2999, 1, <b>.</b>     | 4 . I .  3090,                          |                    | 1, 1, 1, 1, 15pqp, 1   | , , , , , , , , , , , , , , , , , , ,               |

Fig.8.1 Simulation result for four input NAND gate

Fig.8.2 Simulation result for four input NOR gate

(An ISO 3297: 2007 Certified Organization)

### Vol. 3, Issue 7, July 2014

### DOI: 10.15662/ijareeie.2014.0307010

### VII.CONCLUSION

The logical structures such as NAND and NOR using five-input complex gate composed of a 3-input majority gate and a two cell inverter have been designed. One of these inputs typically function as control inputs to determine the logical structure formed by the four other inputs to the circuit. This five-input gate can be configured as a four-input NAND gate and a four-input NOR gate which are verified through simulation results.

#### REFERENCES

- [1] C.S.Lent, P.D.Tougaw, W.Porod, and G.H.Bernstein, "Quantum cellular automata, "Nanotechnology, vol.4, no.1, pp.49–57, January 1993.

- P.D.Tougaw, C.S.Lent, and W.Porod, "Bistable saturation in coupled quantum-dot cells," *Journal of Applied Physics*, vol.74, no.5, pp.3558–3566, September1, 1993.

- P.D.Tougaw and C.S.Lent, "Logical devices implemented using quantum cellular automata, "Journal of Applied Physics, vol.75, no.3, pp.1818–1825, February1, 1994.

- [4] C.S.Lent and P.D.Tougaw, "Lines of interacting quantum-dot cells: A binary wire," *Journal of Applied Physics*, vol.74, no.10, pp.6227–6233, November15, 1993.

- [5] C.S.Lent, P.D.Tougaw, and W.Porod, "Bistable saturation in coupled quantum dots for quantum cellular automata," *Applied Physics Letters*, vol.62, no.7, pp.714–716, February 15, 1993.

- [6] C.S.Lent and P.D.Tougaw, "A device architecture for computing with quantum dots," *Proceedings of the IEEE*, vol.85, no.4, pp.541–557, April 1997.

- [7] S.Karthigai Lakshmi, G.Athisha, "Efficient design of logical structures and functions using nanotechnology based quantum dot cellular automata design," *International Journal of Computer Applications*, vol.3, no.5, (0975-8887), June 2010.

- [8] *QCADesigner*, version 1.3.2. Available at <u>http://www.atips.ca/projects/qcadesigner/</u>.

[9] K. Walus, T. Dysart, G. Jullien, and R. Budiman, "QCADesigner: A rapid design and simulation tool for quantum-dot cellular automata, *"IEEE Trans. Nanotechnol.*, vol. 3, no. 1, pp. 26–29, Mar. 2004