## International Journal of Advanced Research

in Electrical, Electronics and Instrumentation Engineering

Volume 11, Issue 7, July 2022

ø

9940 572 462

Impact Factor: 8.18

6381 907 438 🛛 🖂 ijareeie@gmail.com 🛛 🙆 www.ijareeie.com

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 8.18|

Volume 11, Issue 7, July 2022

|DOI:10.15662/IJAREEIE.2022.1107016|

### Performance Analysis of T-Type Inverters Using SVPWM Control Technique

Dr. H.R. Ramesh<sup>1</sup>, Poornesh V Mahishi<sup>2</sup>

Professor, Department of Electrical Engineering, UVCE Bangalore, India.<sup>1</sup>

PG Scholar [Power Electronics], Department of Electrical Engineering, UVCE Bangalore, India.<sup>2</sup>

**ABSTRACT**: A power electronics device which converts DC power to AC power at required output voltage and frequency level is known as an inverter. Two categories into which inverters can be broadly classified are two level inverters and multilevel inverters. Some advantages that multilevel inverters have compared to two level inverters are minimum harmonic distortion, reduced EMI/RFI generation, and operation on several voltage levels. A multilevel inverter can be utilized for multipurpose applications, such as an active power filter, a static VAR compensator and a machine drive for sinusoidal and trapezoidal current applications. Some drawbacks to the multilevel inverters are the need for isolated power supplies for each one of the stages and they are more expensive. The proposed paper focuses on reduction of conduction losses at the output of T-type multi-level inverter topology. The neutral point voltage balancing of the circuit is performed using redundant vectors of three level space vector diagram. Since the number of switches are reduced and single switching takes place per transition in SVPWM technique, the switching losses will get reduced to a considerable range. The above work is simulated using MATLAB / Simulink software. The experimental verification is carried out and the output waveforms are obtained.

KEYWORDS: SVPWM, Multilevel Inverters, T-Type Inverters, Conduction Losses, Reduced Device Count.

#### **I.INTRODUCTION**

The trend on providing electricity for cleaner environment has influenced the need for electric power in different forms. Power electronics in electrical engineering is a subject as a whole which has seen more technical enhancement and has impacted almost every sphere of human life. Power electronics has evolved as a key domain of electric power engineering and has got close bonding with different other disciplines like semiconductor engineering, network theory, analog electronics and digital electronics. Along with these, control systems, electrical machines, electrical power systems, electronics theory etc are also connected with power electronics. The basic definition of power electronics is "control, regulation, conversion and conditioning of power". In recent times the most compelling advances in power electronics are **inverters**.

There are numerous applications where we will be having AC power load which needs to be powered from a DC power source. Generally renewable energy resource like solar PV cells are used to synthesis DC power where inverters are put in action to obtain AC power.

The paper proposed in [1] uses modified sinusoidal PWM technique to reduce the switching losses in T-type inverters, however neutral point balancing is difficult for the circuits like T-type inverters using this control technique. The paper proposed in [2] uses the concept of reduced device count for T-type inverters by modifying the switches placed between clamped neutral and load into a single switch, also reduced device count concept makes T-Type inverter more compatible with economical cost structure and there is no effect of reduced device count on output of T-Type converter. This paper focuses on reduction of overall conduction losses by reducing the number of switching devices used and by using modified SVPWM control technique.

#### **II. COMPARISON OF CONVENTIONAL AND PROPOSED MODIFIED T-TYPE INVERTER**

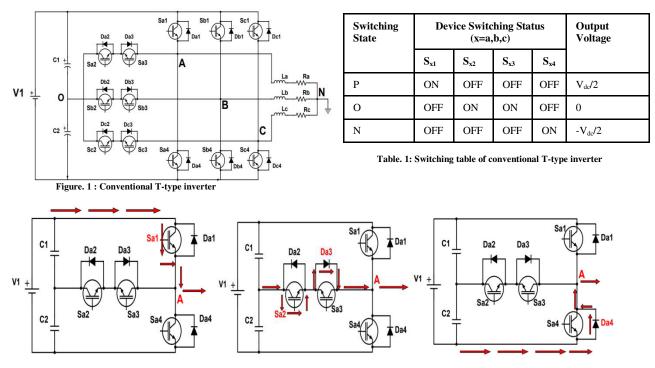

The T-Type inverters are originated by the modification of neutral point clamped (NPC) multilevel inverters. The working principle of T-type inverters remains same as NPC inverters. The conventional T-type inverter topology is as given in figure 1. Here 12 number of power devices are used, 12 number of diodes are used, 2 number of DC link capacitors are used and single DC supply is used. The switching table for this circuit is given in table 1. The possible three levels of outputs of this circuit are  $[+V_{DC}/2, 0, -V_{DC}/2]$ . Consider any one phase of the inverter. To obtain the positive state of output  $[+V_{DC}/2]$ , the switch connected to the positive rail must be turned ON as given in figure 2a. Hence this switching state is called positive switching state and is represented as **'P'**. Likewise to obtain zero state of

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 8.18|

||Volume 11, Issue 7, July 2022||

#### DOI:10.15662/IJAREEIE.2022.1107016

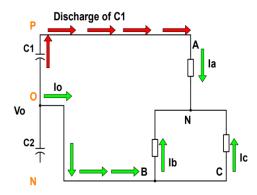

the output [0], the switches connected to the neutral point must be turned ON. Hence this switching state is called zero switching state and is represented as '**O**'. Similarly to obtain negative state of the output  $[-V_{DC}/2]$ , the switch connected to the negative rail must be turned ON. Hence this switching state is called negative switching state and is represented as '**N**'. Working of the circuit considering the flow of the current in one of the three phases is explained in figure 2.

Figure. 2a,2b & 2c: Switching of conventional T-type inverter.

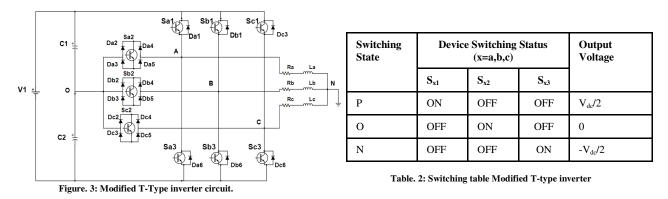

The modified T-type inverter topology is as given in figure 3. Here 9 number of power devices are used, 18 number of power diodes are used, 12 number of DC link capacitors are used and single DC supply is used. The switching table for this circuit is given in table 2. The possible three levels of outputs of this circuit are  $[+V_{DC}/2, 0, -V_{DC}/2]$ . Hence this switching state is called positive switching state and is represented as '**P**'. Likewise to obtain zero state of the output [0], the switches connected to the neutral point must be turned ON. Hence this switching state is called zero switching state and is represented as '**O**'. Similarly to obtain negative state of the output  $[-V_{DC}/2]$ , the switch connected to the negative rail must be turned ON. Hence this switching state and is represented as '**N**'. Working of the circuit considering the flow of the current in one of the three phases is explained in figure 4.

e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765 www.ijareeie.com | Impact Factor: 8.18

#### ݙݯݠݜ IJĂREEIE

Volume 11, Issue 7, July 2022

DOI:10.15662/IJAREEIE.2022.1107016

Figure. 4a, 4b & 4c : Switching of modified T-type inverter.

#### **III.SVPWM CONTROL TECHNIQUE**

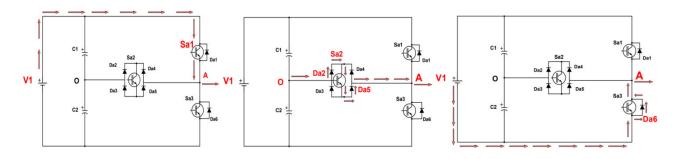

The three level space vector diagram is as shown in figure 5(a). There are total 27 number of switching states in a three level space vector diagram which is explained with the help of table 3. Based on magnitude of space vectors, four categories of vectors are found in a three level space vector diagram. The four categories of Space Vectors are Zero vectors, Small vectors, Medium vectors and Large vectors.

The grand hexagon is divided into six small hexagons as shown in figure 5(b). These small hexagons are called **sub-hexagons**. In order to synthesize the resultant vector, each sub-hexagon can be split into 6 parts which are called **sub-sectors**. The resultant vector is synthesized by using these sub-hexagons and sub-sectors. To simplify into the space vector diagram of a two-level inverter, the following two steps have to be taken. First, from the location of a given reference voltage, one sub-hexagon has to be selected among the six sub-hexagons. Secondly the original reference voltage vector has to be subtracted by the amount of the centre voltage vector of the selected sub-hexagon. By these two steps, the three-level space vector plane is transformed into the two-level space vector plane.

Then the determination of switching sequence and the calculation of the voltage vector duration time are done as conventional two-level SVPWM method. As the proposed SVPWM method is same in principle as conventional two-level SVPWM, various techniques used in two-level SVPWM can be applied to this proposed method too.

Figure. 5: Representation of three level space vector diagram.

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 8.18|

#### ||Volume 11, Issue 7, July 2022||

#### DOI:10.15662/IJAREEIE.2022.1107016

| VECTOR<br>TYPE | MAGNITUDE                 | SWITCHI | NG STATE | NEUTRAL POINT CURRENT           |                |  |  |

|----------------|---------------------------|---------|----------|---------------------------------|----------------|--|--|

| ZERO           | 0                         | [P]     | PP]      |                                 |                |  |  |

| VECTOR         |                           | [00     | 00]      | -                               |                |  |  |

|                |                           | [N]     | NN]      | -                               |                |  |  |

| SMALL          | $\frac{1}{3}V_{D}$        | P-TYPE  | N-TYPE   | P-TYPE                          | N-TYPE         |  |  |

| VECTOR         | VECTOR                    |         | [ONN]    | $I_b + I_c$                     | Ia             |  |  |

|                |                           | [PPO]   | [OON]    | Ic                              | $I_a + I_b$    |  |  |

|                |                           | [OPO]   | [NON]    | I <sub>a</sub> + I <sub>c</sub> | I <sub>b</sub> |  |  |

|                |                           | [OPP]   | [NOO]    | Ia                              | $I_b + I_c$    |  |  |

|                |                           | [POP]   | [ONO]    | I <sub>b</sub>                  | $I_a + I_c$    |  |  |

|                |                           | [OOP]   | [NNO]    | $I_a + I_b$                     | Ic             |  |  |

| MEDIUM         | $\frac{\sqrt{3}}{3}V_{D}$ | [PC     | DN]      | I <sub>b</sub>                  |                |  |  |

| VECTOR         | 3                         | [0]     | PN]      | Ia                              |                |  |  |

|                |                           | [NI     | 20]      | Ic                              |                |  |  |

|                |                           | [N0     | OP]      | I <sub>b</sub>                  |                |  |  |

|                |                           | [0]     | NP]      | Ia                              |                |  |  |

|                |                           | [PN     | 10]      | Ic                              |                |  |  |

| LARGE          | LARGE $\frac{2}{3}V_D$    |         | IN]      |                                 |                |  |  |

| VECTOR         | 3                         | [PI     | PN]      |                                 |                |  |  |

|                |                           | [NI     | PN]      |                                 |                |  |  |

|                |                           | [N]     | PP]      | 1                               |                |  |  |

|                |                           | [NI     | NP]      | 1                               |                |  |  |

|                |                           | [P]     | NP]      | 1                               |                |  |  |

Table. 3 : Different types of space vectors of three level space vector diagram.

#### **IV.NEUTRAL POINT VOLTAGE BALANCING**

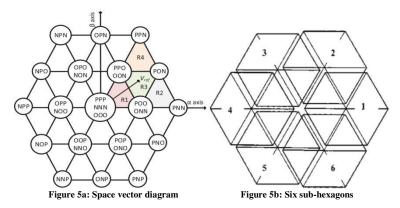

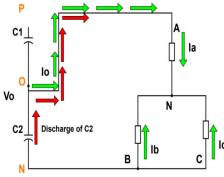

The neutral point voltage balancing is mainly due to the uneven charging and discharging of DC link upper and lower capacitors. Firstly let us understand why does neutral point voltage fluctuates? The answer for this question is when we access the mid-point (neutral point) for our switching, the voltage at the midpoint fluctuates. This voltage fluctuation depends on the direction of current at the mid-point (which in turn depends on whether the capacitors are getting charged or discharged). The direction of current depends on the switching states we choose. This can be explained with the help of an example as given below.

Consider a switching state [POO] as shown in figure 6. When the current is flowing from source to load  $(i_a > 0)$

Figure. 6: Circuit of POO switching state.

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 8.18|

#### Volume 11, Issue 7, July 2022

#### DOI:10.15662/IJAREEIE.2022.1107016

For a balanced load  $(i_a + i_b + i_c = 0)$  and  $(i_b + i_c = -i_a)$  from figure  $(i_a = -i_0)$ . Hence the upper capacitor  $C_1$  starts discharging and  $V_0$  (mid-point voltage) goes up assuming total DC bus voltage is constant. More fluctuations leads to more harmonic distortion in the output and further uneven charging and discharging will put the capacitors and power switches at great risk and deteriorate the inverter performance. Possible solutions are additional balancing circuit which add cost and complicates therefore it is not widely used. The solution for this problem is by using the concept of multiplicity or degree of freedom since it is observed that these redundant switching states (alternative switching states) affect the mid-point voltage oppositely. For example consider a switching state **[ONN].** This is the redundant vector of **[POO]** which we had explained previously. Now let us see how oppositely does [ONN] affect the mid-point voltage. When the current is flowing from source to load ( $i_a > 0$ ) as shown in figure 7.

Figure. 7: Circuit of ONN switching state.

For a balanced load  $(i_a + i_b + i_c = 0)$  and  $i_a = -(i_b + i_c)$  from figure  $(i_0 = i_a)$ . Hence the lower capacitor C<sub>2</sub> starts discharging and V<sub>0</sub> (midpoint voltage) goes down assuming total DC bus voltage is constant. From these two examples we can say that the redundant vectors affect the neutral point voltage in opposite fashion. Therefore we can say that with redundant vectors we can balance the neutral point voltage that is by using one of the redundant vector for one switching time period TPWM and other redundant vector for the next switching time period so that the mid-point voltage remains constant.

#### V. RESULT AND DISCUSSION

The results of MATLAB simulation implementing space vector pulse width modulation to both conventional T-type

inverter and modified T-type inverter (proposed circuit topology) are as given below.

#### Results for Modified T-Type Circuit Topology with RL load.

The results of simulations considering resistive inductive load with theoretically calculated values which is, output power of  $P_{out} = 30$ KW, output phase voltage of 240V, power factor of 0.9, resistance of  $R = 5.42 \Omega$  and inductance value taken as L = 4.32 mH for a modified T-Type inverter is explained here. The conduction losses for the proposed circuit considering internal resistance of the switch to be  $R_{int} = 1m\Omega$  is given in table 4. The waveforms of phase current, phase voltage, line voltage and neutral point voltage balancing are given in figure 8a, 8b, 8c & 8d.

| PARAMETERS                           | S <sub>A1</sub> | S <sub>A2</sub> | S <sub>A3</sub> | S <sub>B1</sub> | S <sub>B2</sub> | S <sub>B3</sub> | S <sub>C1</sub> | S <sub>C2</sub> | S <sub>C3</sub> |

|--------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| i <sub>rms</sub>                     | 29.38           | 19.28           | 29.5            | 29.47           | 19.17           | 29.58           | 29.54           | 18.84           | 29.68           |

| $i^2_{\rm rms} \mathbf{R}_{\rm int}$ | 0.863           | 0.372           | 0.87            | 0.868           | 0.367           | 0.875           | 0.873           | 0.355           | 0.88            |

| OVERALL CONDUCTION LOSSES = 6.323 W  |                 |                 |                 |                 |                 |                 |                 |                 |                 |

Table. 4: Conduction losses calculated for modified T-type inverter with RL load.

The efficiency is calculated using the values of I<sub>in</sub> = 53.64A, V<sub>in</sub> = 700V, I<sub>out</sub> = 45.74A, V<sub>out</sub> = 467.6V and cos  $\phi = 0.9$ . Efficiency ( $\eta$ ) % =  $\frac{Pout}{Pin}$  x 100 =  $\frac{35933.8}{37548}$  x 100 = **95.7**%.

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 8.18|

||Volume 11, Issue 7, July 2022||

|DOI:10.15662/IJAREEIE.2022.1107016|

Total harmonic distortion THD obtained is as follows. For Line Currents = 6.28%, Line Voltages = 35.81% and Phase Voltages = 36.53%.

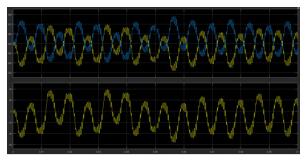

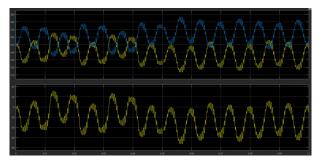

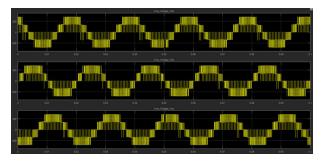

Figure. 8a: Obtained phase voltages of modified topology considering RL load.

Figure. 8b: Obtained phase currents of modified topology considering RL load.

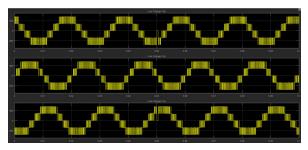

Figure. 8c: Obtained neutral point voltage balancing of modified topology considering RL load.

Figure. 8d: Obtained line voltages of modified topology RL load.

#### Results for Conventional T-Type Circuit Topology with RL load.

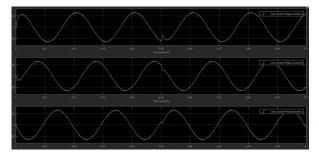

The results of simulations considering resistive inductive load with theoretically calculated values which is, output power of  $P_{out} = 30$ KW, output phase voltage of 240V, power factor of 0.97, resistance of  $R = 5.42 \Omega$  and inductance value taken as L = 4.32 mH for a conventional T-Type inverter is explained here. The conduction losses for the proposed circuit considering internal resistance of the switch to be  $R_{int} = 1m\Omega$  is given in table 5. The waveforms of phase current, phase voltage, line voltage and neutral point voltage balancing are given in figure 10a, 10b, 10c & 10d.

| PARAMETERS                           | S <sub>A1</sub> | S <sub>A2</sub> | S <sub>A3</sub> | S <sub>A4</sub> | S <sub>B1</sub> | S <sub>B2</sub> | S <sub>B3</sub> | S <sub>B4</sub> | S <sub>C1</sub> | S <sub>C2</sub> | S <sub>C3</sub> | S <sub>C4</sub> |

|--------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| i <sub>rms</sub>                     | 29.12           | 19.13           | 19.13           | 29.55           | 29.2            | 19.03           | 19.03           | 29.62           | 29.27           | 18.7            | 18.7            | 29.73           |

| $i^2_{\rm rms} \mathbf{R}_{\rm int}$ | 0.848           | 0.366           | 0.366           | 0.873           | 0.853           | 0.362           | 0.362           | 0.877           | 0.857           | 0.35            | 0.35            | 0.884           |

| OVERALL CONDUCTION LOSSES = 7.348 W  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

Table 5: Conduction losses calculated for conventional T-type inverter with RL load.

The efficiency is calculated using the values of  $I_{in} = 53.17$ A,  $V_{in} = 700$ V,  $I_{out} = 45.68$ A,  $V_{out} = 467.7$ V and  $\cos \phi = 0.9$ .

Efficiency ( $\eta$ ) % =  $\frac{Pout}{Pin}$  x 100 =  $\frac{35894.33}{37219}$  x 100 = **96.4**%.

Total harmonic distortion THD obtained is as follows. For Line Currents = 6.27%, Line Voltages = 36.23% and Phase Voltages = 37%.

e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765 www.ijareeie.com | Impact Factor: 8.18

||Volume 11, Issue 7, July 2022||

DOI:10.15662/IJAREEIE.2022.1107016

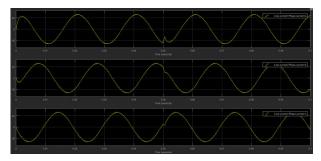

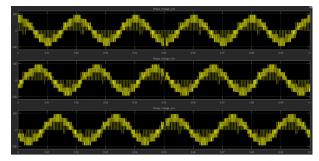

Figure 10a: Obtained phase currents of conventional topology considering RL load

Figure10b : Obtained neutral point voltage balance of conventional topology considering RL load.

Figure 10c: Obtained line voltages of conventional topology considering RL load.

Figure10d: Obtained phase voltages of conventional topology considering RL load.

#### VI.CONCLUSION

From the comparison of conduction losses of conventional T-type inverter with modified T-type inverter (proposed) using space vector pulse width modulation, it is observed that we achieve lower conduction losses in modified T-type inverter, with the same ratings and same output parameters for medium switching frequencies.

The neutral point voltage balancing of the circuit is performed using redundant vectors of three level space vector diagram and the simulation results are attached to the report. Since the number of switches can be reduced and single switching takes place per transition in SVPWM technique, the switching losses will also get reduced to a considerable range.

Theoretical calculations of efficiency, THD and conduction losses were compared with simulation results. The simulated waveforms of phase currents, line voltages, phase voltages and neutral point voltage balancing for RL load for each of the topology (conventional T-Type and modified T-Type topology) are verified.

#### References

- [1] V. Tran, T. Quach, D. Do, M. Nguyen, M. Le and N. Truong, "A Novel Offset Function for Three Level T-Type Inverter to Reduce Switching Loss," 2019 International Conference on System Science and Engineering (ICSSE), Dong Hoi, Vietnam, 2019, pp. 41-44, doi: 10.1109/ICSSE.2019.8823507.

- [2] C. L. Solanki, M. H. Ayalani and S. N. Gohil, "Performance of Three Phase T-Type Multilevel Inverter with Reduced Switch Count," 2018 International Conference on Current Trends towards Converging Technologies (ICCTCT), Coimbatore, India, 2018, pp. 1-5, doi: 10.1109/ICCTCT.2018.8550937.

- [3] M. Schweizer and J. W. Kolar, "Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications," in *IEEE Transactions on Power Electronics*, vol. 28, no. 2, pp. 899-907, Feb. 2013, doi: 10.1109/TPEL.2012.2203151.

- [4] H. M. Bassi, "A New PWM Technique for Cascade H-Bridge with Reduced Switching Losses," 2019 International Conference on Industrial Engineering, Applications and Manufacturing (ICIEAM), Sochi, Russia, 2019, pp. 1-5, doi: 10.1109/ICIEAM.2019.8742924.

| e-ISSN: 2278 – 8875, p-ISSN: 2320 – 3765| <u>www.ijareeie.com</u> | Impact Factor: 8.18|

#### Volume 11, Issue 7, July 2022

#### |DOI:10.15662/IJAREEIE.2022.1107016|

- [5] N. A. Rahim, M. F. M. Elias and W. P. Hew, "Transistor-Clamped H-Bridge Based Cascaded Multilevel Inverter With New Method of Capacitor Voltage Balancing," in *IEEE Transactions on Industrial Electronics*, vol. 60, no. 8, pp. 2943-2956, Aug. 2013, doi: 10.1109/TIE.2012.2200213.

- [6] A. Narendrababu, N. Yalla and P. Agarwal, "A modified T-type single phase five-level inverter with reduced switch voltage stress," 2018 International Conference on Power, Instrumentation, Control and Computing (PICC), Thrissur, India, 2018, pp. 1-5, doi: 10.1109/PICC.2018.8384775.

- [7] Z. Wang, X. Li, X. Xing, B. Duan and C. Zhang, "Simultaneous Switching Loss Reduction and Neutral-Point Voltage Balance Scheme for Single-Phase Three-Level T-Type Inverter," in *IEEE Transactions on Industry Applications*, vol. 56, no. 6, pp. 6687-6700, Nov.-Dec. 2020, doi: 10.1109/TIA.2020.3025845.

- [8] M. Aly and M. Shoyama, "An efficient neutral point voltage control algorithm with reduced switching losses for three level inverters," 2014 IEEE International Conference on Power and Energy (PECon), Kuching, Malaysia, 2014, pp. 330-335, doi: 10.1109/PECON.2014.7062466.

- [9] Schweizer, M.; Lizama, I.; Friedli, T.; Kolar, J.W.: "Comparison of the chip area usage of 2-level and 3-level voltage source converter topologies". In: IECON 2010-36th Annual Conference on IEEE Industrial Electronics Society, pp. 391–396 (2010).

- [10] High power multilevel converters- analysis, design and operational issues by Anandarup Das, IIT Delhi.

- [11] Two level and three level SVPWM for three phase inverters by Dr. Osama Arafa.

doi crossref

# International Journal of Advanced Research

in Electrical, Electronics and Instrumentation Engineering

www.ijareeie.com