(An ISO 3297: 2007 Certified Organization) Website: <u>www.ijareeie.com</u> Vol. 6, Issue 4, April 2017

# Low Power Multiplier Architectures Design Using Vedic Mathematics in 22nm Technology

Sushma S. Gadekar<sup>1</sup>, Mahesh S. Badmera<sup>2</sup>

PG Student, Department of E&TC, Deogiri Institute of Engineering & Management Studies, Aurangabad (MS), India<sup>1</sup>

Assistant Professor, Department of E&TC, Deogiri Institute of Engineering & Management Studies,

Aurangabad (MS), India<sup>2</sup>

**ABSTRACT**: This paper presents unsigned 8 x 8 high speed multiplier power and area efficient multipliers can be used in digital signal processor based applications. The high speed multipliers can be implemented by using Vedic mathematics mainly the "Urdhav Tiryakbhyam [3] "Multiplication requires more hardware and processing time than addition and subtraction. Vedic algorithm (sutras) reduces the number of computational steps as compared with any conventional method. In the proposed system, the schematic is designed using TANNER TOOL. The design is verified in T-SPICE using 22nm CMOS technology library file. The performance evaluation that the transistor requirement is reduced hence the area, also the power consumption and propagation delay is reduced.

**KEYWORDS:** Multipliers, Vedic Mathematics, Urdhav Tirakbhyam Sutra.

### I. INTRODUCTION

While designing any processor, the multiplier is basic building block. Multiplication process is used in many applications like communication, image processing, video processing, etc. To multiply two binary numbers a binary multiplier is used. Most multiplication techniques involve the process of adding a number of partial products. Many algorithms differ in the partial product generation and partial product addition to produce the final results (compare). The proposed system uses a multiplier based on the Vedic mathematics [3]. (The Vedic mathematics was rediscovered from 1911 to 1980 by Shri Bhatri Krishna Tirthaji Maharaj). Vedic mathematics contains 16 sutras.

This paper process the architecture which is based on Urdhva Tiryakbhyam. In this sutra the multiplication is based on vertically and cross wise operation.

This paper is organized in five sections. Section I gives a brief introduction, Section II technique of Vedic multiplication by using Urdhva Tiryakbhyam sutra. Section III Illustrates different multiplier design. Section IV presents experimental results of the proposed system and performance evaluation with previous systems. Section V concludes the paper.

### **II. VEDIC MATHEMATICS**

Vedic Mathematics comprises four Vedas. Vedic mathematics explains various mathematical terms which includes arithmetic, geometry, trigonometry, factorization and quadratic equations. The Vedic mathematics was rediscovered by Shri Bhatri Krishna Tirthaji Maharaj (1884 – 1960). Swamiji has given 16 sutras and its explanation with it application. These Sutras along with their meanings are enlisted below alphabetically.

- 1) Shunyamanyat If one is in ratio, the other is zero.

- 2) Chalana-Kalanabyham Differences and Similarities.

- 3) Ekadhikina Purvena By one more than the previous One.

- 4) EkanyunenaPurvena By one less than the previous one.

- 5) Gunakasamuchyah The factors of the sum is equal to the sum of the factors.

- 6) Gunitasamuchyah The product of the sum is equal to the sum of the product.

- 7) NikhilamNavatashcaramamDashatah All from 9 and last from 10.

- 8) ParaavartyaYojayet Transpose and adjust.

- 9) Puranapuranabyham By the completion or noncompletion.

(An ISO 3297: 2007 Certified Organization)

Website: www.ijareeie.com

### Vol. 6, Issue 4, April 2017

- 10) Sankalana- Vyavakalanabhyam By addition and by subtraction.

- 11) ShesanyankenaCharamena The remainders by the last digit.

- 12) ShunyamSaamyasamuccaye When the sum is the same that sum is zero.

- 13) Sopaantyadvayamantyam The ultimate and twice the penultimate.

- 14) Urdhva-Tiryakbhyam Vertically and crosswise.

- 15) Vyashtisamanstih Part and Whole.

- 16) Yaavadunam Whatever the extent of its deficiency.

This paper is discussed by using Urdhva Tiryakbhyam (UT) Sutra. It is seen that by using this sutra, the designing of faster and lower power multiplier circuits can be implemented. Urdhva Tiryakbhyam Sutra is a Sanskrit word which means vertically and crosswise explanation for 2-bit multiplication is as follows

#### a1 x b1 : a1 x b0 + a0 x b1 : a0 x b0

Similar type of 2-bit multiplication can be carried out for any digital numbers by using Urdhva Tiryakbhyam algorithm.

#### **III. DESIGN OF MULTIPLIER ARCHITECTURE**

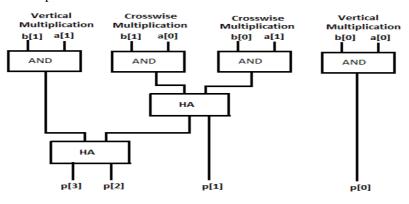

### A] Design 2-Bit Multiplier

The fundamental block for all types of multiplier design is a 2-bit multiplier. The proposed 2-bit multiplier comprises four AND gates and two 1-bit half adder blocks. The modified AND gate consists of five transistors which is having one less transistors as compared with the conventional multiplier [4]. The half adder used is designed with 9 transistors. Figure 1 shows the 2-bit multiplier.

Figure 1 Design of 2-bit Multiplier

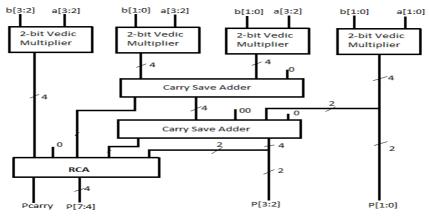

#### **B]** Design of 4-bit multiplier

The 4-bit multiplier is designed by suing four 2-bit multiplier and three 4- bit adders. The different blocks of a 4-bit multiplier are as shown in figure 2. Each adder consists of four full adders. The full adder is used in this design is having 14 transistors [4] [5]. With use of this new full adder it is observed that the speed of multiplication is improved with low power consumption. The conventional multipliers units comprise long adder chains which gives rise to more propagation delay. The 4-bit multiplier is used to have reduced propagation delay. As per the UT sutra the 4-bit input is applied to four 2-bit multiplier and the output is of 8-bit.

(An ISO 3297: 2007 Certified Organization)

Website: www.ijareeie.com

### Vol. 6, Issue 4, April 2017

Figure 2 Design of 4-bit Multiplier.

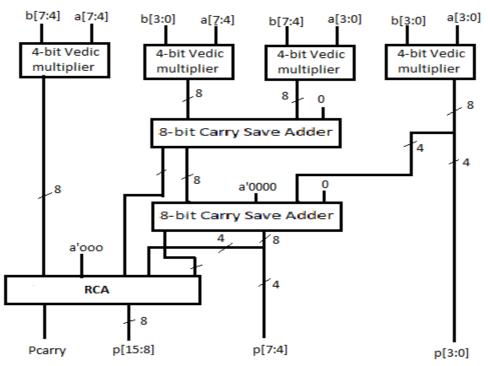

### C] Design of 8-bit multiplier

The proposed 8-bit multiplier is designed by using four 4-bit multiplier blocks and three 8-bit adders. The input to the 8-bit multiplier is 8-bit (Multiplicand) and the output obtained is of 16-bit wide. The output is applied to the four 4-bit multipliers. The output of 4-bit multipliers is given to the 8-bit adder.

Figure 3 Design of 8-bit Multiplier.

### **IV. PERFORMANCE ANALYSIS**

Performance analysis of the multiplier topologies presented in this paper is realized using the Tanner EDA tool, in 22nm CMOS process technology [1]. The schematics views of the topologies are obtained at power supply of 400mV, to analyze the power consumption and propagation delay. The results obtained are compared with different architectures to approximate the effectiveness of the proposed architectures [4] [6] [12]. The results are given in TABLE I-III. TABLE I gives the transistor count related with the topologies. The modified designs used for the AND

(An ISO 3297: 2007 Certified Organization)

Website: www.ijareeie.com

Vol. 6, Issue 4, April 2017

gate ,the half adder and the full adder units provides the overall reduction in area of the multiplier architectures as these topologies utilize less number of transistors as opposed to the conventional designs.. TABLE II lists the propagation delays and power consumptions associated with the proposed designs, both for the schematic.

TABLE I. Transistor Count and Layout Area

| Name of the topology                    | Transistor count |

|-----------------------------------------|------------------|

| 4-bit Multiplier of proposed Multiplier | 320              |

| 8-bit Multiplier of proposed Multiplier | 1616             |

A comparative analysis of propagation delays and power dissipation of different existing 8-bit multiplier architectures reported in the literature with the proposed architecture is presented in TABLE III. The comparison indicates that with respect to the different existing multiplier algorithms and architectures, the proposed design offers improved speed at considerably smaller power consumption with 0.4 volt power supply.

TABLE II. Propagation Delay and Power Consumption of different multiplier topologies

| Name of the topology                       | Propagation Delay (in ns) | Power Consumption (in µW) |

|--------------------------------------------|---------------------------|---------------------------|

| 4-bit Multiplier of proposed<br>Multiplier | 0.019                     | 0.134                     |

| 8-bit Multiplier of proposed<br>Multiplier | 0.408                     | 0.776                     |

### TABLE III. Performance Comparison

| Name of the topology      | Power Supply<br>in V | Propagation Delay<br>(in ns) | Power Consumption<br>(in µW) |

|---------------------------|----------------------|------------------------------|------------------------------|

| Proposed 8-bit Multiplier | 0.4                  | 0.408                        | 0.776                        |

| [4]                       | 1                    | 0.635                        | 7.460                        |

| [6]                       |                      | 21.5                         |                              |

| [7]                       |                      | 22.216                       |                              |

| [12]                      |                      | 18.532                       |                              |

| [13]                      | 2.5 to 5             | 14.13sec                     | 9.386e-2                     |

### VI.CONCLUSION

The proposed paper presents new topologies for 4-bit and 8-bit multipliers based on UT sutra of Vedic mathematics. The topologies are realized in 22 nm CMOS process technology in Tanner EDA tool and the performance analysis is performed using with a power supply of 400mV. The multiplier designs proposed in this paper provides improvement in propagation speed and power consumption and the improvement in performance is achieved due to the new UT based architecture with fewer number of adder units with the use of modified circuits.

operations using Vedic Mathematics", IEEE

## International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering

(An ISO 3297: 2007 Certified Organization)

Website: www.ijareeie.com

Vol. 6, Issue 4, April 2017

#### REFERENCES

[1] Tanner EDA Tutorial

[2] J. M. Rabaey, A. Chandrakasan and B. Nikolic, "Digital integrated circuits-A design perspective", second edition, PHI Learning Pvt. Ltd.

[3] Swami Bharati Krisna Tirthaji Maharaja, "Vedic mathematics", original edition, Motilal Banarasidass publishers.

[4] Suryasnata Tripathy, L B Omprakash, Sushanta K. Mandal, B S Patro, "Low Power Multiplier Architectures Using Vedic mathematics in 45nm Technology for High Speed Computing" International Conference on Communication, Information & Computing Technology, 2015 IEEE.

[5] G. Ganesh Kumar, V. Charishma, "Design of High Speed Vedic Multiplier using Vedic Mathematics Techniques" International Journal of Scientific and Research Publication, Volume 2, Issue 3 March 2012

[6] Garima Rawat, Khyati Rathore, Siddharth Goyal, Shefali Kala and Poornima Mittal, "Design & Analysis of ALU: Vedic Mathematics Approach", IEEE International Conference on Computing, Communication and Automation, 2015.

[7] K. Mounika, A. Damodar Reddy, "A Comparative Analysis of Multiplier Topologies using Different Vedic Sutras", International Journal of Engineering Research & Technology, Vol. 1 Issue 6 August- 2012.

[8] Emjala Divya, Y. David Solomonraju, "An Efficient Design of Vedic Multiplier using Pass Transistor Logic", International Journal & Magazine of Engineering, Technology, Management and Research, A Peer Reviewed Open Access International Journal, Vol. 3, Issue 6, 2016.

[9] Suraj A. Dafe, Suraj A. Bhagat, "Design of High Speed Vedic Multiplier using Vedic Mathematics Techniques, "International Journal of Emerging Research in Management & Technology, Vol. 4 Issue 3 March 2015.

[10] P. Sreenivasa Rao, Mr.C. Md. Aslam, "Design of Complex Multiplier with High Speed ASIC Using Vedic Mathematics", International Journal of Engineering Research & Technology, Vol. 1, Issue 6, August 2012.

[11] B. Keerthi Priya, Manoj Kumar, "A Novel Low Power Vedic Multiplier using Modified GDI Technique in 45nm Technology", International Journal of Innovative Research in Computer and Communication Engineering, Vol. 3, Issue 11, November 2015.

[12] Surabhi Bhardwaj, Ashwin Singh Dodan, "Design of High Speed Vedic Multiplier using Vedic Mathematics", International Journal of Engineering Research and General Science, Vol. 2 Issue 4 June-July 2014.

[13] Arun K. Patro, Kunal N. Dekate, "A Transistor Level Analysis for a 8-bit Vedic Multiplier", International Journal of Electronics Signals and Systems, Vol. 1 Issue 3, 2012.

[14] Akhalesh K. Itawadiya, Rajesh Mahle, Vivek Patel, Dadan Kumar, "Design a DSP International Conference on Communication and Signal Processing, April 2013.

[15] Mr. S.V. Mogre, Mr. D. G. Bhalke, "Implementation of High Speed Matrix Multiplier using Vedic Mathematics on FPGA", IEEE International conference on Computing Communication Control and Automation, 2015.