(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 10, October 2016

# **Design and Analysis of Improved Recycling** Folded Cascode OTA with Gain and Phase **Margin Enhancement**

David Solomon George<sup>1</sup>, Firoz Mon Y<sup>2</sup>

Associate Professor, Dept. of ECE, Government Engineering College, Idukki, Kerala, India<sup>1</sup>

PG Student [VLSI & Embedded System], Dept. of ECE, Government Engineering College, Idukki, Kerala, India<sup>2</sup>

ABSTRACT: In this paper, Gain boosted improved Recycling folded cascode Operational Transconductance Amplifier with phase margin enhancement architecture is described. The proposed Operational Transconductance Amplifier (OTA) is designed using cadence tool in 180 nm technology. This amplifier delivers an appreciably enhanced performance over that of conventional folded cascode. This is achieved by using previously idle in the signal path. This circuit achieves higher gain, unity gain bandwidth and Phase margin. The gain of the amplifier is enhanced by increasing the output impedance of the circuit with the addition of a cascoded gain stage which will further enhance the different parameters within the same area and power budget. A complete analysis of the circuit is presented in this thesis which shows how this circuit leads to a high gain and resistance at output. A brief comparison of different OTA architectures is described and the completed layout of the proposed OTA is also included.

KEYWORDS: OTA, Amplifiers, Gain, Phase Margin, Unity Gain Bandwidth, OTA architectures.

#### **I. INTRODUCTION**

In todays industry the low power and low voltage supply is becoming one of the important research area due to the developing market of battery operated mobile and portable electronic devices. The power consumption is becoming an important parameter as speed, gain and GBW. Operational Transconductance Amplifier (OTA) is an integral part of many analog and mixed signal systems. OTA is an amplifier whose differential input voltage produces an output current. The topology of OTAs plays an important role in the design of low power system. The design of OTA continues to face challenge as the supply voltage and transistor length scale down with each newer generation of CMOS technologies. To address the issue of power efficiency, proposed Recycling Folded Cascode (RFC) amplifier which recycles the tail current back to the input differential pair and boost the input transconductance to achieve large increase in unity gain frequency and moderate improvements in DC gain, phase margin and input referred noise. Taking into account this wide scale applicability of RFCs this particular topic is chosen as the area of research. The OTA is the most adaptable building block of analog processing system. Designing these building blocks in terms of power consumption, gain and gain bandwidth product effectively is still a challenging task. Operational Transconductance Amplifiers are mainly grouped into Single ended output OTAs and Differential ended output or Fully Differential OTAs.

#### **II. OTA ARCHITECTURES**

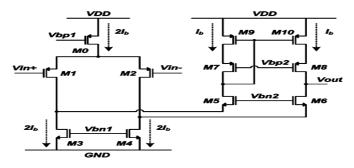

#### A. FOLDED CASCODE OTA (FC OTA)

Folded cascode OTA is mostly used architecture for its high gain and large signal swing. OTA is an amplifier, whose differential input voltage produces an output current[1],[2]. So, it is a Voltage Controlled Current Source (VCCS). (1)

I out = (V in  $_{+}$  – V in  $_{-}$ )  $\square$  g<sub>m</sub>

where  $V_{in+}$  is the voltage at the non-inverting input,  $V_{in-}$  is the voltage at inverting input, g m is the transconductance of the amplifier. The output current is a function of input differential voltage and transconductance of the circuit. The gain is described by the product of effective transconductance and output impedance of the circuit[3],[4],[5].

$$A o = g_{m,eff} \square R_{out}$$

(2)

Copyright to IJAREEIE

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 10, October 2016

where Ao is the gain,  $R_{out}$  is the output impedance. Although the Folded Cascode (FC) OTA is providing a good improvisation in term of performance parameters like gain, GBW, output voltage swing, slew rate, power consumption as compare to a Two stage OTA and Telescopic Cascode OTA. The recycling technique has become prominent to improve the performance of conventional Folded Cascode OTA with the same area and power budget[6],[7].

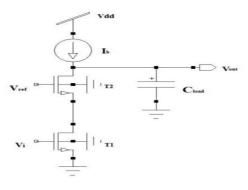

Fig 1: Folded Cascode OTA

#### B. RECYCLING FOLDED CASCODE OTA (RFC OTA)

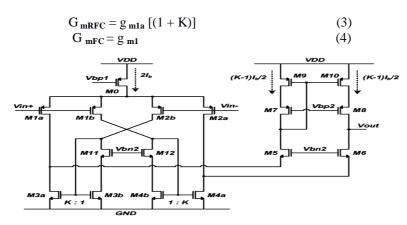

In the conventional FC transistors  $M_3$  and  $M_4$  conduct the most current, and in many designs have the largest transconductance. However, their role is limited to providing a folding node for the small signal current generated by the input drivers  $M_1$  and  $M_2$ . To address this inefficiency, a modified FC is presented. The proposed modifications are intended to use  $M_3$  and  $M_4$  as driving transistors[8]. First, the input drivers  $M_1$  and  $M_2$  are split in half to produce transistors  $M_{1a}$ ,  $M_{1b}$ ,  $M_{2a}$  and  $M_{2b}$ , which now conduct fixed and equal currents  $I_b$ /2. Next,  $M_3$  and  $M_4$  are split to form the current mirrors  $M_{3a}$ :  $M_{3b}$  and  $M_{4a}$ :  $M_{4b}$  with a ratio of K:1. The cross-over connections of these current mirrors ensure the small signal currents added at the source of  $M_5$  and  $M_6$  are in phase. Finally  $M_{11}$  and  $M_{12}$  are sized similar to  $M_5$  and  $M_6$ , and their addition helps maintain the drain potentials of  $M_{3a}$ :  $M_{3b}$  and  $M_{4a}$ :  $M_{4b}$  equal for improved matching. The amplifiers transconductance, Gm , by Finding the short circuit current at the output with respect to the input. The results for RFC and FC.

Fig 2: Recycling Folded Cascode OTA

By taking into account that  $M_1$  is twice the size of  $M_{1a}$  and conducts twice the amount of current[9] (ie,  $g_{m\,1} = 2g_{m1a}$ ), and substituting for the value of K, the transconductance of the RFC is demonstrated to be twice that of the FC for the same power consumption. It shows that the RFC has twice the gain bandwidth (GBW) as that of the FC for the same power, and consequently twice the speed. The low frequency gain of OTAs is frequently expressed as the product of the small signal transconductance Gm , and low frequency output impedance,  $R_0$ . It was demonstrated that G  $_{mRFC} = 2G_{mFC}$ , which results about an 6 dB gain enhancement for the same output impedance. However, is also enhanced over . The expressions for R  $_{0RFC}$  and R  $_{0FC}$  are

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 10, October 2016

| $R_{oRFC} = g_{m6}r_{ds6}(r_{ds2a}   r_{ds4a})  g_{m8}r_{ds8}r_{ds10}$     | (5) |

|----------------------------------------------------------------------------|-----|

| $R_{oFC} = g_{m6} r_{ds6} (r_{ds2}    r_{ds4})    g_{m8} r_{ds8} r_{ds10}$ | (6) |

(6)

The gain enhancement seen in R<sub>oRF C</sub> is attributed to the increased r ds of M  $_{2a}$  and M  $_{4a}$ , as they conduct less current compared to their counterparts M  $_2$  and M  $_4$  of the FC. Therefore, an overall low frequency gain enhancement of 8 to 10 dB can be seen in the RFC compared to the FC. This added gain has two fundamental benefits. First one, static settling errors are reduced because of the increased gain. Second one, the power supply rejection ratio (PSRR) of the RFC is improved over its FC counterpart.

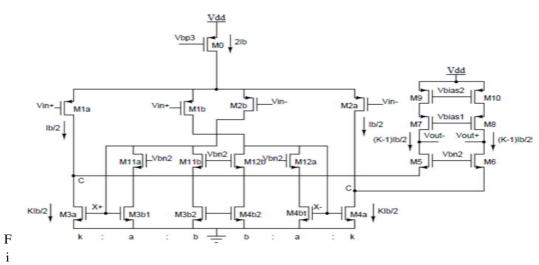

#### C. IMPROVED RECYCLING FOLDED CASCODE OTA (IRFC OTA)

To improve the swing of the signal at the current mirror nodes X + and X - d, the DC and AC path are separated in IRFC proposed is shown in Fig 3. To achieve this, the transistors M<sub>11</sub>, M<sub>3b</sub>, M<sub>12</sub> and M<sub>4b</sub> are divided into two parts M 11a, M11b, M 3b1, M 3b2 and M 12a, M 12b, M 4b1, M 4b2 respectively. The paths M 11b, M 3b2 and M 12b, M 4b2 have high impedance. The paths M 11a, M 3b1 and M 12a, M 4b1 and have low impedance. The small signal current flows through the low impedance path. The ratio of DC current flowing through the high impedance and low impedance paths is a:b and the transconductance of M  $_{11a}$ , M  $_{3b1}$  is scaled by a where a < 1. The signal flowing through the current mirror node becomes larger compared to that of the RFC because of the increase in the resistance of the small signal path.

The recycling and improved recycling techniques is used to boost the transconductance of OTAs by multiple times and achieve very high GBW values in power efficient way. However, DC gain is not enhanced by similar amount on dB scale.

The output impedance R out of the IRFC OTA is given by

$$R_{outIRFC} = g_{m5} r_{05} (r_{01a} || r_{03a}) || g_{m7} r_{07} r_{09}$$

(7)

The Gain A<sub>v</sub> of the IRFC OTA is given by

$A_{v} = g_{m1a}(k/a + 1) \Box g_{m5} r_{05} (r_{01a} || r_{03a}) || g_{m7} r_{07} r_{09}$ (8)

g 3: Improved Recycling Folded Cascode OTA.

### III. GAIN BOOSTED IRFC OTA WITH PHASE MARGIN ENHANCEMENT

The ineffectiveness of folded cascode OTA was overcome by recycling folded cascode OTA in which we are reusing or recycling the devices or currents to perform additional task speed but the voltage swing is reduced at the output. And also the multistage amplifiers may be used for high gains but such kind of high gain amplifiers are generally difficult to compensate. So we have to implement some compensation techniques to achieve the stability and significant phase margin. So here a Single Miller Compensation Nulling Resistor (SMCNR) is used in which we put a compensation capacitor between input and output nodes of the second inverting stage of the amplifier and the dominant pole is created due to Miller feedback and it will helps us to increase the phase margin and to achieve stability. In the proposed GB RFC OTA the gain is enhanced by improving the output impedance because the output resistance increases in proportion to the decrease in bias current. So it make the circuit power efficient to increase the output

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 10, October 2016

impedance by lowering the currents. The cascode gain boosting stage is attached to enhance the performance parameters. The output impedance  $R_{out}$  of the IRFC OTA is given by

$R_{outIRFC} = g_{m5} r_{05} (r_{01a} || r_{03a}) || g_{m7} r_{07} r_{09}$ (9)

The output impedance of GB-IRFC is given by

Fig 4: GB-IRFC OTA with phase margin enhancement

#### A. GAIN BOOSTING

In the IRFC operational transconductance amplifier the gain is enhanced by increasing the output impedance of the circuit by providing a cascoded gain stage. The higher gain often causes to instability so to achieve the stability and better phase margin the miller compensation is used. In order to increase the gain either the Transconductance or the output impedance can be enhanced. But the transconductance increases as square root of increase in bias current which cause to increase in power consumption[12],[13].

#### Fig 5: Gain boosting stage

The cascoded structures as shown above are widely used to boost the gain. The output voltage V <sub>out</sub> is given by  $\Delta V_{out} = \Delta I_o R_{out}$  (11)

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 10, October 2016

Where R out is the output impedance of the whole circuit and is given by

| $R_{out} = (g_{m2}r_{02} + 1)r_{01} + r_{02}$ | (12) |

|-----------------------------------------------|------|

| $R_{out} = g_{m2} r_{02} r_{01}$              | (13) |

| $R_{out} = g_{m2} r_{02} r_{01}$ |  |

|----------------------------------|--|

|----------------------------------|--|

It produces the following expression of DC gain A  $_{\rm o}$

#### $A_0 = g_{m1} r_{01} (g_{m2} r_{02} + 1)$ (14)

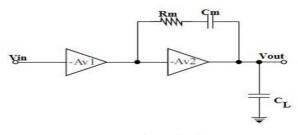

#### **B. MILLER COMPENSATION**

However the multistage amplifiers may be used for high gains but such kind of high gain amplifiers are generally difficult to compensate. So we have to implement some compensation techniques to achieve the stability and significant phase margin. So here Single Miller Compensation Nulling Resistor (SMCNR) is used in which we place a compensating capacitor in between the input and output nodes of the second inverting stage of the amplifier and the dominant pole is created due to Miller feedback and it will helps us to increase the high midband gap without affecting its dc response[14].

Sometimes if the transistor gain of second stage increases the dominant poles decreases and non dominant pole increases and poles are split aside to stabilize the amplifier but this method also introduces a Right Half Plane (RHP) zero which causes a negative phase shift and stability decreases. This zero arises because of the direct feed through of input to output through Miller capacitor. So in order to increase the phase margin the RHP should be eliminated, a lead compensation technique in which the nulling resistor in series with the compensation capacitor is used to increase the impedance of feed through path.

Fig 6: SMCNR **IV. RESULT AND DISCUSSION**

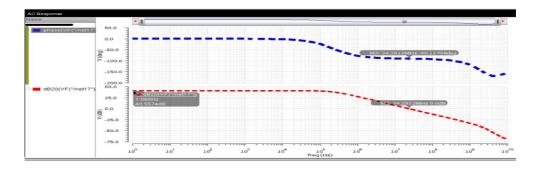

#### A. FOLDED CASCODE OTA

While analyzing gain and phase margin the following results are found.

From analysing the output waveform of the folded cascode circuit shown in Fig 7, it got a gain of 40.5 dB and a phase margin of 89.785 degree.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 10, October 2016

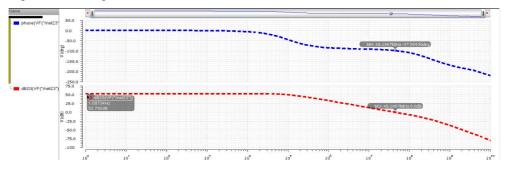

#### **B. RECYCLING FOLDED CASCODE OTA**

From analysing the output waveform of the Recycling folded cascode circuit shown in Fig.8, it got a gain of 52.79 dB and a phase margin of 82.04 degree.

Fig 8: Output waveform of Recycling Folded Cascode OTA

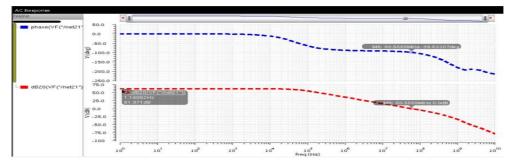

#### C. IMPROVED RECYCLING FOLDED CASCODE OTA

From analysing the output waveform of the Improved Recycling folded cascode circuit shown in Fig.9, it got a gain of 61.97 dB and a phase margin of 81.37 degree.

Fig 9: Output waveform of IRFC OTA

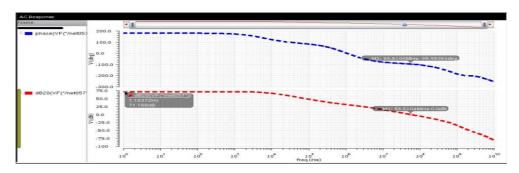

#### D. GB-IRFC OTA

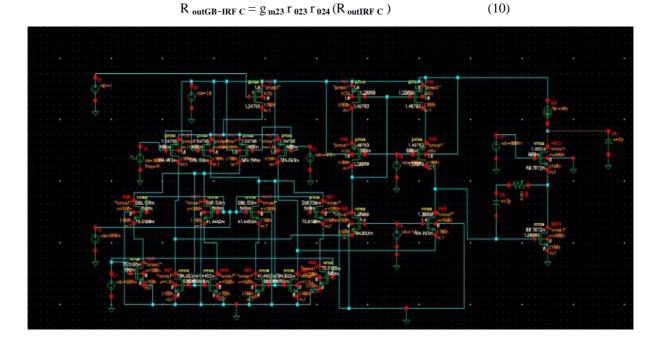

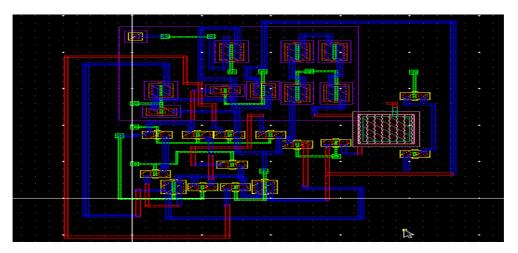

From analysing the output waveform of the Gain boosted Improved Recycling folded cascode with phase margin enhancement circuit shown in Fig.10, it got a gain of 71.168 dB and a phase margin of 84.05 degree. The layout of the circuit is shown in Fig.11. The GB-IRFC OTA showing significant performance over the existing configurations like FC, RFC, IRFC. The performance comparison is shown in the Table I.

Fig 10: Output waveform of GB-IRFC OTA with phase margin enhancement

(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 10, October 2016

Fig 11. Layout of GB-IRFC OTA with phase margin enhancement

| Parameter           | FC     | RFC    | IRFC   | GB-IRFC |

|---------------------|--------|--------|--------|---------|

| Gain(dB)            | 40.55  | 52.79  | 61.971 | 71.168  |

| Phase Margin(deg)   | 89.785 | 82.04  | 81.37  | 84.05   |

| GBW (MHz)           | 24.251 | 45.186 | 60.56  | 56.51   |

| Supply Voltage(V)   | 1.8    | 1.8    | 1.8    | 1.8     |

| capacitive load(pF) | 2      | 2      | 2      | 2       |

Table I. Performance Comparison

#### V. CONCLUSION

It has been demonstrated that the gain-boosted recycling folded cascode amplifier with phase margin enhancement achieves superior performance when compared to three other topologies namely Folded Cascode (FC), Recycling Folded Cascode (RFC) and Improved Recycling Folded Cascode (IRFC) OTAs. For a better comparison, the four amplifiers have been realised in gpdk 180 nm CMOS technology process using the same power and area budget. The output impedance of the circuit is enhanced by adding a cascode gain stage at the output. A significant increase in Gain and GBW is achieved within the same area and power budget. The Miller compensation technique is used to increase the phase margin of the circuit.

#### REFERENCES

[1] P.R Gray ,R.G Mayer.," MOS Operational Amplifier Design-A Tutorial Overview", IEEE Journal of solid state Circuits, VOL.SC - 17, NO.6; pp. 969 - 982, December 1982.

[2] Behzad Razavi, "CMOS Technology Characterisation for Analog and RF Design," IEEE Conference on Custom Integrated Circuits, September 1998

[3] B. Hernes, W. Sansen "Distortion in single, two and three-stage amplifiers", IEEE Transactions on Circuits and Systems., Volume: 52, Issue: 5, May 2005.

[4] B.P. Brandt, D.E. Wingard, and B.A. Wooley., "Second-Order Sigma-Delta Modulation for Digital Audio Signal Acquisition", IEEE Journal of Solid State Circuits, Vol. 26, No. 4, pp. 618-627, April 1991.

[5] Xiao Zhao ; Huajun Fang; Jun Xu., "Phase-margin enhancement technique for recycling folded cascode amplifier," Analog Integrated Circuits and Signal Processing, v.74 n.2, p.479-483, February 2013.

[6] Philip E. Allen & Douglas R., Holberg., CMOS Analog Circuit Design, 2nd Edition., Oxford University Press, 2009.

[9] Xiao Zhao; Huajun Fang; Jun Xu., "DC gain enhancement method for recycling folded cascode amplifier in deep submicron CMOS technology", IEICE Electronics Express, vol.8, no.17, pp.1450,1454, Sept. 10.

<sup>[7]</sup> Assaad, R.; Silva-Martinez, J., "Enhancing general performance of folded cascode amplifier by recycling current", Electronics Letters, vol.43, no.23, Nov. 8 2007.

<sup>[8]</sup> Rida S. Assaad, Jose Silva-Martinez "The Recycling Folded Cascode: A General Enhancement of the Folded Cascode Amplifier" IEEE Journal of Solid State Circuits, VOL. 44, NO. 9, Sept. 2009.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 10, October 2016

[10] Yan, Z., Mak, P.-I., Martins, R.P., "Double Recycling Technique for Folded-cascode OTA", Analog Integrated Circuits and Signal Processing, vol. 71, pp. 137-141, 2012.

[11] S.Kumaravel, B.Venkataramani., "An Improved Recycling Folded Cascode OTA with Positive Feedback" WSEAS Transactions on Circuits and Systems Vol.13, Oct-2014.

[12] Sanjeev Sharma, Pawandeep Kaur, Tapsi Singh, Mukesh Kumar.,"A Review of Different Architectures of Operational Transconductance Amplifier" IJECT Vol. 3, Issue 4, Oct - Dec 2012.

[13] Li, Y.L.; Han, K.F.; Tan, X.; Yan, N.; Min, H., "Transconductance enhancement method for operational transconductance amplifiers", Electronics Letters, vol.46, no.19, pp.1321,1323, Sept. 16 2010.

[14] Swati Kundra, Priyanka Soni and Anshul Kundra "Low Power Folded Cascode OTA", International Journal of VLSI design Communication Systems Vol.3, No.1, February 2012.