(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 12, December 2013

# DATA Surveillance Using I2C Protocol & VHDL

Jayant Mankar<sup>1</sup>, Chaitali Darode<sup>2</sup>, Komal Trivedi<sup>3</sup>, Madhura Kanoje<sup>4</sup>, Prachi Shahare<sup>5</sup>

Asst. Professor, Dept. Of Electronics Engg., Smt. Rajshree Mulak College of Engg. For Women, Nagpur, India<sup>1</sup>

Student, Dept. Of Electronics & Telecomm. Engg., Smt. Rajshree Mulak College of Engg. For Women, Nagpur, India<sup>2-5</sup>

**ABSTRACT**: I2C protocol provides easy communication without data loss. It also gives excellent speed compared to other protocols.I2C uses only two wire for communication. It is light weight, economical and omnipresent. It also increases data transfer rate. The objective to develop the protocol is to get high speed communication and to control registers inside the devices as well as the data that can be saved on registers, through this we are able to control various parameters. I2C is used in data surveillance for accuracy and efficiency. The design method is developed in VHDL, simulated on MODELSIM or Xilinx and can be implemented on FPGA board

Keywords: I2C protocol, Data surveillance, VHDL, ModelSim, SDA, SCL,

#### I. INTRODUCTION

The physical size and power requirement of IC get reduce over the years. The main reason for that is more number of transistors can be integrated into smaller size and less number of interconnections wire present in between ICs can possible. The actual circuitry of the IC is much smaller than the packaging of the IC but it requires larger area to cover because of interconnection wire present in between ICs.

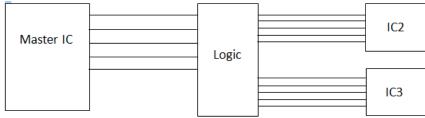

Fig 1.Basic block diagram of I<sup>2</sup>C system

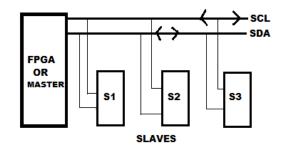

These wire requirement can be reduce by using  $I^2C$ , that is Inter-Integrated circuit bus. This communication have a special protocol assigned to it which is  $I^2C$  Protocol.  $I^2C$  bus physically consist of two active wires and a ground connection. The two active wires namely Serial Clock[SCL] and Serial Data[SDA]. These wire are bidirectional half duplex in nature which carry information between the devices connected to the bus. Each device is acknowledge by a unique address whether it is a microcontroller, LCD driver, memory or keyboard interface and can operate as either a transmitter or receiver, depending on the function of t he device. In  $I^2C$  bus devices can easily added or removed which is very useful for low maintenance and control application in embedded system

(An ISO 3297: 2007 Certified Organization)

#### Vol. 2, Issue 12, December 2013

Fig 2.Master and Slave in I2C system

#### II. LITERATURE SURVEY

There are many reasons for using serial interface design many more important application includes serial communication like sensors communication with personal computer. Many common Embedded system peripherals, such as anolog-to-digital and digital-to-anlaog convetors, LCDs, and temperature sensors, support serial interfaces. Serial interface allow processors to communicate without the need for shared memory and the problems they can create. There are Serial communication protocols like UART,CAN,USB,SPI, Inter IC. USB,SPI and UARTS are all

| •••                                                                                                                         | foute: There are bottal communication protocols into criticity of it (cobb), of it, into the obb), of it and criticity are an |           |     |              |     |                  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------|-----|--------------|-----|------------------|--|--|--|

| just one type to point type protocol. USB uses multiplexer to communicate with other devices. Only I <sup>2</sup> C and CAN |                                                                                                                               |           |     |              |     |                  |  |  |  |

| р                                                                                                                           | protocol uses software addressing. But only I <sup>2</sup> C is very simple to design and easy to maintain.                   |           |     |              |     |                  |  |  |  |

|                                                                                                                             |                                                                                                                               |           |     |              |     |                  |  |  |  |

|                                                                                                                             |                                                                                                                               | UART      | CAN | USB          | SPI | I <sup>2</sup> C |  |  |  |

|                                                                                                                             | DD OLIG                                                                                                                       | TT 7 11 1 | a 0 | <b>a b b</b> |     |                  |  |  |  |

|       | UAKI           | CAN         | USB              | 5P1                          | 10                     |

|-------|----------------|-------------|------------------|------------------------------|------------------------|

| PRONS | Well known     | Secure fast | Secure,fast,plug | Fast, low, cost, universally | Simple, plug and       |

|       | Simple         |             | and play         | accepted, large portfolio    | play,cost              |

|       |                |             |                  |                              | effective, universally |

|       |                |             |                  |                              | acceptd                |

| CONS  | Limited        | Complex,    | Powerful master  | No plug and play hardware,   | Limited no. Of         |

|       | functionality, | liumited    | required,        | No fixed standard            | components due to      |

|       | Point to point | portfolio,  | No plug and play |                              | capacitance effect     |

|       |                | Automotive  | software,        |                              |                        |

|       |                | oriented    | Extra drivers    |                              |                        |

|       |                |             | required         |                              |                        |

|       |                |             |                  |                              |                        |

| 1     |                |             |                  |                              |                        |

Table I: Comparisons Of different Protocols

#### III. PROPOSED SYSTEM

#### A.Components Of $I^2C$ :

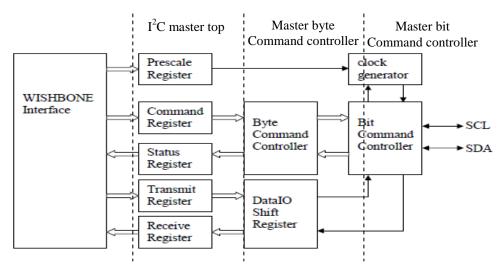

$-1^{2}$ C master top comprises of prescale register, command register, status register, transmit register, and receive register. Prescale register is used to reduce high frequency electrical signal to lower frequency by integer division. Data comes initially into status register and depending upon it the command register issues the commands. Transmit and receive register decide whether to transmit or receive the data and this data is transmitted parallel to data I/O register

(An ISO 3297: 2007 Certified Organization)

## Vol. 2, Issue 12, December 2013

Fig 3: Components in I<sup>2</sup>C communication

-I<sup>2</sup>C Master Byte Controller are the byte command controller and data I/O shift register. The byte command controller is the heart of I<sup>2</sup>C communication traffic at the byte level and is a state machine that generates different states of I<sup>2</sup>C byte operations based on the command register bits. The data I/O shift register is a component which contains and deals with the data associated with the present I<sup>2</sup>C write and read transactions.

- I<sup>2</sup>C Master bit controller involves clock generator and a bit command controller. During transmission data is shifted bit by bit into the command bit controller and from there it is transferred onto SDA. During reception data comes on SDA and then to bit controller

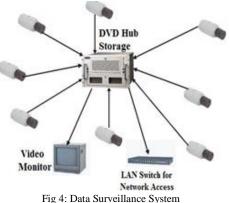

#### B.Data surveillance:

Data surveillance compiles personal information from various sources to investigate .Data sueveillance also helps in monitoring people's daily activities and interactions amongst each other. It has proven to be far cheaper and more effective than traditional forms of surveillance with I2C and is quickly increasing in popularity throughout a number of different fields.

However, the next generation of data surveillance systems will replace these components with newer digital LAN cameras, complex image processing, and data-over-IP routing. They will no longer be simply camera systems, but also data communication system.<sup>[1]</sup>

There are many different standards for video data compression, with the most popular including JPEG, H.263, Motion JPEG, MPEG, and Wavelet. The type of compression used has an impact on hardware system requirements, including

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

memory, data rate, and storage space. However, next-generation surveillance systems will probably use the H.264 standard due to its compression efficiency. Efficiency is a key factor in the transmission of high-quality video over a bandwidth-limited network. For example, a colour transmission at 30 fps at 640 x 480 pixels requires a data rate of 26 Mbytes/sec. This data rate must be reduced (compressed) to a more manageable data rate that can be routed over a twisted pair of copper wires.

#### IV. WORKING

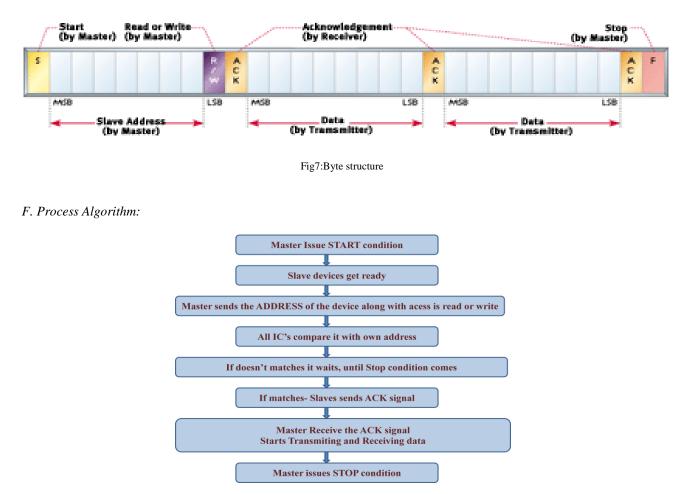

Different stages of I<sup>2</sup>C communication are as explained below-

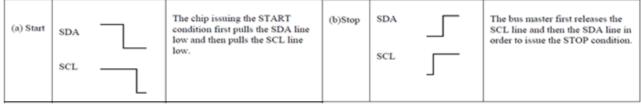

A. Start and Stop Conditions

Before any transaction a START condition needs to be issued on the bus. The start condition acts as a signal to all connected IC's that something is about to be transmitted. After a message has been completed, a STOP condition is sent. This is the signal for all devices on the bus that the bus is available again (idle). If a chip was accessed and has received data during the last transaction, it will now process this information (if not already processed during the reception of the message).

Table II: Start and Stop conditions

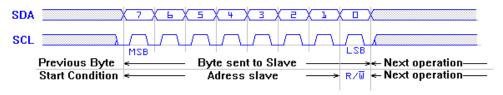

#### B. Transmitting a byte to a slave device

After start condition has been sent, a byte can be transmitted to a slave by the master. This first byte after a start condition will identify the slave on the bus (address) and will select the mode of operation. The meaning of all following bytes depends on the slave.

Fig 5: Transmission of a byte to a slave

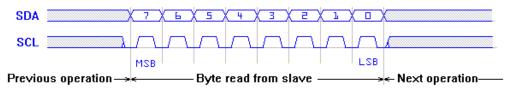

#### C. Receiving a byte from a slave device

Once the slave has been addressed and the slave has acknowledged this, a byte can be received from the slave if the R/W bit in the address was set to READ (set to '1').

Fig 6: Reception of a byte from a slave

#### D.Getting acknowledge (ACK) from a slave device

When an address or data byte has been transmitted onto the bus then this must be acknowledged by the slave(s). In case of an address, if the address matches its own then that slave and only that slave will respond to the address with an ACK. In case of a byte transmitted to an already addressed slave, the slave will respond with an ACK as well. Copyright to IJAREEIE www.ijareeie.com

(An ISO 3297: 2007 Certified Organization)

## Vol. 2, Issue 12, December 2013

#### E. Giving acknowledge (ACK) from a slave device

Upon reception of a byte from a slave, the master must acknowledge this to the slave device. If there is no data left to receive, the master will send a not-acknowledge (NACK) signal and will stop the data transaction.<sup>[1]</sup>

The overall coding part can be written on VHDL and simulate on Xilinx. It can be represented with the help of RTL diagram of I2C and verified. I2C interfacing technique is implemented using different techniques and Result can be verified with Xilinx ISE Design suite  $13.1_1$ .<sup>[1]</sup>

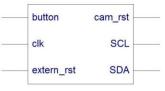

Fig 8: RTL diagram of Data Surveillanc

(An ISO 3297: 2007 Certified Organization)

#### Vol. 2, Issue 12, December 2013

| S.No | Pin Name   | Pin Description                                       |

|------|------------|-------------------------------------------------------|

| 1.   | Button     | It used for reset<br>The FPGA                         |

| 2.   | Clk        | It is the clock given for entire system               |

| 3.   | Extern_rst | It is the external reset to restart the system        |

| 4.   | CAM_RST    | It is the camera reset signal to reset the camera     |

| 5.   | SCL        | It is the Serial Clock line to provide the clock      |

| 6.   | SDA        | Serial Data line, It send the address of the register |

Table III: I/O Pin description

## **V.** FEATURES OF $I^2C$

- It is multimaster serial ended computer bus

- I<sup>2</sup>C has two wire bi-directional serial bus

- It is a simple and efficient method of data exchange

- I<sup>2</sup>C protocol have low bandwith

- It is a Short distance protocol

#### **VI.** ADVANTAGES OF $I^2C$

- I. Used for security sensitive applications like sensor connections, RFID, biometric devices, etc

- II. Common communication standards between microcontrollers and sensors

- III. Each device is recognised by its unique address and can operates as either a transmitter or receiver, depending upon the function of the device

- IV. It Provides enhance security system

- V. Compatible with FPGA

#### VI. CONCLUSION

The ideal surveillance architecture with I2C will have the following characteristics: high performance, flexibility, easy upgradability, low development cost, and a migration path to lower cost as the application matures and volume ramps. FPGAs in conjunction with the feature-rich Data and Image Processing Suite, Data over IP reference design, and partner's compression solutions offer data system designers all the key building blocks needed to produce such a system.

#### REFERENCES

- [1] Arvind Sahu, Ravi Shankar Mishra, Puran Gour, "Design and Interfacing of High speed model of FPGAS using I2C protocol", Int.J.Com.Tech.Appl.Vol2(3), 531-536

- [2] Shoaib.Shah Sobhan, Sudipta. Das and Iqbalur. Rahman, "Implementation of I2C using System Verilog and FPGA", ICAEPE'2011

- [3] P.Venkateswaran, A. Saynal, S. Das, S.K Saynal and R. Nandi, "FPGA Based Efficient Interface Model for Scale-Free Computer Networking using I2C Protocol" 15th.intl" conf on computing – CIC 2006, Proc. Research in Computing Science: Special Issues – Advances in Computer Science & Eng., ISSN 1870 – 406, pub. National Polytechnic Institute, Mexico, Vol.23, pp 191 - 198, Nov. 21-24,2006

- [4] Xavier Righetti Xavier Righetti "Proposition of a Modular I2C-Based Wearable Architecture" IEEE-2010

- [5] Jan O. Borchers, Wolfgang Samminger, Max M"uhlh"auser "Personal Orchestra: Conducting Audio/Video Music Recordings" IEEE-2002.

- [6] A.R.M. Khan, A.P.Thakare, S.M.Gulhane "FPGA-Based Design of Controller for Sound Fetching from Codec Using Altera DE2 Board" International Journal of Scientific & Engineering Research,

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

[7] A.K. Oudjida, M.L. Berrandjia, R. Tiar, A. Liacha, K. Tahraoui "FPGA Implementation of I2C & SPI Protocols" a Comparative Study" IEEE 2009

[8] J.M. Irazabel & S. Blozis, Philips Semiconductors, "I2CManual, Application Note, ref. AN10216-0" March 24, 2003.

- [9] F. Leens, "An Introduction to I2C and SPI Protocols," IEEE Instrumentation & Measurement Magazine, pp. 8-13, February 2009.

- [10] L. Bacciarelli et al, "Design, Testing and Prototyping of a Software Programmable I2C/SPI IP on AMBA Bus," Conference on Ph.D.Research in Microelectronics and Electronics (PRIME'2006), pp. 373-376, ISBN: 1-4244-0157-7, Ortanto, Italy, June 2006.

- [11] Fred Eady "Networking and Internetworking with Microcontrollers" Elsevier, 2004.

- [12] J. Bhasker, A VHDL Synthesis Primer, BS Publications 2nd Edition, 2003, pp. 132.

- [13] Design Ware Inter-IC (I2C) VIP Data book, Version 1.10a, February 18, 2005, Synopsis.Figure 6. Flow Summary of the Device 1.

- [14] THE I2C BUS SPECIFICATION VERSION 2.1 January, 2000, Philips Semiconductors.

- [15] TMS470R1x Inter-Integrated Circuit (I2C) Reference Guide, Texas Instruments (SPNU223).

- [16] Xilinx Inc., "Virtex-II<sup>TM</sup> V2MB1000 Development Board User"sGuide". Available:

- [17] www.semiconductors.philips.com//I2C/index.hml

- [18] http://www.embedded.com/story/OEG20010718S0073