(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 12, December 2013

# Efficient Implementation of Adaptive Noise Canceller Using FPGA for Automobile Applications

### S.Thilagam

Assistant Professor, Department of ECE, Kumaraguru College of Technology, Coimbatore, Tamilnadu, India

**ABSTRACT:**This paper presents the architecture and implementation of a real time adaptive NLMS filter for nonstationary noise cancellation in a car environment. The active noise control techniques using adaptive digital filters are very much suitable and well proven. The proposed efficient Adaptive Noise Canceller is realized using Xilinx System Generator 12.3 on Spartan 3E FPGA. System Generator is a DSP design tool from Xilinx that enables the use of The Mathworks model-based design environment ,Simulink for FPGA design. All FPGA implementation steps including Synthesis, place and Route are automatically performed to generate an FPGA programming file and the design is evaluated in terms of speed, hardware resources and power dissipation.

Keywords: LMS Adaptive filter, Noise canceller, Xilinx system generator 12.3, Spartan 3E, VHDL

### I. INTRODUCTION

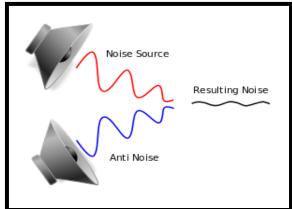

The purpose of active noise control is to generate an anti-noise signal from a speaker to minimize the noise level of the original signal. Traditional noise control techniques use passive treatments to minimize the noise level [1, 4, 5]. In automobile industry, the noise level in the car cabin is minimized by using mufflers to absorb the engine noise. However, these techniques cannot minimize noise that has a low frequency. An adaptive filter is used to generate the anti-noise signal thus minimizing noise as shown in figure 1[6, 7]. An efficient LMS adaptive filter is implemented to achieve this noise cancellation.

Figure 1.Graphical depiction of Active Noise Reduction

### II. ADAPTIVE NOISE CANCELLER

The Adaptive Noise Canceller employs a directional microphone to measure and estimate the instantaneous amplitude of ambient noise and another microphone is used to take the speech signal which is contaminated with noise[13]. The ambient noise is processed by the adaptive filter to make it equal to the noise contaminating the speech signal and then Copyright to IJAREEIE www.ijareeie.com 6218

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

is subtracted to cancel out the noise in the desired signal. In order to be effectively removed, the ambient noise must be highly correlated with the noise components in the speech signal.

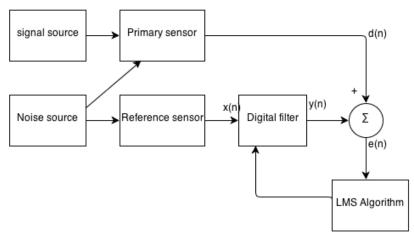

The Least Mean Square (LMS) adaptive filter is used for implementing the noise cancellation because of its simplicity and suitability for real-time applications [14][15]. The block diagram of Adaptive Noise Canceller is shown in figure 2.

Figure 2. Block Diagram of Adaptive Noise Cancellation

In figure 2, The error at the output of the filter can be expressed as,

$e_n = d_n - W_n^T u_n$

(1)

(3)

which is simply the desired output minus the actual filter output. The step size parameter, $\mu$  in the weight update equation,

$$W_{n+1} = W_n + 2\mu . e_n . u_n \tag{2}$$

determines how fast the algorithm converges to the optimal weights

$$<\mu<2/M.S_{max}$$

Where M is the number of filter taps and  $S_{max}$  is the maximum value of the power spectral density of the tap inputs  $\mu$ .[17]

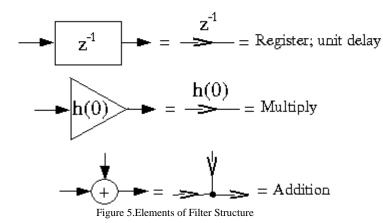

From each set of equations(1),(2) and (3), we can construct a block diagram consisting of an interconnection of delay elements, multipliers, and adders. Such block diagrams are called realizations of the system or equivalently structures for realizing the system[18].

#### **III. REALIZATION FACTORS**

The major factors that influence the choice of realization are

1. Computational Complexity

2. Memory Requirements

3.Finite Word-length Effects

4. Ease of Implementation.

Computational complexity refers to the number of arithmetic operations (multiplications, divisions, and additions) required to compute an output value y(n) for the system.

Memory requirements refer to the amount of memory required to store the system parameters, past inputs, past outputs and any intermediate computed values.

Finite word-length effects or finite precision effects refer to the quantization effects that are inherent in any digital implementation of system, either in hardware or in software [8].

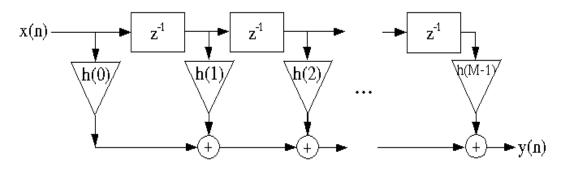

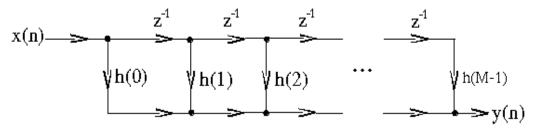

The filter could be implemented by cascading as many units of the unit cell as the length of the filter as shown in figure 3 and figure 4. The basic elements of filter structure are shown in figure 5.[10][12].

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 12, December 2013

Figure 3.FIR filter structure representation 1

Or as

Figure 4.FIR filter structure representation 2

#### IV. FPGA IMPLEMENTATION OF ANC

#### A The SPARTAN-3E FPGA

The FPGA used to implement the Adaptive Noise Canceller is 500,000-gate Xilinx Spartan-3E XC3S500E as shown in figure 6.Spartan-3E devices contain a two-dimensional row and column based architecture to implement custom logic. For implementing ANC using LMS filter, the number of operations for an N-tap filter has been reduced to 2\* N multiplications and N additions per coefficient update. Numerous techniques have been devised to efficiently calculate the convolution operation when the filter's coefficients are fixed in advance [20]

#### Copyright to IJAREEIE

(An ISO 3297: 2007 Certified Organization)

Vol. 2, Issue 12, December 2013

Figure 6. Spartan-3E kit

#### B Implementation of LMS Algorithm

The LMS algorithm uses an FIR filter structure. The design shown in figure represents a structural view of the filter. From the figure, the main components of the filter consist of L-1 Unit Delay Registers and L Weight Updates. The Unit Delay Registers are simply D flipflops. Each weight Update component consists of a multiplier, an adder and a buffer to store the new weights' update of the filter coefficient. [15]According to equation (2), the filter output is subtracted from the desired signal to produce an error signal. The error signal is then multiplied with  $\mu$  and then with the input signal, which produces next sets of filter coefficients.

#### C Fixed point representation of data

Fixed point is a step between integer mathematics and floating point. This has the advantage of being almost as fast as integer arithmetic and able to represent numbers with fraction. It uses a smaller area in FPGA than floating point to process arithmetic operations [19]. A fixed-point number has an assigned width and an assigned location for the decimal point. As long as the number is big enough to provide enough precision, fixed point is fine for most DSP applications. Because it is based on integer math, it is extremely efficient as long as the data does not vary too much in magnitude [2][3].

#### D Word length Selection

The most essential task is the right selection of word lengths for the various variables in the system. Short word lengths may result in extra round-off errors, which can cause instability or poor performance. On the other hand, the use of excessively long word lengths increases system complexity which in turn reduces its maximum speed and increases the used area of the FPGA.So balance should be achieved between the system round-off errors and the maximum speed of operation together with the used area of the FPGA[9][10][12].

The training algorithm for the adaptive filter usually use a direct form FIR structure that has a delay which is determined by the depth of the output adder, which is dependent on the filter's order. A direct form FIR filter of length 16 is used for the purpose of noise cancellation.

#### V. TESTING AND RESULTS

The efficient fixed point LMS based adaptive filter is designed using VHDL. The design is synthesized and simulated on Xilinx System Generator 12.3. The simulation results after implementation of the Adaptive Noise

(An ISO 3297: 2007 Certified Organization)

## Vol. 2, Issue 12, December 2013

Canceller on FPGA are shown in figure 7. The hardware resources required to implement this filter can be obtained from the simulation results shown in figure 7 from the device utilization summary and synthesis report.

|                                     |   | 563.4   |         |         |          |        |          |  |       |       |          |

|-------------------------------------|---|---------|---------|---------|----------|--------|----------|--|-------|-------|----------|

| Current Simulation<br>Time: 1000 ns |   | o       | 200     |         | 400<br>I |        | 600<br>I |  | 800   |       |          |

| öll cik                             | 1 |         |         |         |          |        |          |  |       |       |          |

| ön rst                              | 0 |         |         |         |          |        |          |  |       |       |          |

| 🎝 👖 train                           | 1 |         |         |         |          |        |          |  |       |       |          |

| 🗉 💸 data_in(15:0)                   | 1 | 16'b0   | (16'b0) | 16'b0   | (16'b1)  | 16'b0  | ( 16'b1  |  | 16'b1 | 16'b0 | 16'b0    |

| 🖽 刻 new_data                        | 1 | 16'b0   | 16'b1   | 16'b1   | 16'b0    | 16'b1  | (16'b1   |  | 16'b0 | 16'b1 | 6'b11010 |

| 🖽 刻 desired[15:0]                   | 1 | (16'b0) | (16'b0) | (16'b1  | (16'b0)  | (16'b0 | 16'b1    |  | 16'b1 | 16'b1 | 6'601111 |

| 🖪 🚮 data_out[15:0]                  | 1 | 16'hU   | υυυυ    | 6'h0000 |          |        |          |  |       |       |          |

|                                     |   |         |         |         |          |        |          |  |       |       |          |

Figure 7.Simulation Results of Adaptive Noise Canceller

#### VI. RESOURCE UTILISATION

Table 1. Device Utilization summary represents implementation result mentioning resource utilization of the device Xilinx SPARTAN 3E kit. The synthesized outputs are given below. The number of gates required to implement the Adaptive Noise Canceller and the utilization percentage of the total hardware in the FPGA kit is summarized in Table 1. The number of Slice flipflops,Look-up table,number of bonde IOBs,number of GCLKs are summarized in Table 1.

The results prove that the LMS adaptive filter implemented for the Adaptive Noise Cancellation satisfy the desired demand by providing stability after period of time.(time of Convergence) in a non-stationary (car)environment.Efficient implementation is justified by the resource utilization efficiency as shown in the Table1.

#### Table1.Device Utilization summary

| D Partition Summary                           |      |           |             |  |  |  |  |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|--|--|--|--|

| No partition information was found.           |      |           |             |  |  |  |  |  |  |

|                                               |      |           |             |  |  |  |  |  |  |

| Device Utilization Summary (estimated values) |      |           |             |  |  |  |  |  |  |

| Logic Utilization                             | Used | Available | Utilization |  |  |  |  |  |  |

| Number of Slices                              | 368  | 4656      | 7%          |  |  |  |  |  |  |

| Number of Slice Flip Flops                    | 585  | 9312      | 6%          |  |  |  |  |  |  |

| Number of 4 input LUTs                        | 319  | 9312      | 3%          |  |  |  |  |  |  |

| Number of bonded IOBs                         | 67   | 190       | 35%         |  |  |  |  |  |  |

| Number of MULT18X18SIOs                       | 16   | 20        | 80%         |  |  |  |  |  |  |

| Number of GCLKs                               | 1    | 24        | 4%          |  |  |  |  |  |  |

The experimental set up for Implementation of Adaptive Noise Canceller is shown in figure 8. The experimental set up is done using FPGA SPARTAN 3E kit along with Computer loaded with Xilinx System Generator Software as shown in figure 8.

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

Figure 8.Experimental set up for Implementation of Adaptive Noise Canceller

#### VII. CONCLUSION

The implementation of Adaptive Noise Canceller using VHDL for a non-stationary environment is presented and the word length requirement for the design has also been discussed. The performance of the Adaptive Noise Canceller in a non-stationary environment is expressed by its simplicity to implement and its stability when the step size parameter is selected appropriately by proven results.

#### REFERENCES

[1] J.Jebastine & Dr.B.Sheela Rani(2012),"Design and Implementation of Noise free Audi speech signal using fast block Least Mean Square Algorithm", Signal and Image Processing: An International Journal (SIPIJ) Vol:3.

[2] N.Herve, D.Menard & O.Sentieys(2005),"Data word length optimization for FPGA synthesis", Proceedings of the IEEE International workshop on Signal processing systems, SIPS'05, Athens, Greece.

- Yaghoub & Mollaei(2009), "Hardware Implementation of Adative filters: Publishing: Proceeding of 2009 student conference on Research and Development(SCOReD 2009), 16-18.

- [4] S.Haykin(2003)."Adative filter Theory,4<sup>th</sup> ed.,B.Y.Zheng,, Trans.Publishing House of Electronics Industry,Beijing,pp.183-230.

- [5] R.H.Kwong & E.W.Johnston(1992),"A Variable step size LMS algorithm".IEEE transactions on Signal processing, Vol.40, No.7, pp.1636-1642.

- [6] Special Issue on Adaptive fitering (1984), IEEE Trans. Inform. Theory, Vol. IT-30.

- [7] Special Issue on Adaptive systems and applications(1987), IEEE Trans. Circuits Sysf.vol.CAS-34.

- [8] Shantala.S & S.Y.Kulkarni(2009),"High speed and Low power FPGA implementation of FIR filter for DSP applications"Europeon Journal of Scientific Research, vol.31, no.1, pp.19-28.

- [9] U.Meyer-Baese, DSP with FPGAs , Second Edition, Springer.

- [10] Dusan.M.Kodek,(1980)."Design of optimal finite word length FIR Digital filters using Inter programming techniques" IEEE Transactions on Acoustic,Speech and signal processing,vol.ASSP-28,no.3.

[11] WongYong Sung & Ki-II Kum(1995),"Simulation based word length optimization method for fixed-point Digital signal processing systems", IEEE Transitions on Signal Processing, vol.43, No.12.

[12] X.Hu,L.S.DeBrunner and V.DeBrunner(2002),"An efficient design for FIR filters with Variable precision", IEEE International Symposium on Circuits and Systems, pp.365-368, vol 4.

[13] Russel Tessier & Wayne Burleson(2001),"Reconfigurable Computing for Digital signal processing: A survey", Journal of VLSI signal processing 28, pp 7-27.

[14] Jafar Ramadhan Mohammed, Muhammed Safder Shafi Sahar Imtiaz, Rafay Iqbal Ansari & Mansoor Khan(2012), "An efficient Adaptive Noise Cancellation Scheme using ALE and NLMS Filters", International Journal of Electrical and Computer Engineering(IJECE), vol.2, No.3, pp.325-

332.

[15] A.Elhossini,S.Areibi & R.Don(2006),"An FPGA implementation of the LMS Adaptive filter for audio processing",Proceedings of IEEE International conference on Reconfigurable Computing and FPGAs,pp1-8.

[16] A.Y.Lin,K.S.Gugel &J.C.Principe(2003)."Feasibility of fixed-point transversal adaptive filters in FPGA devices with embedded DSP

blocks", Proceedings of the 3 rd IEEE International Workshop on System-on-Chip for Real- Time Applications pp.157-160.

[17] G.Yecai,H.Longqing & Z.Yanping.(2007)"Design and Implementation of adaptive Equalizer based on FPGA", In Proceedings of IEEE 8<sup>th</sup> International conference on Electronic Measurements and Instruments, pp.4-790-4-794.

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

[18] M.Vella & C.J.Debono(2006),"Implementation of a high speed adaptive FIR filter on a FPGA", In Proceedings of IEEE International Conf. ,pp.113-116.

[19] W.C.Chew & B.FarhangBoroujeny(1999),"FPGA Implementation of Acoustic Echo Cancelling", In Proceedings of IEEE region 10 Conference(TENCON'99),pp.263-266.

[20] Xilinx,"Spartan-3E FPGA Family Complete Data Sheet",Xilinx,Inc.,2009.

### BIOGRAPHY

S.THILAGAM graduated from Government College of Technology, Coimbatore, affiliated to Anna University in M.E-VLSI Design. She is an Assistant Professor in the Department of Electronics & Communication Engineering in Kumaraguru College of Technology, Coimbatore. She has a wide academic and teaching experience of eight years. Her area of interest in Research is VLSI Signal Processing.