(An ISO 3297: 2007 Certified Organization) Vol. 2, Issue 12, December 2013

# Comparison of PWM Methods for Multilevel Inverter

C.Gomathi<sup>1</sup>, Navyanagath<sup>2</sup>, S.V.Purnima<sup>3</sup> S.Veerakumar<sup>4</sup>

PG Scholar, Dept.of EEE, Bannari Amman Institute of Technology, Sathyamangalam Tamilnadu, India<sup>1</sup> PG Scholar, Dept.of EEE, Bannari Amman Institute of Technology, Sathyamangalam Tamilnadu, India<sup>2</sup>

PG Scholar, Dept.of EEE, Bannari Amman Institute of Technology, Sathyamangalam Tamilnadu, India<sup>3</sup>

Asst. Prof. (Sr.G), Dept.of EEE, Bannari Amman Institute of Technology, Sathyamangalam, Tamilnadu, India<sup>4</sup>

**ABSTRACT-**This paper discussed the cascaded H-bridge five level inverter with PWM methods by sinusoidal pulse width modulation & space vector pulse width modulation.Multi level inverter is used to reduce the THD in the output wave form without decreasing the inverter power output. If the level of the inverter will be increased, the numbers of components are increased. So, the switching stress will be increased. The space vector pulse width modulation is better than the sinusoidal pulse width modulation, because of better DC utilization, low THD.Compared to modulating wave or sinusoidal wave with the carrier wave, the carrier based PWM schemes are used for multi level inverters. In that carrier based PWM schemes, the In phase Disposition method is good compared to other schemes. The MATLAB Simulink environment is used to simulate the results.

**Keywords-**Cascaded H-bridge multi level inverter, sinusoidal pulse width modulation, space vector pulse width modulation, in phase disposition method, MATLAB simulink.

#### **I.INTRODUCTION**

Multi level inverters have emerged recently as very important role in the area of high power and medium voltage applications. The multi level inverters are, (i) diode clamped multi level inverters (ii)flying capacitor multi level inverter(iii)cascaded H-bridge multi level inverter, the cascaded H-bridge multi level inverter have some disadvantages compared to other topologies, because it have the full H-bridges that improving the level of the voltages. Same numbers of components are sufficient for each level. In sinusoidal pulse width modulation, sine wave is compared with the carrier wave, the pulses are produced. Then that produces pulses given to the multi level inverters, in SVPWM modulating waves are compared with the carrier wave that produced pulses also given to the multi level inverters. Carrier based schemes are used for multi level inverters. Number of carriers are depends on the levels of the multi level inverters. For five level invertes four carriers are used. Simulation is done by MATLAB simulink model. Wave forms are taken by workspace model.

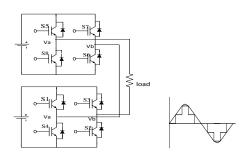

#### II.CASCADED H-BRIDGE MULTI LEVEL INVERTER

In this cascaded H-bridge multi level inverter, the cascaded full bridge with separate DC sources, number of devices are less used. Using of H- bridges including in this multilevel inverter increases the voltage level of the inverter. The fig 1 shows the five level cascaded H-bridge inverter. This having 8 switches, two DC sources and load. This requires less no of components, same amount of components are sufficient in every voltage level. For different voltage level the operation of switching sequence will be following in the table1, when the battery has  $2V_{dc}$  voltage. For zero voltage the S<sub>1</sub>, S<sub>3</sub>, S<sub>5</sub>, S<sub>7</sub>

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

switches get ON. For  $V_{dc}$  Voltage  $S_2 S_6 S_8 S_2$  switches will be ON. For  $2V_{dc}$  voltage  $S_1, S_6, S_5, S_2$  switches will be ON, For  $2V_{dc}$  voltage  $S_3, S_8, S_7, S_4$  switches will be ON, For  $-V_{dc}$  voltage  $S_3, S_7, S_5, S_4$  switches will be ON.

Fig1. Five level cascaded H-bridge inverter

| SI.NO | VOLTAGE<br>LEVEL  | OPERATING SWITCHES |

|-------|-------------------|--------------------|

| 1     | 0                 | S1 S3 S5 S7        |

| 2     | V <sub>dc</sub>   | S2 S6 S8 S2        |

| 3     | $2V_{dc}$         | S1 S6 S5 S2        |

| 4     | -2V <sub>dc</sub> | S3 S8 S7 S4        |

| 5     | -V <sub>dc</sub>  | S3 S7 S5 S4        |

Table 1: Operating Switches with Different Voltage Level

#### **III.PULSE WIDTH MODULATION**

#### A. Sinusoidal Pulse Width Modulation

In the sinusoidal pulse width modulation, the reference wave is the sine wave. That is compared with the carrier triangular wave, the pulses are produced. That is given to the inverter. The sine wave is greater than the carrier wave the top switches are ON. Otherwise the bottom switches are ON.

Fig 2 Comparisons of sine wave with ref wave Fig3 Generating pulse Fig4 Phase Shifted Multi Carrier Modulation

#### Carrier based PWM schemes

In carrier based PWM schemes the for m level (m-1) carrier waves are used, The carrier base PWM schemes are classified into two, they are,(i) Phase shifted multi carrier modulation,(ii) Level shifted multi carrier modulation The level shifted multi carrier modulation schemes are classified into three, they are,(i) In phase disposition method (ii)Alternative phase opposite disposition method and (iii) Phase opposite disposition method.

Phase Shifted Multi Carrier Modulation:

In the phase shifted multi carrier modulation, all triangular carrier wave are having same peak to peak voltage and same frequency but phase shift will be vary depends upon the level according to levels of the inverter by using the formula is,

$$\varphi_{cr} = \frac{360^0}{(m-1)}$$

Copyright to IJAREEIE

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

For five level inverter four carriers are used, these four carriers are having 90° phase shift that shown in fig (4), having four carrier waves for five level inverter. In that wave forms, from top to bottom the triangular waves are considered  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  Waves respectively that is compared with the reference wave. That produced pulses are given to the inverter.fig (1) shows the cascaded H-bridge five level inverter. The C1 wave pulse is given to the S5's gate,C2 wave pulse is given to the S1's gate, then the C3 wave pulse is given to the S7's gate and then the C4 wave pulse is given to the S3's gate of fig(1) inverter.

Level shifted multi carrier modulation:

Similar to phase shifted multi carrier modulation, In the level shifted modulation (m-1) carrier waves are used for m – levels. These triangular carrier also having same frequency and amplitude. These types of level shifted multi carrier modulation are explained below. In Phase Shifted Multicarrier modulation, all the carriers are in phase with each other. In Alternative Phase Opposite Disposition, All carriers are alternatively in opposite disposition. In Phase Opposite Disposition method, above the zero reference is in phase below the zero reference are opposite to the inphase.that wave forms are given as follows.

Fig5 In Phase Disposition Method Fig 6 Alternative Phase Opposite Disposition Fig 7 Phase Opposite Disposition

In fig (5), (6), (7) are having four carrier waves for five level inverter. In that wave forms, from top to bottom we considered  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  Waves respectively. That is compared with the reference wave. That produced pulses are given to the inverter.fig (1) shows the cascaded H-bridge five level inverter. The C1 wave pulse is given to the S5 switch's gate, C2 wave pulse is given to the S1 switch's gate, then the C3 wave pulse is given to the S3 switch's gate and then the C4 wave pulse is given to the S7 switch's gate of fig (1) inverter.

#### B. Space Vector Pulse Width Modulation

The SVPWM have the constant switching time calculations for each state. This SVPWM can easily be changed to higher levels.SVPWM have good utilization of the DC link voltage, low current ripple and relative easy hardware implementation. Compared to the SPWM, the SVPWM has a 15% higher utilization ratio of the voltage. As the number of level increases, the redundant switching states increases and also the complexity of selection of the switching states.

#### Reference Vector

The reference vector is represented in a  $\alpha\beta$ -plane. The switches being ON or OFF are determined by the location of the reference vector on this  $\alpha\beta$ -plane.

(An ISO 3297: 2007 Certified Organization) Vol. 2, Issue 12, December 2013

Fig 8 (a) Space Vector Diagram for 2 Phase Inverter,(b) Diagram of Reference Vector in abc and  $\alpha\beta$  axis

| εεε          |     |

|--------------|-----|

| Zero State   | 000 |

| Active State | 001 |

| Active State | 010 |

| Active State | 011 |

| Active State | 100 |

| Active State | 101 |

| Active State | 110 |

| Zero State   | 111 |

Table 2: Eight Switching States of the Inverter

The switches ON means 1, OFF means 0. The switches 1, 3, 5 are the upper switches and if these are 1 it turns the upper inverter leg ON and the terminal voltage ( $V_a$ ,  $V_b$ ,  $V_c$ ) is positive. If the upper switches are zero, then the terminal voltage is 0. The lower switches are complementary to the upper switches, so the only possible combinations are the switching states: 000, 001, 010, 011, 100, 110, 111. This means that there are 8 possible switching states, for which two of them are zero switching states and six of them are active switching states. These are represented by active (V1-V6) and zero (V0) vectors. The zero vectors are placed in the axis origin.

It is assumed that the three-phase system is balanced:

$$V_{a0} + V_{b0} + V_{c0} = 0 \tag{1}$$

These are the instantaneous phase voltages:

$$V_a = V\sin(\theta t) \tag{2}$$

$$V_b = \operatorname{Vsin}\left(\theta t + \frac{2\pi}{3}\right) \tag{3}$$

$$V_c = \operatorname{Vsin}\left(\theta t + \frac{4\pi}{3}\right) \tag{4}$$

When the three phase voltages are applied to a AC machine a rotating flux is created. This flux is represented as one rotating voltage vector. The magnitude and angle of this vector can be calculated with Clark's Transformation:

$$V_{ref} = V_{\alpha} + jV_{\beta} \tag{5}$$

The reference vector's magnitude and angle is:

$$\left|V_{ref}\right| = \sqrt{V_{\alpha}^{2} + V_{\beta}^{2}} \qquad \theta = \tan^{-1}\left(\frac{V_{\beta}}{V_{\alpha}}\right) \tag{6}$$

Copyright to IJAREEIE

(An ISO 3297: 2007 Certified Organization)

#### Vol. 2, Issue 12, December 2013

The reference voltage can then be expresses as:

$$V_{\alpha} + jV_{\beta} = \frac{2}{3} \left( V_{a} + e^{j\frac{2\pi}{3}} V_{b} + e^{-j\frac{2\pi}{3}} V_{c} \right)$$

(7)

The voltage vectors on the alpha and beta axis can then be described as:

$$\begin{pmatrix} V_{\alpha} \\ V_{\beta} \end{pmatrix} = \frac{2}{3} \begin{pmatrix} 1 & \cos\left(\frac{2\pi}{3}\right) & \cos\left(\frac{2\pi}{3}\right) \\ 0 & \sin\left(\frac{2\pi}{3}\right) & -\sin\left(\frac{2\pi}{3}\right) \end{pmatrix} \begin{pmatrix} V_{a} \\ V_{b} \\ V_{c} \end{pmatrix}$$

(8)

$$V_{\alpha} = \frac{2}{3} \left( V_{a} - \frac{1}{2} V_{b} - \frac{1}{2} V_{c} \right)$$

(10)

$$V_{\beta} = \frac{2}{3} \left( \frac{\sqrt{3}}{2} V_{b} - \frac{\sqrt{3}}{2} V_{c} \right)$$

(11)

Having calculated  $V_{\alpha}$ ,  $V_{\beta}$ ,  $V_{ref}$  and the reference angle, the first step is taken. The next step is to calculate the duration time for each vector V1-V6.

Time Duration

| NO | TIME DURATION T <sub>I</sub>                                                    | TIME DURATION T <sub>2</sub>                                                     |

|----|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1  | $T_1 = \frac{T_S}{V_{DC}} \left( V_\alpha - \frac{1}{\sqrt{3}} V_\beta \right)$ | $T_2 = \frac{T_S}{V_{DC}} \frac{2}{\sqrt{3}} V_\beta$                            |

| 2  | $T_1 = \frac{T_S}{V_{DC}} (V_\alpha + \frac{1}{\sqrt{3}} V_\beta)$              | $T_2 = \frac{T_S}{V_{DC}} \left( -V_\alpha + \frac{1}{\sqrt{3}} V_\beta \right)$ |

| 3  | $T_1 = \frac{T_S}{\sqrt{3}V_{DC}}(2V_\beta)$                                    | $T_2 = \frac{-T_S}{V_{DC}} (V_\alpha + \frac{1}{\sqrt{3}} V_\beta)$              |

| 4  | $T_1 = -\frac{T_S}{V_{DC}}(V_\alpha - \frac{1}{\sqrt{3}}V_\beta)$               | $T_2 = -\frac{T_S}{V_{DC}} \frac{2}{\sqrt{3}} V_\beta$                           |

| 5  | $T_1 = -\frac{T_S}{V_{DC}}(V_\alpha + \frac{1}{\sqrt{3}}V_\beta)$               | $T_2 = -\frac{T_S}{V_{DC}} \left(-V_\alpha + \frac{1}{\sqrt{3}}V_\beta\right)$   |

| 6  | $T_1 = -\frac{T_S}{\sqrt{3}V_{DC}}(2V_\beta)$                                   | $T_2 = \frac{T_S}{V_{DC}} (V_\alpha + \frac{1}{\sqrt{3}} V_\beta)$               |

Table3: Time Duration of Individual Sector

Table4: Switching Time of Individual Sector

| NO | T <sub>A</sub>                    | T <sub>B</sub>                   | T <sub>C</sub>                    |

|----|-----------------------------------|----------------------------------|-----------------------------------|

| 1  | $T_1 + T_2 + T_0/2$               | T <sub>0</sub> /2+T <sub>2</sub> | T <sub>0</sub> /2                 |

| 2  | T <sub>2</sub> +T <sub>0</sub> /2 | $T_1 + T_2 + T_0/2$              | T <sub>0</sub> /2                 |

| 3  | T <sub>0</sub> /2                 | $T_1 + T_2 + T_0/2$              | T <sub>2</sub> +T <sub>0</sub> /2 |

| 4  | T <sub>0</sub> /2                 | $T_2 + T_0/2$                    | $T_1+T_2+T_0/2$                   |

| 5  | $T_2 + T_0/2$                     | T <sub>0</sub> /2                | $T_1+T_2+T_0/2$                   |

| 6  | $T_1 + T_2 + T_0/2$               | T <sub>0</sub> /2                | T <sub>2</sub> +T <sub>0</sub> /2 |

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

| Along $\propto$ -axis: | $V_1 + V_2 \cos 60 T_2 = V_{ref} T_S \cos \theta$ | (12) |

|------------------------|---------------------------------------------------|------|

| Along $\beta$ -axis :  | $V_2 \sin 60 T_2 = V_{ref} T_S \sin \theta$       | (13) |

| Total time is,         | $T_S = T_1 + T_2 + T_0$                           | (14) |

Switching Time

Each sector having 7 switching states for each cycle. It starts and ends with a zero vector. The uneven numbers travel counter clockwise in each sector and the even sectors travel clockwise. The table3 shows the duty cycle of three phases that's are,  $T_A$ ,  $T_B$ , and  $T_C$  for six sectors.

#### **IV.SIMULATION RESULTS**

The following results are done by works space model using MATLAB Simulink. And comparison of SPWM & SVPWM in THD level is following below.

#### A. Sinusoidal PWM

In SPWM, carrier based scheme is used for compare the reference wave(sine wave) with carrier wave in five level cascaded H- bridge inverter.

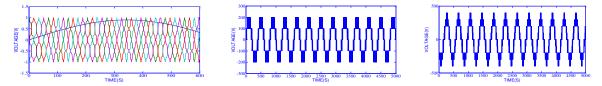

Phase Shifted Multi Carrier Modulation

The fig 9 shows the simulation results of cascaded 5 level H-bridge inverter using phase shifted modulation in SPWM.

Fig 9 Phase Shifted Multi Carrier Modulation, a) Comparison Wave b) Phase Voltage c) Line Voltage

Level Shifted Multi Carrier Modulation

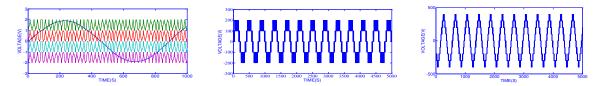

In Phase Disposition

Fig 10 In Phase Disposition Multi Carrier Modulation, a)Comparison Wave b)Phase Voltage c)Line Voltage

(An ISO 3297: 2007 Certified Organization) Vol. 2, Issue 12, December 2013

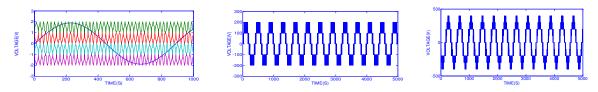

Alternative Phase Opposite Disposition

Fig 11 Alternative phase opposite disposition multi carrier modulation, a) comparison wave b) phase voltage c) line voltage Phase Opposite Disposition

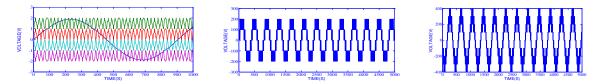

Fig 12 Phase opposite disposition multi carrier modulation, a) comparison wave b) phase voltage c) line voltage.

Fig 13 Phase Shifted Modulation, f=50HZ,Ph V=181.5,THD=31.68% Fig 14 IPD Modulation,f=50HZ,Ph V=194.4,THD=29.13%

Fig 15 APOD Modulation, f=50HZ, Ph V=178.1, THD=34.63% Fig 16 POD Modulation=50HZ, Ph V=177.8, THD=35.37%

From these figures the In Phase Disposition method of Multi Carrier Modulation is better than other. These have low THD and better voltage.

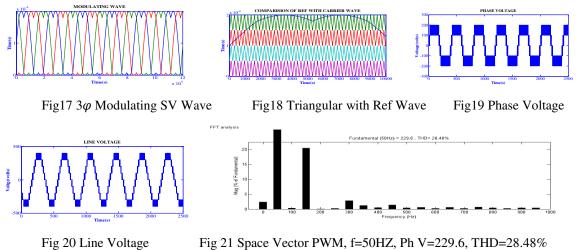

#### B. Space vector PWM

The SVPWM has advantages than the SPWM .In this IPD Multi Carrier Modulation is used. This modulating wave is compared with the carrier wave the pulses are produced. That is given to the inverters gates. The phase voltage &line voltage wave of cascaded H- bridge 5 level inverter is following below.

(An ISO 3297: 2007 Certified Organization)

### Vol. 2, Issue 12, December 2013

V.CONCLUSION

In this paper the comparison of SPWM &SVPWM with Cascaded H-bridge Five Level were discussed. And also discussed the types of multi carrier modulation. In that methods the in phase disposition method is better because of low THD (29.13%).then the space vector pulse width modulation having low THD (28.48%) compared to Sinusoidal Pulse Width Modulation.SVPWM have better DC utilization than SPWM.This simulation results were discussed using MATLAB simulink model.

#### ACKNOWLEDGEMENT

Author would like to thank Mr. S.Veerakumar for their support in implementation of this project.

#### REFERENCES

- [1] Zhiguo Pan, Fang Zheng Peng, Keith A. Corzine, Victor R. Stefanovic, John M. (Mickey) Leuthen, and Slobodan Gataric, "Voltage Balancing Control of Diode-Clamped Multilevel Rectifier/Inverter Systems" IEEE Trans On Industry Applications, Vol. 41, No. 6, pp. 1698-1706, Nov/Dec 2005.

- [2] Robert Stala, "The Switch-Mode Flying-Capacitor DC-DC Converters with Improved Natural Balancing", IEEE Trans. On Industrial Electronics, Vol. 57, No. 4, pp. 1369-1382, April 2010.

- [3] M. Trabelsi, and L. Ben-Brahim, "Development Of A Grid Connected Photovoltaic Power Conditioning System Based On Flying Capacitors Inverter", 8th International Multi-Conference on Systems, Signals & Devices, pp. 1-6, May 2011.

- [4] Pablo Lezana, José Rodriguez, and Diego A. Oyaizu, "Cascaded Multilevel Inverter with Regeneration Capability and Reduced Number of Switches", IEEE Trans. On Industrial Electronics, Vol. 55, No. 3, pp. 1059-1066, March 2008.

- [5] G.P. Adam, O. Anaya-Lara, G.M. Burt, D. Telford, B.W. Williams, and J.R. McDonald, "Modular multilevel inverter: pulse width modulation and capacitor balancing technique", Published in IET Power Electronics, Vol. 3, Iss. 5, pp. 702-715, 2010.

- [6] Moncef Ben Smida and Faouzi Ben Ammar, "Modeling and DBC-PSC-PWM Control of a Three-Phase Flying-Capacitor Stacked Multilevel Voltage Source Inverter", IEEE Trans. On Industrial Electronics, Vol. 57, No. 7, pp. 2231-2239, July 2010.

- [7] Mohan M. Renge and Hiralal M. Suryawanshi, "Three-Dimensional Space-Vector Modulation to Reduce Common-Mode Voltage for Multilevel Inverter", IEEE Trans. On Industrial Electronics, Vol. 57, No. 7, pp. 2324-2331, July 2010.

- [8] Ahmed M. Massoud, Shehab Ahmed, Prasad N. Enjeti, and Barry W. Williams, "Evaluation of a Multilevel Cascaded-Type Dynamic Voltage Restorer Employing Discontinuous Space Vector Modulation", IEEE Trans. on Industrial Electronics, Vol. 57, No7, pp.2398- 2410 July 2010.

- [9] Karthikeyan, R.,Dr.chenthur, pandian, s., "An algorithm for minimizing THD in multi level inverters with space vector modulation", IEEE Trans. on Industrial Electronics, Vol.3, NO.5, pp3915-3921, 2011

(An ISO 3297: 2007 Certified Organization) Vol. 2, Issue 12, December 2013

#### BIOGRAPHY

**C.Gomathi** received her BE Degree in Electrical & Electronics Engineering from Karpagam University, Coimbatore in May 2012. Currently she is pursuing her ME Degree in Power Electronics & Drives from Anna University, Chennai. Her research interest includes power electronics .She has published 1 paper in National Conference.

**Navya Nagath** received her BE Degree in Electrical & Electronics Engineering from sasurie college of engineering, vijayamangalam, in May 2012. Currently she is pursuing her ME Degree in Power Electronics & Drives from Anna University, Chennai.

**S.V.Purnima** received her BE Degree in Electrical & Electronics Engineering from Avinasilingam University, Coimbatore in May 2012. Currently she is pursuing her ME Degree in Power Electronics & Drives from Anna University, Chennai. Her research interest includes power electronics .She has published 1 paper in National Conference.

**S.Veerakumar** received his M.E degree at VIT Deemed University, Vellore. in Power Electronics in 2006. He is currently pursuing His Ph.D. degree at Anna University, Coimbatore in Power electronics. He is presently working as Assistant Professor (Sr.G) in the department of Electrical & Electronics Engineering, Bannari Amman Institute of Technology, Sathyamangalam. He is having a total of 6.5 years of teaching experience in various engineering colleges. He has published 12 papers in International and National Conferences.